Chiplets đang thu hút được sự chú ý mới trên thị trường ô tô, nơi điện khí hóa ngày càng tăng và cạnh tranh gay gắt đang buộc các công ty phải đẩy nhanh tiến độ thiết kế và sản xuất.

Điện khí hóa đã châm ngòi cho một số nhà sản xuất ô tô lớn nhất và nổi tiếng nhất, vốn đang phải vật lộn để duy trì tính cạnh tranh khi đối mặt với thời gian thị trường rất ngắn và yêu cầu liên tục thay đổi. Không giống như trước đây, khi các nhà sản xuất ô tô thường thực hiện chu kỳ thiết kế từ 5 đến 7 năm, công nghệ mới nhất trên ô tô ngày nay có thể được coi là lỗi thời trong vòng vài năm. Và nếu họ không thể theo kịp, sẽ có một loạt công ty khởi nghiệp mới sản xuất xe giá rẻ có khả năng cập nhật hoặc thay đổi tính năng nhanh chóng như cập nhật phần mềm.

Nhưng phần mềm có những hạn chế về tốc độ, bảo mật và độ tin cậy, đồng thời khả năng tùy chỉnh phần cứng là điều mà nhiều nhà sản xuất ô tô hiện đang nỗ lực. Đây là nơi các chiplets phù hợp và trọng tâm hiện nay là làm thế nào để xây dựng đủ khả năng tương tác trên các hệ sinh thái lớn để biến đây thành thị trường plug-and-play. Các yếu tố chính giúp khả năng tương tác của chiplet ô tô bao gồm tiêu chuẩn hóa, công nghệ kết nối, giao thức truyền thông, quản lý năng lượng và nhiệt, bảo mật, thử nghiệm và cộng tác hệ sinh thái.

Tương tự như các ứng dụng phi ô tô ở cấp độ bo mạch, nhiều nỗ lực thiết kế đang tập trung vào phương pháp tiếp cận liên tục, điều này đang thúc đẩy một số cân nhắc và đánh đổi thiết kế mới. Ở cấp độ chip, các kết nối giữa các bộ xử lý, chip, bộ nhớ và I/O khác nhau đang trở nên phức tạp hơn do yêu cầu về hiệu suất thiết kế tăng lên, thúc đẩy một loạt các hoạt động tiêu chuẩn. Các loại kết nối và giao diện khác nhau đã được đề xuất để phục vụ các mục đích khác nhau, trong khi các loại kết nối và giao diện khác nhau đang nổi lên. con nhỏ các công nghệ dành cho các chức năng chuyên dụng - bộ xử lý, bộ nhớ và I/O, cùng một số công nghệ khác - đang thay đổi cách tiếp cận thiết kế chip.

David Fritz, phó chủ tịch hệ thống ảo và hybrid tại Siemens EDA, cho biết: “Các OEM ô tô nhận ra rằng để kiểm soát vận mệnh của chính mình, họ sẽ phải kiểm soát SoC của chính mình”. “Tuy nhiên, họ không hiểu EDA đã đi được bao xa kể từ khi họ còn học đại học vào năm 1982. Ngoài ra, họ tin rằng họ cần phải đi đến nút quy trình mới nhất, nơi một bộ mặt nạ sẽ có giá 100 triệu USD. Họ không thể mua được thứ đó. Họ cũng không có cơ hội tiếp cận nhân tài vì nguồn nhân tài khá ít. Cùng với tất cả những điều đó, các OEM nhận ra rằng để kiểm soát vận mệnh của mình, họ cần một công nghệ do người khác phát triển nhưng có thể được kết hợp tuy nhiên cần thiết để tạo ra một sản phẩm khác biệt độc đáo mà họ tin rằng sẽ phù hợp với tương lai đối với ít nhất một số ít. năm mô hình. Sau đó, nó trở nên khả thi về mặt kinh tế. Thứ duy nhất phù hợp với yêu cầu đó là chiplets.”

Chiplets có thể được tối ưu hóa cho các chức năng cụ thể, giúp các nhà sản xuất ô tô đáp ứng các yêu cầu về độ tin cậy, an toàn, bảo mật bằng công nghệ đã được chứng minh trên nhiều thiết kế xe. Ngoài ra, chúng có thể rút ngắn thời gian đưa sản phẩm ra thị trường và cuối cùng là giảm chi phí cho các tính năng và chức năng khác nhau.

Nhu cầu về chip đã tăng lên trong thập kỷ qua. Theo Allied Market Research, nhu cầu chip ô tô toàn cầu sẽ tăng từ 49.8 tỷ USD vào năm 2021 lên 121.3 tỷ USD vào năm 2031. Sự tăng trưởng đó sẽ thu hút nhiều đổi mới và đầu tư vào chip ô tô hơn nữa, và chiplets dự kiến sẽ được hưởng lợi lớn.

Tuy nhiên, thị trường dành cho chiplets sẽ cần thời gian để trưởng thành và có thể sẽ triển khai theo từng giai đoạn. Ban đầu, nhà cung cấp sẽ cung cấp các loại khuôn dập độc quyền khác nhau. Sau đó, các đối tác sẽ làm việc cùng nhau để cung cấp chiplet nhằm hỗ trợ lẫn nhau, như đã từng xảy ra với một số nhà cung cấp. Giai đoạn cuối cùng sẽ là các chiplet có khả năng tương tác phổ quát, được hỗ trợ bởi UCIe hoặc một số sơ đồ kết nối khác.

Đến giai đoạn cuối cùng sẽ là khó khăn nhất và nó sẽ đòi hỏi những thay đổi đáng kể. Để đảm bảo khả năng tương tác, các phần đủ lớn của hệ sinh thái ô tô và chuỗi cung ứng phải kết hợp với nhau, bao gồm các nhà phát triển phần cứng và phần mềm, xưởng đúc, OSAT và nhà cung cấp vật liệu và thiết bị.

Động lực đang được xây dựng

Về mặt tích cực, không phải tất cả những điều này đều bắt đầu từ đầu. Ở cấp độ bo mạch, các mô-đun và hệ thống con luôn sử dụng giao diện chip-to-chip trên bo mạch và chúng sẽ tiếp tục làm như vậy. Nhiều nhà cung cấp chip và IP khác nhau, bao gồm Cadence, Diode, Microchip, NXP, Renesas, Rambus, Infineon, Arm và Synopsys, cung cấp chip giao diện hoặc IP có sẵn để tạo silicon giao diện.

Hiệp hội Universal Chiplet Interconnect Express (UCIe) là động lực đằng sau tiêu chuẩn kết nối mở, cố định. Nhóm đã phát hành thông số kỹ thuật UCIe 1.1 mới nhất vào tháng 2023 năm XNUMX. Các thành viên hội đồng quản trị bao gồm Alibaba, AMD, Arm, ASE, Google Cloud, Intel, Meta, Microsoft, NVIDIA, Qualcomm, Samsung và những người khác. Các đối tác trong ngành đang thể hiện sự hỗ trợ rộng rãi. AIB và Bunch of Wires (BoW) cũng đã được đề xuất. Ngoài ra, Arm vừa phát hành Kiến trúc hệ thống Chiplet của riêng mình, cùng với thông số AMBA được cập nhật để chuẩn hóa các giao thức cho chiplet.

Arif Khan, giám đốc nhóm tiếp thị sản phẩm cấp cao về IP thiết kế tại Cadence cho biết: “Chiplets đã có mặt ở đây do nhu cầu thiết yếu. “Kích thước bộ xử lý và SoC ngày càng tăng đang đạt đến giới hạn đường kẻ ô và tính kinh tế của quy mô. Lợi ích gia tăng từ tiến bộ công nghệ quy trình thấp hơn so với chi phí ngày càng tăng trên mỗi bóng bán dẫn và thiết kế. Những tiến bộ trong công nghệ đóng gói (2.5D/3D) và tiêu chuẩn hóa giao diện ở cấp độ hoàn thiện, chẳng hạn như UCIe, sẽ tạo điều kiện thuận lợi cho việc phát triển chiplet.”

Gần như tất cả các chiplets được sử dụng ngày nay đều được phát triển nội bộ bởi các nhà sản xuất chip lớn như Intel, AMD và Marvell, vì họ có thể kiểm soát chặt chẽ các đặc tính và hoạt động của các chiplet đó. Nhưng có nhiều công việc đang được tiến hành ở mọi cấp độ để mở cửa thị trường này cho nhiều người chơi hơn. Khi điều đó xảy ra, các công ty nhỏ hơn có thể bắt đầu tận dụng những gì mà những người đi đầu đường mòn nổi tiếng đã đạt được cho đến nay và đổi mới xung quanh những phát triển đó.

Guillaume Boillet, giám đốc tiếp thị chiến lược cấp cao tại Arteris cho biết: “Nhiều người trong chúng tôi tin rằng giấc mơ có được danh mục chiplet có sẵn, có khả năng tương tác sẽ phải mất nhiều năm trước khi trở thành hiện thực”. đang giải quyết rủi ro về thông số kỹ thuật không đầy đủ.

Điều này cũng đang nâng cao sức hấp dẫn của FPGA và eFPGA, có thể cung cấp mức độ tùy chỉnh và cập nhật cho phần cứng trong lĩnh vực này. Geoff Tate, Giám đốc điều hành của Flex Logix cho biết: “Chiplets là có thật. “Ngay bây giờ, một công ty xây dựng hai chiplets trở lên có thể hoạt động kinh tế hơn nhiều so với một công ty xây dựng khuôn có kích thước gần như hình kẻ ô mà hầu như không có năng suất. Việc tiêu chuẩn hóa chiplet dường như vẫn còn rất xa vời. Ngay cả UCIe cũng chưa phải là một tiêu chuẩn cố định. Không phải tất cả đều đồng ý về UCIe, thử nghiệm khuôn mẫu và ai là người gây ra sự cố khi gói tích hợp không hoạt động, v.v. Chúng tôi có một số khách hàng sử dụng hoặc đang đánh giá eFPGA cho các giao diện có tiêu chuẩn thay đổi liên tục như UCIe. Họ có thể triển khai silicon ngay bây giờ và sử dụng eFPGA để tuân thủ các thay đổi tiêu chuẩn sau này.”

Cũng có những nỗ lực khác để hỗ trợ các chiplets, mặc dù vì những lý do hơi khác nhau - đáng chú ý là chi phí mở rộng quy mô thiết bị ngày càng tăng và nhu cầu kết hợp nhiều tính năng hơn vào chip, vốn bị hạn chế về mặt kẻ ô ở các nút tiên tiến nhất. Nhưng những nỗ lực đó cũng mở đường cho các chiplet trong ô tô và có sự hỗ trợ mạnh mẽ của ngành để biến tất cả những điều này thành hiện thực. Ví dụ: dưới sự tài trợ của SEMI, ASME và ba Hiệp hội IEEE, Lộ trình tích hợp không đồng nhất (HIR) mới xem xét các vấn đề về thiết kế, vật liệu và đóng gói vi điện tử khác nhau để đưa ra lộ trình cho ngành bán dẫn. Trọng tâm hiện tại của họ bao gồm 2.5D, 3D-IC, đóng gói ở cấp độ wafer, quang tử tích hợp, MEMS và cảm biến cũng như hệ thống trong gói (SiP), hàng không vũ trụ, ô tô, v.v.

Tại Hội nghị thượng đỉnh toàn cầu về tích hợp không đồng nhất 2023 vừa qua, đại diện của AMD, Ứng dụng Vật liệu, ASE, Lam Research, MediaTek, Micron, Onto Innovation, TSMCvà những người khác đã thể hiện sự ủng hộ mạnh mẽ đối với chiplets. Một nhóm khác hỗ trợ chiplets là Trao đổi thiết kế Chiplet (CDX) nhóm làm việc, là một phần của Kiến trúc cụ thể của miền mở (ODSA) và Quỹ Dự án Điện toán Mở (OCP). Điều lệ Trao đổi thiết kế Chiplet (CDX) tập trung vào các đặc điểm khác nhau của tích hợp chiplet và chiplet, bao gồm các tiêu chuẩn trao đổi thiết kế điện, cơ và nhiệt của Mạch tích hợp 2.5D (3D-IC) xếp chồng 3D. Đại diện của nó bao gồm Ansys, Vật liệu ứng dụng, Arm, Ayar Labs, Broadcom, Cadence, Intel, Macom, Marvell, Microsemi, NXP, Siemens EDA, Synopsys, và những người khác.

Fritz của Siemens lưu ý: “Những điều mà các công ty ô tô mong muốn về chức năng của mỗi chiplet vẫn đang ở trạng thái biến động”. “Một thái cực có những vấn đề này, thái cực kia có những vấn đề đó. Đây là điểm ngọt ngào. Đây là những gì cần thiết. Và đây là những loại công ty có thể hoạt động và thực hiện loại công việc đó, sau đó bạn có thể tập hợp chúng lại với nhau. Sau đó, khả năng tương tác này không phải là một vấn đề lớn. OEM có thể khiến vấn đề trở nên quá phức tạp bằng cách nói: 'Tôi phải xử lý toàn bộ các khả năng đó.' Giải pháp thay thế là họ có thể nói, 'Nó giống như một PCIe tốc độ cao. Nếu tôi muốn giao tiếp từ người này sang người khác, tôi đã biết cách thực hiện điều đó. Tôi có trình điều khiển đang chạy hệ điều hành của mình. Điều đó sẽ giải quyết được rất nhiều vấn đề và tôi tin rằng mọi chuyện sẽ kết thúc ở đó.”

Một con đường để phát triển chiplet phổ quát?

Trong tương lai, các chiplet là tâm điểm của cả ngành công nghiệp ô tô và chip, và điều đó sẽ liên quan đến mọi thứ từ IP chiplet đến các kết nối bộ nhớ cũng như các tùy chọn và hạn chế tùy chỉnh.

Ví dụ: Renesas Electronics đã công bố kế hoạch vào tháng 2023 năm XNUMX cho các SoC và MCU thế hệ tiếp theo của mình. Công ty đang nhắm mục tiêu tất cả các ứng dụng chính trong lĩnh vực kỹ thuật số ô tô, bao gồm thông tin nâng cao về R-Car SoC thế hệ thứ năm dành cho các ứng dụng hiệu suất cao với công nghệ tích hợp chiplet trong gói tiên tiến, nhằm giúp các kỹ sư ô tô linh hoạt hơn trong việc tùy chỉnh. thiết kế của họ.

Renesas lưu ý rằng nếu cần nhiều hiệu suất AI hơn trong Hệ thống hỗ trợ người lái nâng cao (ADAS), các kỹ sư sẽ có khả năng tích hợp bộ tăng tốc AI vào một con chip duy nhất. Công ty cho biết lộ trình này được đưa ra sau nhiều năm cộng tác và thảo luận với các khách hàng Cấp 1 và OEM, những khách hàng đang kêu gọi tìm cách tăng tốc phát triển mà không ảnh hưởng đến chất lượng, bao gồm cả việc thiết kế và xác minh phần mềm ngay cả trước khi có phần cứng.

“Do nhu cầu ngày càng tăng về khả năng tính toán theo yêu cầu và nhu cầu về mức độ tự chủ ngày càng cao trên ô tô của ngày mai, chúng tôi nhận thấy những thách thức trong việc mở rộng quy mô các giải pháp nguyên khối và đáp ứng nhu cầu hiệu suất của thị trường trong những năm tới,” cho biết Vasanth Waran, giám đốc cấp cao về Chiến lược & Kinh doanh SoC tại Renesas. “Chiplets cho phép các giải pháp điện toán mở rộng quy mô vượt xa nhu cầu của thị trường.”

Renesas đã công bố kế hoạch thành lập một dòng sản phẩm dựa trên chiplet nhắm mục tiêu cụ thể vào thị trường ô tô bắt đầu từ năm 2025.

Giao diện tiêu chuẩn cho phép tùy chỉnh SoC

Không hoàn toàn rõ ràng sẽ có bao nhiêu sự chồng chéo giữa các bộ xử lý tiêu chuẩn, nơi hầu hết các chiplets được sử dụng ngày nay và các chiplet được phát triển cho các ứng dụng ô tô. Nhưng các công nghệ cơ bản và sự phát triển chắc chắn sẽ hỗ trợ lẫn nhau khi công nghệ này chuyển sang các thị trường mới.

David Ridgeway, giám đốc sản phẩm cấp cao, nhóm giải pháp tăng tốc IP tại Synopsys, lưu ý: “Cho dù đó là máy tăng tốc AI hay ứng dụng ô tô ADAS, khách hàng đều cần các khối IP giao diện tiêu chuẩn”. “Điều quan trọng là phải cung cấp các hệ thống con IP được xác minh đầy đủ xung quanh các yêu cầu tùy chỉnh IP của chúng để hỗ trợ các thành phần hệ thống con được sử dụng trong SoC của khách hàng. Khi tôi nói đến khả năng tùy chỉnh, bạn có thể không nhận ra IP có thể tùy chỉnh đã trở nên như thế nào trong suốt 10 đến 20 năm qua, về phía PHY cũng như phía bộ điều khiển. Ví dụ: PCI Express đã chuyển từ PCIe Gen 3 sang Gen 4 rồi Gen 5 và bây giờ là Gen 6. Bộ điều khiển có thể được cấu hình để hỗ trợ nhiều chế độ phân nhánh có độ rộng liên kết nhỏ hơn, bao gồm một x16, hai x8 hoặc bốn x4. Nhóm IP hệ thống con của chúng tôi làm việc với khách hàng để đảm bảo đáp ứng tất cả các yêu cầu tùy chỉnh. Đối với các ứng dụng AI, tính toàn vẹn của tín hiệu và nguồn điện là cực kỳ quan trọng để đáp ứng các yêu cầu về hiệu suất của chúng. Hầu như tất cả khách hàng của chúng tôi đang tìm cách đẩy giới hạn đạt được tốc độ băng thông bộ nhớ cao nhất có thể để TPU của họ có thể xử lý nhiều giao dịch hơn mỗi giây. Bất cứ khi nào ứng dụng là điện toán đám mây hay trí tuệ nhân tạo, khách hàng đều muốn tốc độ phản hồi nhanh nhất có thể được.”

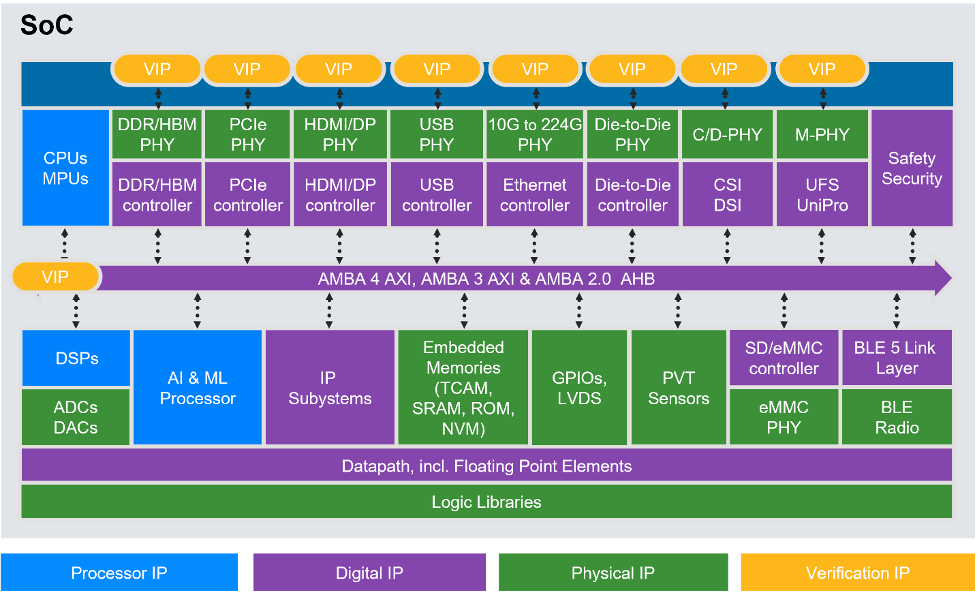

Hình 1: Các khối IP bao gồm bộ xử lý, kỹ thuật số, PHY và xác minh giúp các nhà phát triển triển khai toàn bộ SoC. Nguồn: Tóm tắt

Tối ưu hóa PPA phục vụ mục tiêu cuối cùng là tăng hiệu quả và điều này làm cho các chiplet trở nên đặc biệt hấp dẫn trong các ứng dụng ô tô. Khi UCIe trưởng thành, dự kiến nó sẽ cải thiện hiệu suất tổng thể theo cấp số nhân. Ví dụ: UCIe có thể cung cấp băng thông bờ biển từ 28 đến 224 GB/s/mm trong gói tiêu chuẩn và 165 đến 1317 GB/s/mm trong gói nâng cao. Điều này thể hiện sự cải thiện hiệu suất từ 20 đến 100 lần. Việc giảm độ trễ từ 20ns xuống 2ns thể hiện sự cải thiện gấp 10 lần. Hiệu suất năng lượng cao hơn khoảng 10 lần, ở mức 0.5 pJ/b (gói tiêu chuẩn) và 0.25 pJ/b (gói nâng cao), là một điểm cộng nữa. Điều quan trọng là rút ngắn khoảng cách giao diện bất cứ khi nào có thể.

Để tối ưu hóa thiết kế chiplet, UCIe Consortium đưa ra một số gợi ý:

- Xem xét lập kế hoạch cẩn thận các đường cắt kiến trúc (tức là ranh giới chiplet), tối ưu hóa năng lượng, độ trễ, diện tích silicon và tái sử dụng IP. Ví dụ: việc tùy chỉnh một chiplet cần nút xử lý tiên tiến nhất trong khi sử dụng lại các chiplet khác trên các nút cũ hơn có thể ảnh hưởng đến chi phí và thời gian.

- Các hạn chế về đóng gói về nhiệt và cơ học cần phải được lên kế hoạch cho các đường bao nhiệt của gói, các điểm nóng, vị trí của chiplet cũng như định tuyến và đột phá I/O.

- Các nút quy trình cần phải được lựa chọn cẩn thận, đặc biệt trong bối cảnh sơ đồ phân phối điện liên quan.

- Chiến lược thử nghiệm cho các chiplet và các bộ phận được đóng gói/lắp ráp cần phải được phát triển từ trước để đảm bảo các vấn đề về silicon được phát hiện ở giai đoạn thử nghiệm ở cấp độ chiplet thay vì sau khi chúng được lắp ráp thành một gói.

Kết luận

Ý tưởng tiêu chuẩn hóa các giao diện cố định đang nhanh chóng được triển khai nhưng con đường đạt được điều đó sẽ cần thời gian, công sức và rất nhiều sự hợp tác giữa các công ty hiếm khi nói chuyện với nhau. Việc chế tạo một chiếc xe cần có sự quyết tâm của một nhà sản xuất ô tô. Việc chế tạo một phương tiện sử dụng chiplets đòi hỏi toàn bộ hệ sinh thái bao gồm các nhà phát triển, xưởng đúc, OSAT và nhà cung cấp vật liệu và thiết bị để làm việc cùng nhau.

Các OEM ô tô là những chuyên gia trong việc kết hợp các hệ thống lại với nhau và tìm ra những cách sáng tạo để cắt giảm chi phí. Nhưng vẫn còn phải xem họ có thể xây dựng và tận dụng hệ sinh thái gồm các chiplets có khả năng tương tác nhanh chóng và hiệu quả như thế nào để thu hẹp chu trình thiết kế, cải thiện khả năng tùy chỉnh và thích ứng với một thế giới mà công nghệ tiên tiến hàng đầu có thể đã lỗi thời vào thời điểm nó được thiết kế, thử nghiệm hoàn chỉnh. , và có sẵn cho người tiêu dùng.

- Ann Mutschler đã đóng góp cho báo cáo này.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/