Đối với Hội nghị chuyên đề chiến lược quốc tế SEMI năm 2024, tôi đã được các thành viên ban tổ chức thách thức xem xét logic sẽ ở đâu trong mười năm tới từ góc độ công nghệ, kinh tế và tính bền vững. Sau đây là phần thảo luận về bài trình bày của tôi.

Để hiểu logic, tôi tin rằng sẽ rất hữu ích nếu hiểu được điều gì tạo nên các thiết bị logic hàng đầu. TechInsights tạo ra các báo cáo phân tích dấu chân chi tiết và tôi đã lấy báo cáo cho mười thiết bị loại 7nm và 5nm bao gồm bộ vi xử lý Intel và AMD, bộ xử lý Apple A series và M series, GPU NVIDIA và các thiết bị khác. Hình 1 minh họa những gì tạo nên khu vực khuôn.

Từ hình 1, logic chiếm ít hơn một nửa diện tích khuôn, bộ nhớ ít hơn một phần ba khuôn và I/O, analog và phần cân bằng khác. Tôi thấy điều thú vị là diện tích bộ nhớ SRAM thực tế đo được nhỏ hơn rất nhiều so với tỷ lệ phần trăm mà tôi thường nghe mọi người nói về các sản phẩm System On a Chip (SOC). Biểu đồ ở phía dưới bên phải cho thấy có một ngoại lệ nhưng mặt khác các giá trị được phân cụm chặt chẽ.

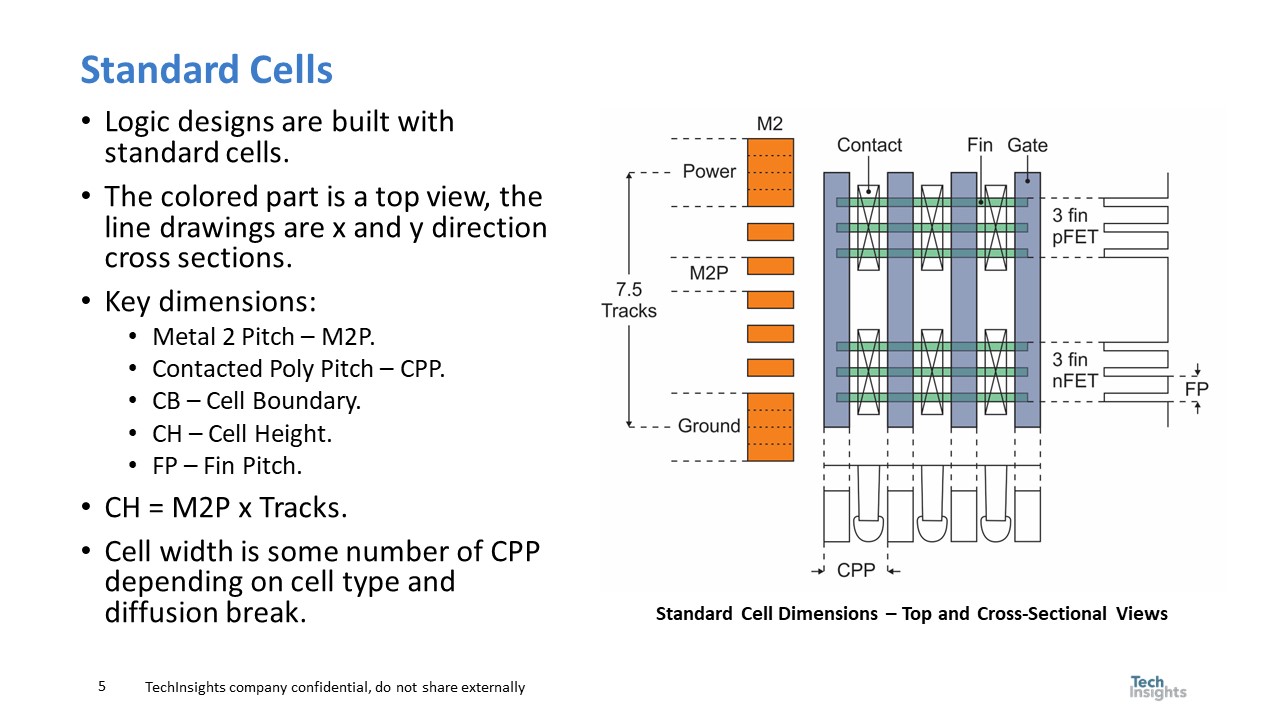

Logic đơn chiếm gần một nửa diện tích khuôn, nên bắt đầu với phần logic của thiết kế. Các thiết kế logic được thực hiện với các ô tiêu chuẩn và hình 2 là sơ đồ của một ô tiêu chuẩn.

Chiều cao của một ô tiêu chuẩn thường được đặc trưng bằng Metal 2 Pitch (M2P) nhân với số lượng rãnh, nhưng nhìn sang bên phải của hình sẽ có mặt cắt ngang của cấu trúc thiết bị cũng phải phù hợp với chiều cao của ô và bị hạn chế bởi vật lý của thiết bị. Điều tương tự cũng xảy ra với chiều rộng ô phụ thuộc vào Poly Pitch Liên hệ (CPP) và nhìn vào phần dưới của hình, có một mặt cắt ngang của cấu trúc thiết bị một lần nữa bị hạn chế bởi vật lý.

Hình 3 trình bày kết quả phân tích để xác định các giới hạn thực tế của tỷ lệ chiều rộng ô và chiều cao ô. Tôi có một bài trình bày nêu chi tiết các hạn chế về tỷ lệ và trong bài trình bày đó có hàng tá trang trình bày giữa hình 2 và hình 3, nhưng vì thời gian có hạn nên tôi chỉ có thể đưa ra kết luận.

Tỷ lệ chiều rộng ô phụ thuộc vào CPP và phía bên trái của hình minh họa cách CPP được tạo thành từ Chiều dài cổng (Lg), Chiều rộng tiếp điểm (Wc) và hai Độ dày miếng đệm tiếp xúc với cổng (Tsp). Lg bị hạn chế bởi rò rỉ và Lg tối thiểu với rò rỉ chấp nhận được tùy thuộc vào loại thiết bị. Các thiết bị phẳng có một cổng duy nhất điều khiển bề mặt của kênh có độ dày không giới hạn, được giới hạn ở khoảng 30nm. FinFET và Nanosheets ngang (HNS) giới hạn độ dày kênh (~5nm) và có 3 và 4 cổng tương ứng. Cuối cùng, vật liệu 2D có độ dày kênh <1nm, vật liệu không chứa silicon và có thể tạo ra Lg xuống ~5nm. Cả Wc và Tsp đều có khả năng mở rộng quy mô hạn chế do ký sinh. Điểm mấu chốt là thiết bị 2D có thể tạo ra CPP ~ 30nm so với CPP ngày nay là ~ 50nm.

Tỷ lệ chiều cao ô được minh họa ở phía bên phải của hình. HNS cung cấp các ngăn xếp tấm nano đơn thay cho nhiều vây. Sau đó, quá trình phát triển thành các thiết bị xếp chồng có CFET sẽ loại bỏ khoảng cách np theo chiều ngang và xếp chồng nFet và pFET. Chiều cao tế bào hiện tại là 150nm đến 200nm có thể giảm xuống ~ 50nm.

Sự kết hợp giữa CPP và chia tỷ lệ Chiều cao ô có thể tạo ra mật độ bóng bán dẫn ~ 1,500 triệu bóng bán dẫn trên mỗi milimet bình phương (MTx/mm2) so với ngày nay <300MTx/mm2. Cần lưu ý rằng vật liệu 2D có khả năng là công nghệ từ giữa đến cuối năm 2030 nên 1,500 MTx/mm2 nằm ngoài thời gian được thảo luận ở đây.

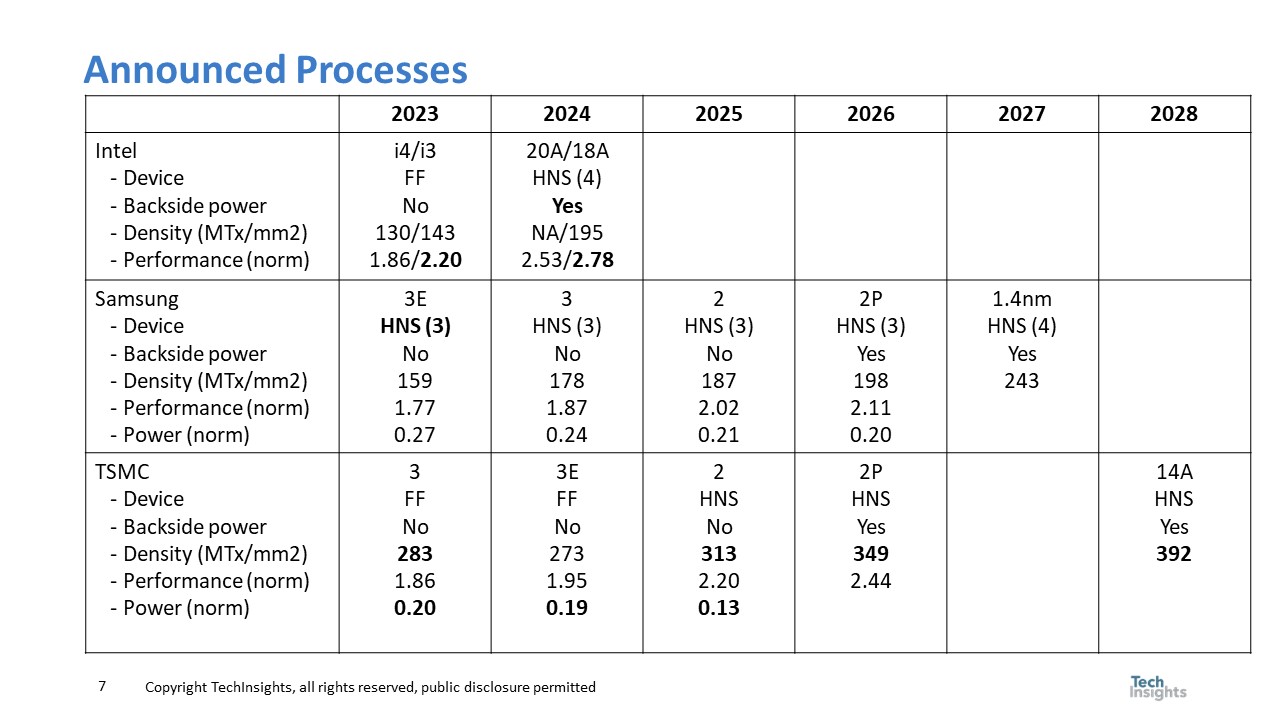

Hình 4 trình bày tóm tắt các quy trình đã được công bố của Intel, Samsung và TSMC.

Đối với mỗi công ty và năm, loại thiết bị, có sử dụng nguồn điện phía sau hay không, mật độ, công suất và hiệu suất sẽ được hiển thị nếu có. Sức mạnh và hiệu suất là những thước đo tương đối và sức mạnh không có sẵn cho Intel.

Trong hình 4, những đổi mới về công nghệ và hiệu suất hàng đầu được in đậm. Samsung là hãng đầu tiên đưa HNS vào sản xuất vào năm 2023, trong đó Intel sẽ không giới thiệu HNS cho đến năm 2024 và TSMC cho đến năm 2025. Intel là hãng đầu tiên đưa nguồn điện mặt sau vào sản xuất vào năm 2024 còn Samsung và TSMC sẽ không giới thiệu nó cho đến năm 2026.

Phân tích của tôi kết luận Intel là công ty dẫn đầu về hiệu suất với i3 và duy trì trạng thái đó trong khoảng thời gian được minh họa, TSMC dẫn đầu về sức mạnh (không có dữ liệu Intel) và dẫn đầu về mật độ.

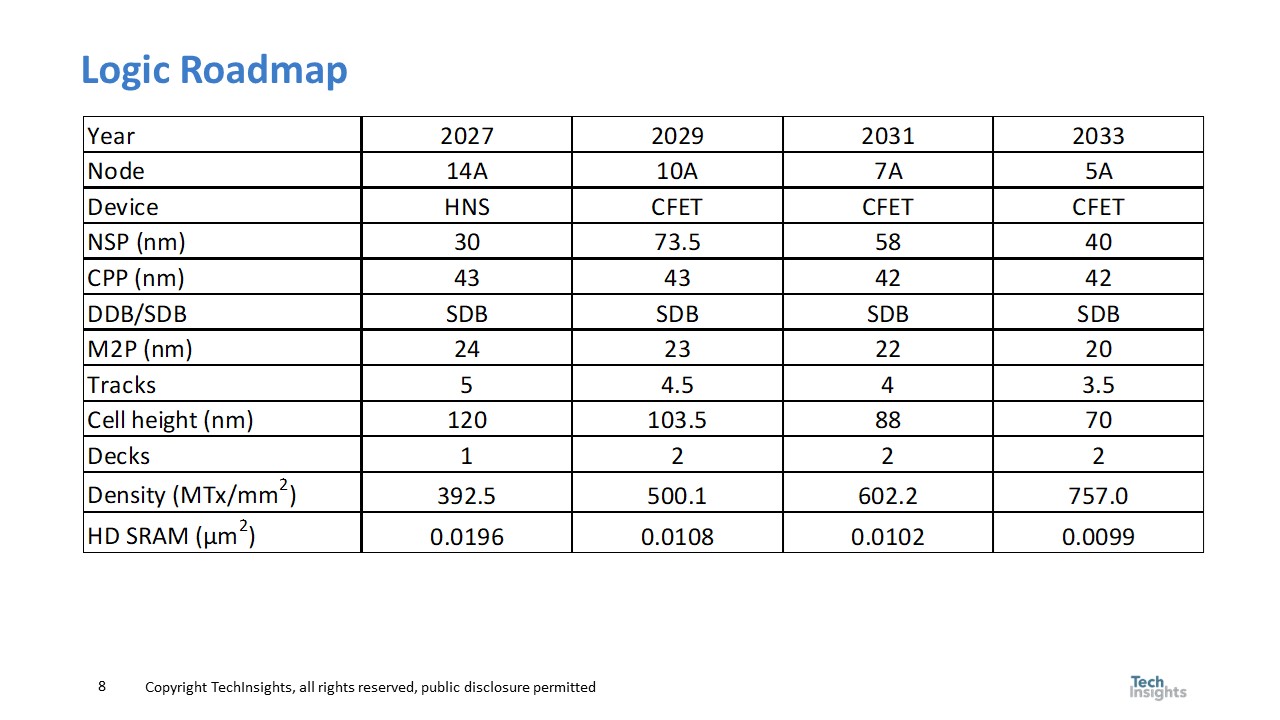

Hình 5 trình bày lộ trình logic của chúng tôi và bao gồm các kích thước ô SRAM dự kiến (sẽ nói thêm về điều này sau).

Từ hình 5, chúng tôi kỳ vọng CFET sẽ được giới thiệu vào khoảng năm 2029 giúp tăng mật độ logic và cũng cắt giảm gần một nửa kích thước ô SRAM (việc chia tỷ lệ kích thước ô SRAM hầu như đã dừng ở cạnh đầu). Chúng tôi kỳ vọng mật độ logic sẽ đạt ~757MTx/mm2 bởi 2034.

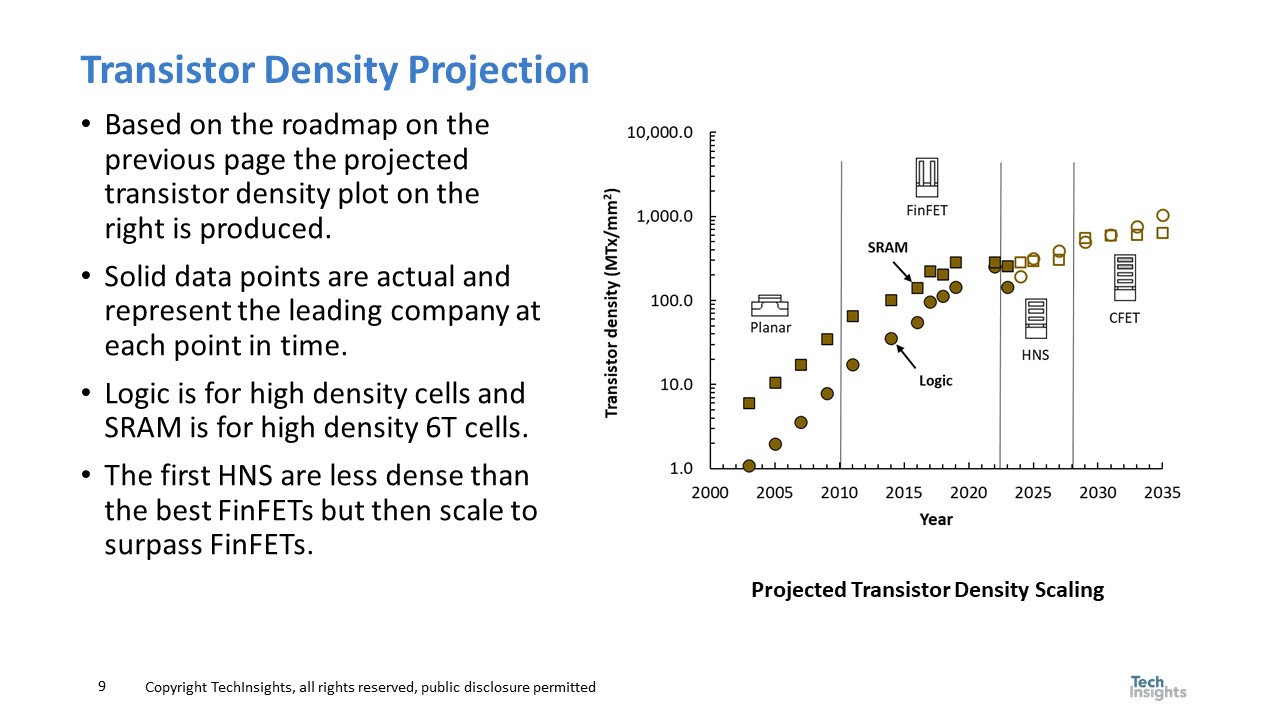

Cả phép chiếu mật độ bóng bán dẫn logic và phép chiếu mật độ bóng bán dẫn SRAM đều được minh họa trong hình 6.

Cả việc chia tỷ lệ mật độ bóng bán dẫn logic và SRAM đều chậm lại nhưng SRAM ở mức độ lớn hơn và logic hiện có mật độ bóng bán dẫn tương tự như SRAM.

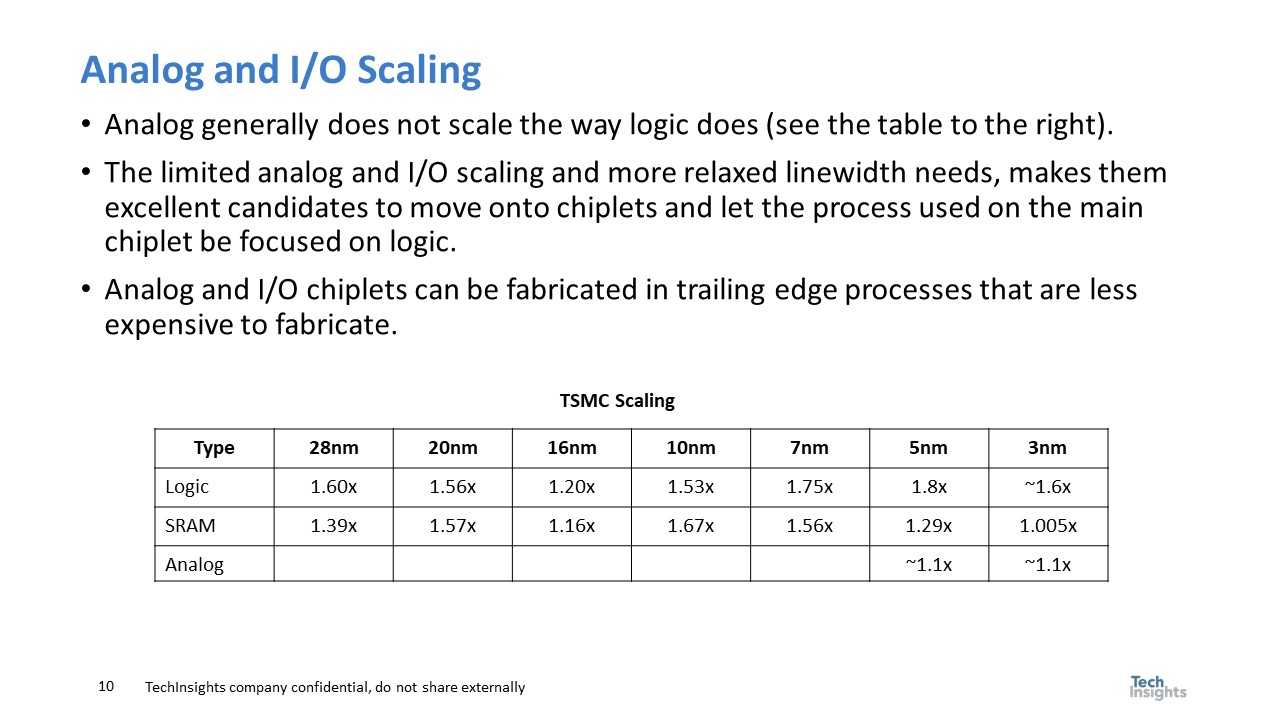

Trang trình bày 7 tóm tắt dữ liệu TSMC về tỷ lệ tương tự so với Logic và SRAM. Việc chia tỷ lệ tương tự và I/O đều chậm hơn so với tỷ lệ logic.

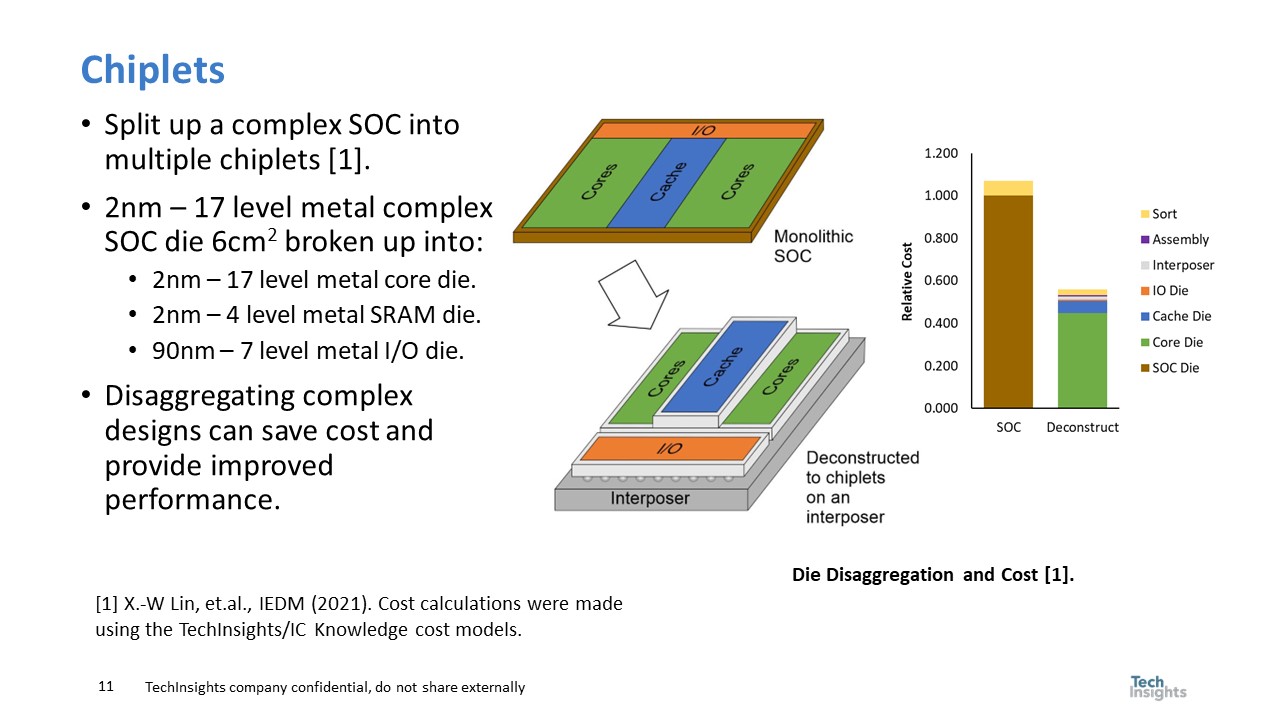

Một giải pháp khả thi để giảm tốc độ SRAM, analog và I/O là chiplets. Chiplets có thể cho phép sử dụng các quy trình ít tốn kém hơn – được tối ưu hóa hơn để tạo SRAM và I/O.

Hình bên phải của hình 8 lấy từ một bài báo năm 2021 mà tôi đồng tác giả với Synopsys. Kết luận của chúng tôi là việc chia một SOC lớn thành các con nhỏ có thể cắt giảm một nửa chi phí ngay cả sau khi tính đến chi phí đóng gói/lắp ráp tăng lên.

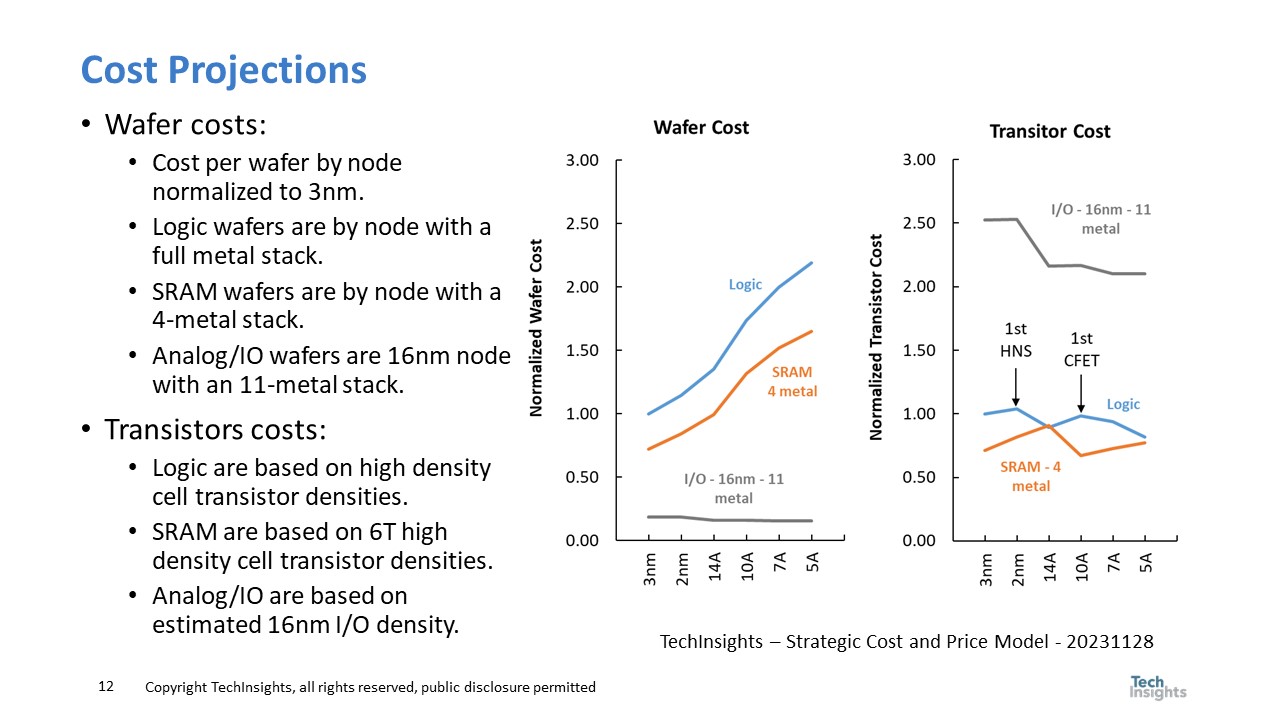

Hình 9 trình bày chi phí wafer và bóng bán dẫn đã chuẩn hóa cho logic, SRAM và I/O (xin lưu ý rằng hình đã được cập nhật từ bản trình bày ban đầu).

Trong hình bên phải, chi phí wafer chuẩn hóa được hiển thị. Chi phí wafer logic dành cho một ngăn xếp kim loại đầy đủ ngày càng tăng về số lượng lớp kim loại. Các tấm wafer SRAM là các nút giống nhau nhưng bị giới hạn ở 4 lớp kim loại do SRAM bố trí đều đặn hơn. Chi phí wafer I/O dựa trên quy trình kim loại 16nm – 11. Tôi đã chọn 16nm để có được nút FinFET với chi phí tối thiểu nhằm đảm bảo hiệu suất I/O đầy đủ.

Hình bên phải là chi phí wafer được chuyển đổi thành chi phí bóng bán dẫn. Điều thú vị là bóng bán dẫn I/O lớn đến mức ngay cả trên tấm bán dẫn 16nm chi phí thấp, chúng vẫn có chi phí cao nhất (kích thước bóng bán dẫn I/O dựa trên các phép đo của TechInsights về bóng bán dẫn I/O thực tế). Chi phí bóng bán dẫn logic tăng lên ở mức 2nm ở nút bảng TSMC HNS đầu tiên có mức thu nhỏ ở mức khiêm tốn. Chúng tôi hy vọng mức thu hẹp ở mức 14A sẽ lớn hơn đối với nút HNS thế hệ thứ hai (điều này tương tự như những gì TSMC đã làm với nút FinFET đầu tiên của họ). Một lần nữa, chi phí của nút CFET đầu tiên cũng làm tăng chi phí bóng bán dẫn cho một nút. Chi phí bóng bán dẫn SRAM có xu hướng tăng lên do độ co rút hạn chế ngoại trừ việc thu nhỏ CFET một lần. Điểm mấu chốt của phân tích này là việc giảm chi phí bóng bán dẫn sẽ ở mức khiêm tốn mặc dù Chiplets có thể mang lại lợi ích một lần.

Chuyển sang vấn đề bền vững, hình 10 giải thích các “phạm vi” khác nhau tạo nên lượng khí thải carbon.

Phạm vi 1 là phát thải trực tiếp tại địa điểm do quá trình xử lý hóa chất và đốt cháy (điện cũng có thể thuộc phạm vi 1 nếu được tạo ra tại chỗ), Phạm vi 2 là do lượng khí thải carbon của điện mua vào. Phạm vi 3 không được đưa vào phân tích này mà là do lượng khí thải carbon của vật liệu được mua, việc sử dụng sản phẩm được sản xuất và những thứ như phương tiện do nhân viên của một công ty lái.

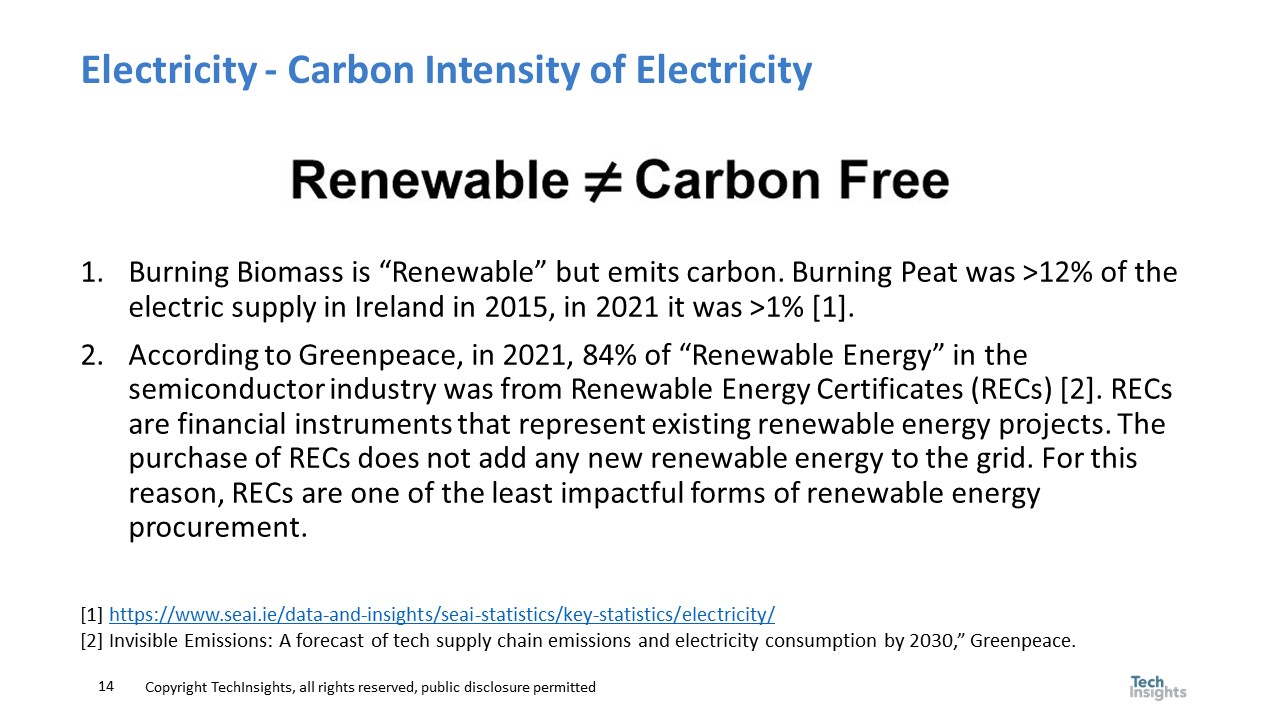

Rất nhiều công ty trong ngành bán dẫn tuyên bố rằng họ không phát thải carbon do điện vì điện hoàn toàn có thể tái tạo. Hình 11 so sánh năng lượng tái tạo và không có carbon.

Vấn đề chính là 84% năng lượng tái tạo trong ngành bán dẫn vào năm 2021 được Greenpeace phát hiện là chứng chỉ năng lượng tái tạo, trong đó một công ty mua quyền yêu cầu mức giảm mà người khác đã làm. Điều này không giống như việc lắp đặt các nguồn điện có hàm lượng carbon thấp hoặc trả tiền cho người khác để cung cấp điện có hàm lượng carbon thấp và trên thực tế không làm giảm lượng khí thải carbon toàn cầu.

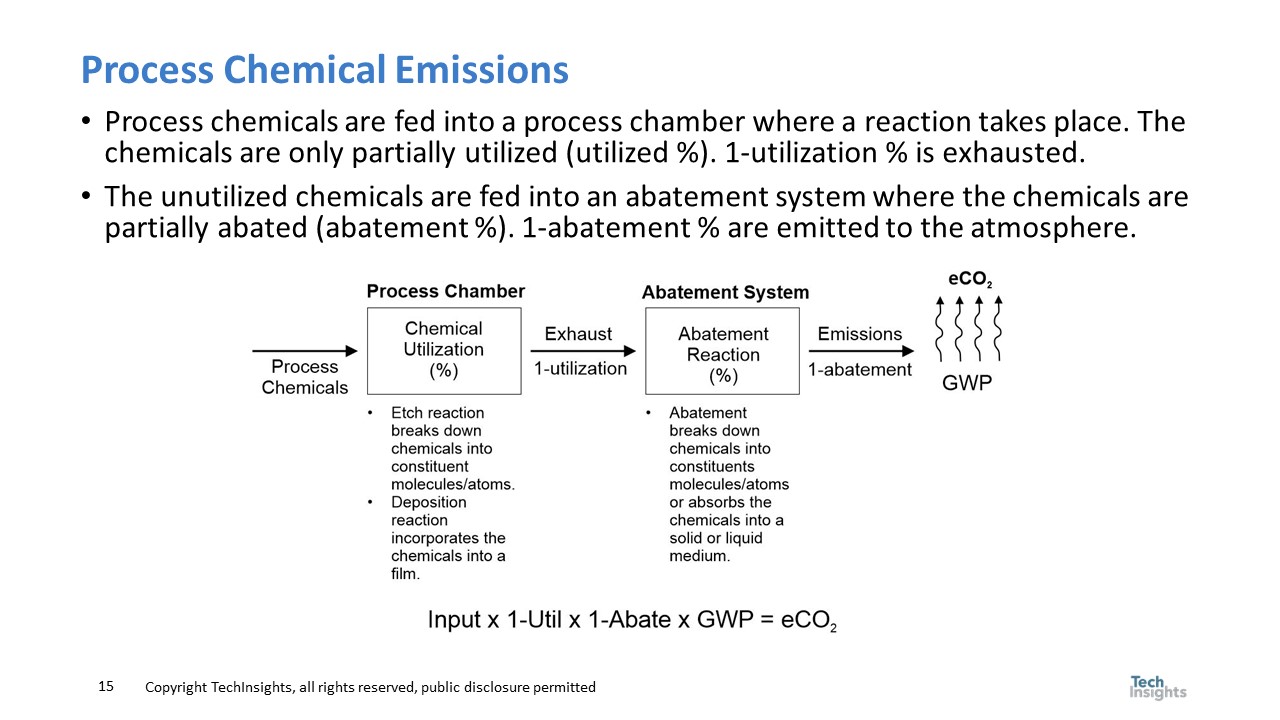

Hình 12 minh họa quá trình phát thải hóa chất diễn ra và đặc trưng như thế nào.

Hóa chất xử lý đi vào buồng xử lý trong đó một tỷ lệ phần trăm hóa chất được sử dụng trong phản ứng ăn mòn hoặc lắng đọng để phá vỡ các hóa chất hoặc kết hợp chúng thành một màng lắng đọng. 1-uitlization là lượng hóa chất thoát ra khỏi ống xả của dụng cụ. Sau đó, khí thải của dụng cụ có thể đi vào buồng xử lý để phân hủy thêm một phần trăm hóa chất và lượng khí thải ra khí quyển từ quá trình xử lý là 1 lần xử lý. Cuối cùng, Tiềm năng nóng lên toàn cầu (GWP) được áp dụng để tính toán lượng carbon tương đương của lượng phát thải. GWP tính đến thời gian hóa chất tồn tại trong khí quyển và lượng nhiệt mà hóa chất phản xạ lại so với carbon dioxide. Carbon dioxide có GWP bằng 1, các hóa chất xử lý chất bán dẫn như SF6 và NF3 có giá trị GWP lần lượt là 24,300 và 17,400 (theo IPCC AR6).

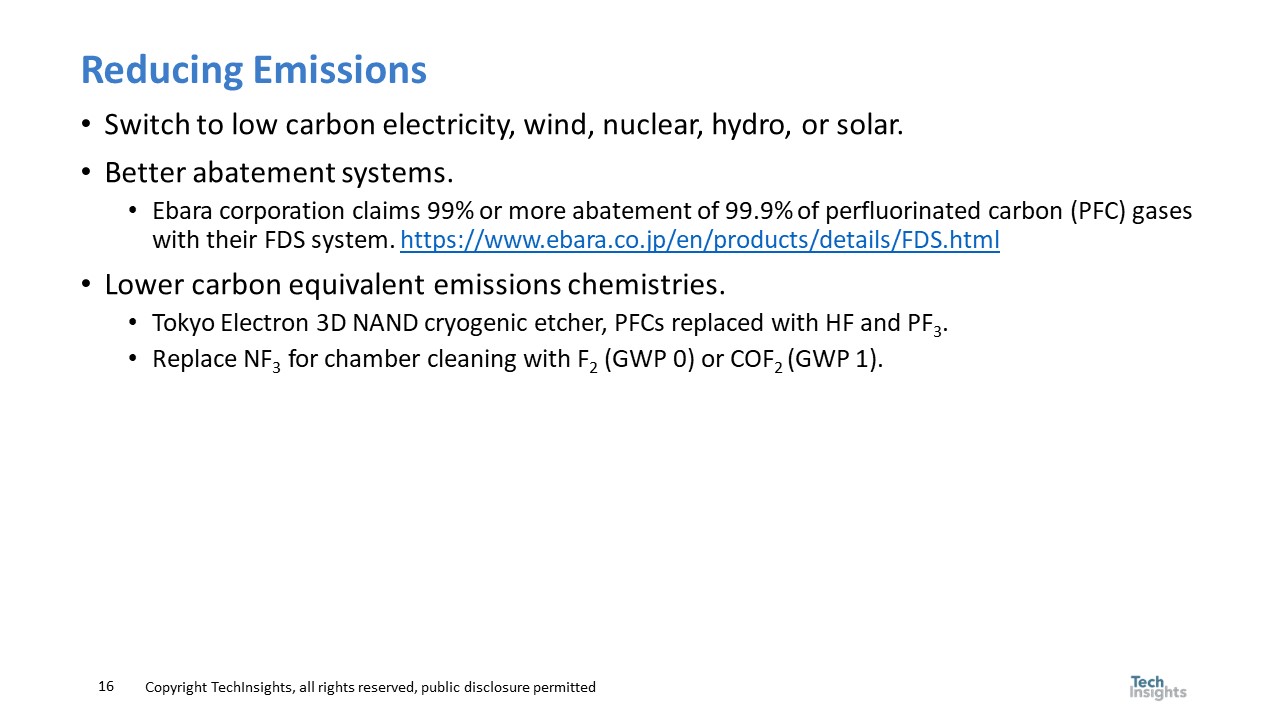

Hình 13 trình bày một số phương án giảm phát thải.

Các nguồn điện như than tạo ra 820 gam CO2 lượng khí thải tương đương trên mỗi kilowatt giờ (gCO2e/KWh) trong khi năng lượng mặt trời, thủy điện, gió và điện hạt nhân tạo ra lần lượt 48, 24, 12 và 12, gCO2e/KWh.

Hệ thống xử lý hiệu quả hơn có thể phân hủy khí xử lý hiệu quả hơn. Hệ thống giảm thiểu Fab có hiệu suất dao động từ 0% đối với một số cơ sở được báo cáo ở Hoa Kỳ (không giảm thiểu) đến ~90%. Chúng tôi ước tính mức trung bình của các nhà máy 300mm trên toàn thế giới là ~70% và hầu hết các nhà máy có kích thước wafer 200mm và nhỏ hơn đều không bị suy giảm. Có sẵn các hệ thống có hiệu suất lên tới 99%.

Hóa học phát thải thấp hơn cũng có thể được sử dụng. Tokyo Electron đã công bố một công cụ khắc mới dành cho 3D NAND sử dụng các loại khí có GWP bằng XNUMX. Các loại khí như SF6 và NF3 chủ yếu được sử dụng để đưa Fluorine (F) vào buồng làm sạch, thay thế F2 (GWP 0) hoặc COF2 (GWP 1) về cơ bản có thể loại bỏ nguồn phát thải này.

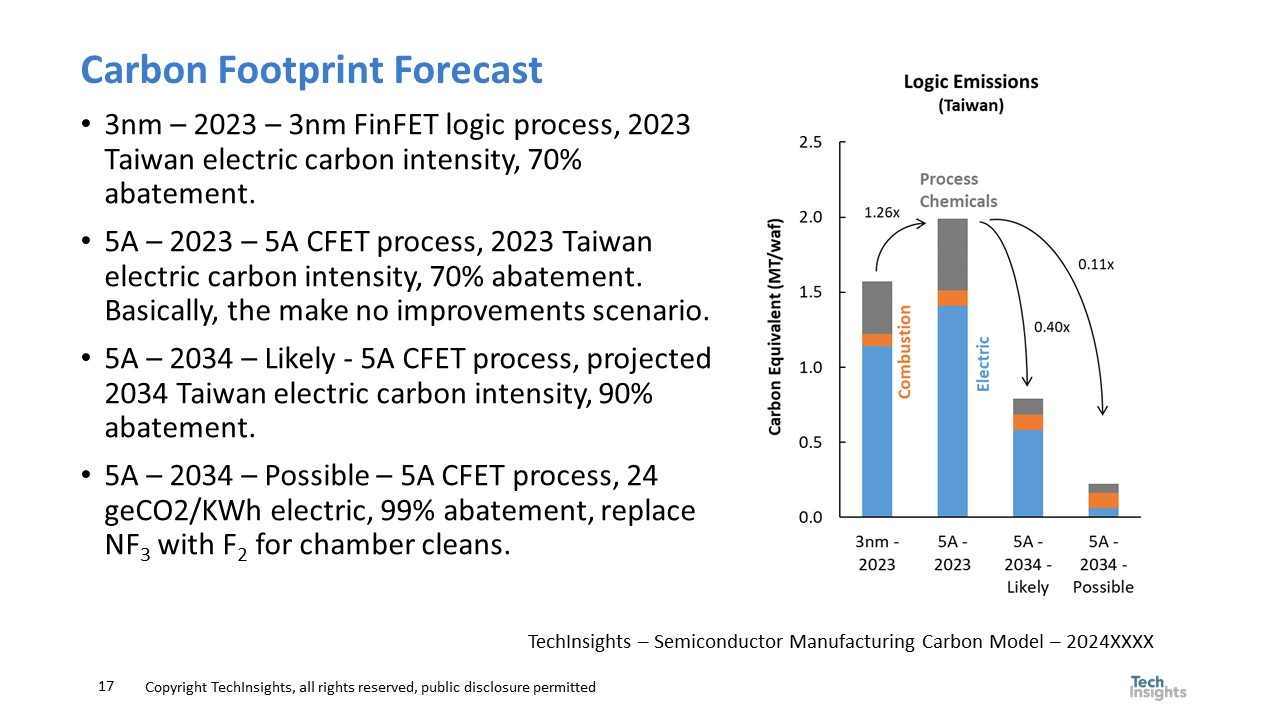

Hình 14 minh họa logic về Dự báo dấu chân carbon.

Trong hình, thanh đầu tiên bên trái là quy trình 3nm được chạy ở Đài Loan vào năm 2023 với giả định lượng khí thải carbon điện của Đài Loan và mức giảm 70%. Thanh thứ hai là quy trình 5A và lượng phát thải sẽ xảy ra nếu sử dụng cùng cường độ carbon điện năm 2023 của Đài Loan và mức giảm 70%. Sự gia tăng độ phức tạp của quy trình sẽ làm tăng dấu chân tổng thể lên 1.26 lần. Hướng tới năm 2034, điện của Đài Loan dự kiến sẽ khử cacbon đáng kể, mức giảm phát thải 90% cũng là điều phổ biến và thanh thứ ba cho thấy quy trình 5A sẽ như thế nào trong điều kiện này. Mặc dù điều này thể hiện việc cắt giảm hơn một nửa lượng khí thải, nhưng sự tăng trưởng về số lượng tấm bán dẫn do ngành vận hành vào năm 2034 có thể sẽ lấn át sự cải thiện này. Thanh cuối cùng bên phải là những gì có thể làm được nếu được đầu tư đầy đủ, nó dựa trên điện ít carbon, giảm thải 99% và sử dụng F2 để làm sạch buồng.

Hình 15 trình bày kết luận của chúng tôi:

Mật độ bóng bán dẫn, ước tính chi phí wafer và khuôn được tạo bằng Mô hình giá và chi phí chiến lược của TechInsights, một lộ trình của ngành tạo ra ước tính chi phí và giá cả cũng như các yêu cầu chi tiết về thiết bị và vật liệu. Ước tính lượng phát thải khí nhà kính được đưa ra bằng Mô hình cacbon sản xuất chất bán dẫn TechInsights. Để biết thêm thông tin, vui lòng liên hệ sales@techinsights.com

Tôi muốn cảm ơn các đồng nghiệp của tôi trong Đơn vị kinh doanh Kỹ thuật đảo ngược tại TechInsights, sơ đồ mặt bằng kỹ thuật số và báo cáo quy trình của họ đã rất hữu ích trong việc tạo ra bản trình bày này. Ngoài ra, Alexandra Noguera tại TechInsights đã trích xuất dữ liệu kích thước bóng bán dẫn I/O cho công việc này.

Cũng đọc:

IEDM 2023 – Mô hình hóa lượng phát thải carbon của wafer Fab 300mm

SMIC N+2 trong Huawei Mate Pro 60

Cập nhật ASML SEMICON Tây 2023

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/