Trong nhiều thập kỷ, một dạng phân cấp cấu trúc là phương tiện chính để xử lý độ phức tạp trong thiết kế chip. Nó không phải lúc nào cũng hoàn hảo và không có cách lý tưởng nào để phân chia và chinh phục vì điều đó cần phải tập trung vào phân tích đang được thực hiện. Trên thực tế, hầu hết các hệ thống có thể được xem xét từ nhiều hệ thống phân cấp khác nhau, đều chính xác như nhau và cùng nhau tạo thành một hệ thống phân cấp.

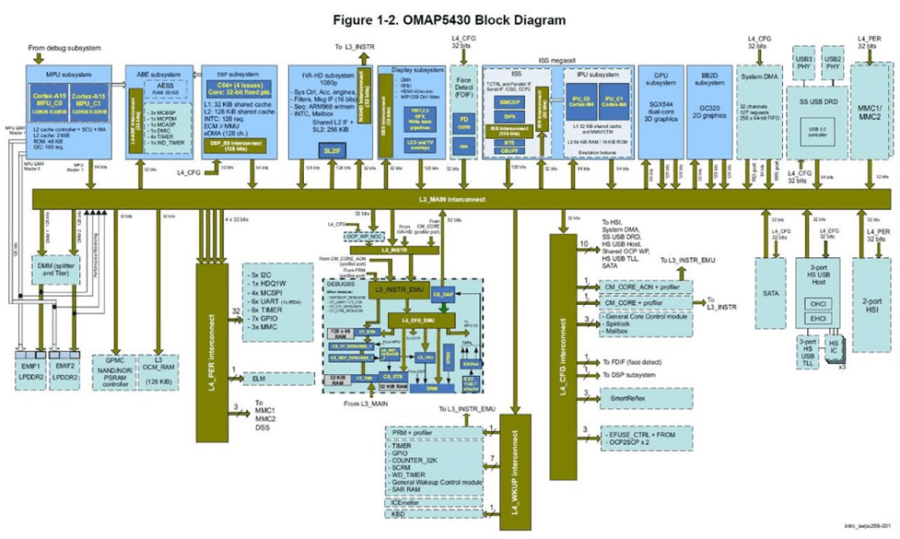

Cách dễ nhất để nghĩ về hình thức phân cấp đang được sử dụng ngày nay là yêu cầu một kỹ sư thiết kế một hệ thống theo ý tưởng. Họ có thể sẽ bắt đầu vẽ sơ đồ khối chứa các khối lớn với các nhãn như CPU, bộ mã hóa, hệ thống con hiển thị, v.v. Đây không phải là một hệ thống phân cấp chức năng, mặc dù nhiều khối được phân chia được coi là cung cấp một chức năng. Nó cũng không phải là sự phân hủy cấu trúc thuần túy, bởi vì bên trong một con chip, mọi thứ đều trở thành một biển bóng bán dẫn vô định hình.

Sơ đồ đó gần như tuân theo các hệ thống phân cấp được phát triển cho thiết kế bảng mạch in, tức là hệ thống phân cấp chân cắm. Ở cấp độ thấp nhất, bạn có thể đã sử dụng thư viện logic, chẳng hạn như dòng Texas Instruments 7400. Những thiết bị đó có bản đồ pin. Cấp độ phân cấp tiếp theo là cấp độ bo mạch và các chân kết nối với bảng nối đa năng. Hiếm khi có bất kỳ hệ thống phân cấp nào ở giữa, với các sơ đồ chỉ được trải rộng trên nhiều 'tờ'. Sau này, khi các hệ thống trở nên phức tạp hơn, hệ thống phân cấp cấu trúc cũng được hỗ trợ.

Hình 1: Sơ đồ khối điển hình của một con chip phức tạp, khoảng năm 2013. Nguồn: Texas Instruments

Hình thức phân cấp này cung cấp một sự đóng gói cho phép sự phát triển của từng khối trở nên cô lập phần nào và sự phụ thuộc lẫn nhau được giảm thiểu. Cấp cao nhất trở thành phương tiện để các khối đó được kết nối với nhau. Sau đó, mỗi khối được chia có thể trải qua quá trình phân tách tương tự.

Có một số lý do tại sao hệ thống phân cấp được sử dụng. Marc Swinnen, giám đốc tiếp thị sản phẩm tại Ansys. “Vấn đề trở nên quá lớn và bạn phải chia nó ra thành từng mảnh. Một cái khác là kỹ thuật đồng thời. Bạn có nhiều nhóm muốn thực hiện thiết kế cùng một lúc, vì vậy bạn chia nhỏ nó ra và làm việc trên các phần riêng biệt. Thứ ba là tái sử dụng. Bạn muốn sử dụng lại các khối mà người khác đã thiết kế. Một dạng tinh tế của điều đó là thư viện ô tiêu chuẩn, bản thân thư viện này là một dạng phân cấp. Lý do thứ tư là khả năng quản lý khối lượng dữ liệu. Lý do thứ năm là các cấu trúc lặp đi lặp lại, chẳng hạn như ký ức, nhiều lõi, nơi bạn có khả năng tái sử dụng một cách tự nhiên. Lý do thứ sáu là miền hỗn hợp, chẳng hạn như analog/kỹ thuật số, nơi bạn có các phong cách thiết kế khác nhau trong mỗi khối. Bạn sẽ sử dụng các công cụ khác nhau và do đó bạn chia chúng theo thứ bậc.”

Sức chứa

Khi các thiết kế ngày càng lớn hơn, nhiều thuật toán sẽ mất nhiều thời gian hơn để chạy. Việc chia nhỏ chúng có thể dẫn đến thời gian thực hiện nhanh hơn và yêu cầu ít tài nguyên hơn. Jim Schultz, giám đốc sản phẩm cấp cao của công ty cho biết: “Đối với những thiết kế lớn, khi bạn bắt đầu triển khai thực tế, có thể mất vài ngày hoặc thậm chí vài tuần để hoàn thành những thiết kế rất lớn này”. Synopsys nhóm thực hiện kỹ thuật số. “Nếu bạn làm hỏng thứ gì đó, chi phí có thể rất đáng kể. Hệ thống phân cấp là một cách để phân chia và chinh phục. Nó cho phép chúng tôi biết rằng chúng tôi có thể đóng từng phần của thiết kế tại một thời điểm. Khi chúng tôi tiếp tục bổ sung thêm chức năng và chip ngày càng lớn hơn, vấn đề không chỉ là về thời gian chạy mà còn về việc cạn kiệt tài nguyên — dung lượng bộ nhớ cần để đặt tất cả các phiên bản có thể tái sử dụng này vượt quá dung lượng.”

Để có thể thực hiện phân tích phân cấp, bạn phải đảm bảo rằng các điều kiện biên được đặt chính xác cho từng khối. Sau đó, bạn cần thực hiện phân tích xuyên ranh giới ở cấp cao nhất.

Rimpy Chugh, giám đốc sản phẩm nhân viên của Synopsys cho biết: “Phân tích phẳng mất rất nhiều thời gian nhưng mang lại độ chính xác hoàn toàn. “Việc áp dụng cách tiếp cận hộp đen trên toàn hệ thống phân cấp giúp bạn đạt được tốc độ nhanh hơn nhưng lại mất đi độ chính xác. Điều này đòi hỏi một giải pháp chuyên biệt (xem hình 2) trong đó logic giao diện cho một khối có thể được giữ nguyên để bạn có thể đồng thời được hưởng lợi về tốc độ và độ chính xác. Có thể tạo một mô hình trừu tượng ở cấp IP và sau đó sử dụng nó ở cấp SoC.”

Hình 2: Luồng phân cấp sử dụng các mô hình trừu tượng. Nguồn: Tóm tắt

Kỹ thuật đồng thời

Các nhóm thiết kế không còn tập trung trong một tòa nhà nữa. “Rất nhiều thiết kế đang được phân chia để một nhóm sẽ làm việc trên một hệ thống phân cấp và một nhóm khác làm việc trên một hệ thống phân cấp khác, và họ có thể ở trong cùng một tòa nhà hoặc có thể trải rộng khắp Thế giới,” Simon Rance, giám đốc của quản lý sản phẩm để quản lý dữ liệu & IP tại Keysight EDA. “Điều này có thể tạo ra những thách thức vì các nhóm hiện làm việc ở các mức độ khác nhau. Điều quan trọng là phải có một hệ thống phân cấp ổn định vì sau này rất khó thực hiện các thay đổi. Điều này thường chỉ xảy ra như là phương sách cuối cùng, nhưng thay vào đó, chúng tôi thấy các đội cố gắng dán hoặc giả tạo để thực hiện. Nó có thể xấu, nhưng chúng ta đang thấy thách thức này nhiều hơn với các con chiplets.”

Tái sử dụng

Hệ thống phân cấp cần phải hữu ích theo cả cách từ trên xuống và từ dưới lên. Brian LaBorde, giám đốc tiếp thị sản phẩm cấp cao của công ty cho biết: “Trong cơ thể con người, các tế bào chuyên biệt tổ chức thành các hệ thống và cơ quan tạo nên các khối xây dựng nên con người”. Nhịp. “Tương tự như vậy, các nhóm bóng bán dẫn tạo thành các mạch hoặc cổng logic tạo nên các macro được lắp ráp thành một hệ thống. Trong vài thập kỷ qua, chúng ta đã thấy các IC ngày càng lớn hơn với nhiều mạch chuyên dụng khác nhau, tất cả đều được tích hợp trên một con chip. Việc phân vùng các bố cục này là ảo và được thể hiện bằng hệ thống phân cấp trong cơ sở dữ liệu bố cục.”

Quản lý dữ liệu

Tất cả các thiết kế đều tạo ra rất nhiều dữ liệu và dữ liệu đó phải được quản lý. Keysight cho biết: “Với quản lý vòng đời kỹ thuật và nhu cầu đáp ứng các tiêu chuẩn an toàn chức năng, cho dù đó là tiêu chuẩn ISO 26262 cho ô tô hay tiêu chuẩn MIL882 cho hàng không vũ trụ quân sự, bạn có nhiều tài sản, từ tài liệu đến xác minh, tiêu chí kiểm tra, kế hoạch kiểm tra xác minh và kết quả”. Rance. “Tất cả những điều đó cần phải được giữ lại theo hệ thống phân cấp để có khả năng truy xuất nguồn gốc đầy đủ. Dù sao, việc theo dõi mọi thứ trong hệ thống phân cấp là khó khăn, nhưng bạn cũng có mọi thứ bên ngoài thiết kế, như kế hoạch xác minh và kiểm tra. Khi điều gì đó thất bại trong quá trình kiểm tra, hoặc thậm chí tệ hơn trong hiện trường, bạn quay lại và khám phá để tìm ra điều gì có thể đã thất bại. Nếu bạn chưa gắn tất cả dữ liệu và siêu dữ liệu đó vào hệ thống phân cấp, bạn sẽ không bao giờ tìm thấy nó.”

Cấu trúc lặp đi lặp lại

Nhiều thiết kế chứa các cấu trúc lặp đi lặp lại, có thể là các ô nhớ, mảng bộ xử lý nhỏ hoặc giao diện. Nhưng có những mối nguy hiểm tiềm ẩn trong những mảng này. Swinnen của Ansys cho biết: “Giả sử bạn có 16 lõi CPU được sắp xếp theo lưới 4X4”. “Về nguyên tắc, những điều này đều giống nhau, nhưng trên thực tế chúng có những điều kiện biên khác nhau. Môi trường xung quanh những cái ở rìa là khác nhau đối với mỗi cái. Nếu bạn muốn thực hiện tối ưu hóa, bạn cần phải xác định riêng từng cái, bởi vì tất cả chúng đều có ký sinh duy nhất ở biên giới. Luôn luôn có sự đánh đổi này. Làm thế nào để bạn duy trì khả năng sử dụng lại mà vẫn tìm được những thứ duy nhất? Mọi chuyện trở nên tồi tệ hơn khi bạn nhìn vào những thứ như nhiệt.”

Nhiều miền

Mặc dù analog và kỹ thuật số rất khác nhau nhưng có những khía cạnh khác của quy trình phát triển cũng sử dụng sự tách biệt của các công cụ. Ron Press, giám đốc hỗ trợ công nghệ tại cho biết: “Toàn bộ ý tưởng của EDA là giải quyết vấn đề phức tạp này, đơn giản hóa nó thành một vấn đề mang tính cấu trúc, cắt nhỏ nó và làm cho vấn đề trở nên thực sự đơn giản”. Phần mềm Công nghiệp Kỹ thuật số Siemens. “Đó là tác dụng của quá trình quét đối với DFT. Trước đây, ngay cả khi có các lõi riêng biệt, họ vẫn cố gắng thực hiện mọi thứ trong một hình ảnh phẳng lớn. Sau đó, bạn phải đợi đến giai đoạn sau trong quá trình thiết kế và bạn gặp phải một vấn đề lớn hơn nhiều. Giờ đây, với các nhóm thiết kế phân tán và lõi được tái sử dụng, mọi người cần càng nhiều plug-and-play càng tốt. Họ sẽ hoàn thành thiết kế của mình cho DFT, họ sẽ tạo mẫu cho lõi đó và sau đó nó sẽ được cắm vào cấp cao nhất. Miễn là nó có một số loại cách ly chẳng hạn như chuỗi bao bọc, chúng có thể làm việc riêng trên phần đó, hoàn thiện thiết kế DFT và hoàn thiện các mẫu của chúng. Điều đó làm cho các nhóm này trở nên độc lập và khiến toàn bộ quá trình trở nên dễ dàng hơn nhiều.”

Các vấn đề với hệ thống phân cấp cấu trúc

Không có hệ thống nào là hoàn hảo và hình thức phân cấp này gây ra một số vấn đề. Schultz của Synopsys cho biết: “Chắc chắn có chi phí chung liên quan đến việc thiết kế các giới hạn ở những ranh giới đó”. “Bạn phải chia nhỏ các ràng buộc và xác định chúng một cách chính xác, đồng thời đẩy chúng xuống các ranh giới khối. Đảm bảo rằng bạn đã xác định chính xác những ranh giới đó là một vấn đề lớn. Một yếu tố khác chống lại nó là theo thiết kế, khi bạn chia một thứ gì đó thành từng mảnh một cách vật lý và bạn nói đây là các phân vùng của tôi, thì khi tôi triển khai nó về mặt vật lý, tôi sẽ không tối ưu hóa vượt qua ranh giới đó. Bạn không thể tối ưu hóa – ranh giới đó hiện đã được cố định. Nếu có một hoạt động tối ưu hóa cần được thực hiện trên hệ thống phân cấp đó thì bạn không thể thực hiện được. Bạn đang bị giới hạn bởi chính mình.”

Điều này có thể ảnh hưởng đến một số công cụ và quy trình. Siemens' Press cho biết: “Nếu họ thực hiện một kế hoạch cấp cao nhất với DFT phân cấp, họ có thể lên kế hoạch đưa rất nhiều chân vào một lõi”. “Sau đó, hóa ra lõi đó không cần quá nhiều mẫu và lõi khác mà họ phân bổ số lượng chân tương tự cần nhiều mẫu hơn. Nếu họ đã sớm đóng băng thiết kế của mình, từ cấp cao nhất, thì việc phân phối mẫu của họ sẽ không hiệu quả như vậy.”

Việc thiết lập hệ thống phân cấp sai có thể hạn chế bạn theo nhiều cách. Schultz cho biết thêm: “Một trong những vấn đề lớn, đặc biệt là với các SoC lớn, là mạng và giao tiếp có thể tạo ra tắc nghẽn”. “Chúng tôi thấy tắc nghẽn trên chip, đặc biệt là khi thiết kế được phân vùng kém. Tôi thấy các khối nói chuyện với các khối khác và bạn phải tạo nguồn cấp dữ liệu thông qua. Điều đó có thể gây ra rất nhiều tắc nghẽn trong thiết kế. Ngoài ra, việc đáp ứng các yêu cầu về thời gian của bạn sẽ khó hơn nhiều khi bạn làm những việc như vậy vì bạn không thể dễ dàng tối ưu hóa đường dẫn đầy đủ đó. Bạn phải tối ưu hóa từng khối riêng lẻ và hy vọng rằng tất cả các đường dẫn đều ổn.”

Những thay đổi tinh tế có thể diễn ra ở ranh giới. Swinnen nói: “Khi bạn tiếp giáp hai khối nhà, bạn có một kết nối hợp lý giữa chúng, nhưng không có gì về mặt vật lý ở đó cả”. “Các chân chỉ chạm vào nhau chứ không có dây. Nhưng trong danh sách mạng của bạn, bạn có một sợi dây lẽ ra phải ở đó. Nó được cho là có điện trở, điện dung. Bạn có dây logic nhưng không có dây vật lý. Sau đó, bạn có nguồn cấp dữ liệu xuyên qua, trong đó các dây đi vào một bên của khối, chạy qua khối và đi ra đầu bên kia. Có chân, có dây vật lý, nhưng không có dây logic. Về mặt logic, nó không tồn tại. Bạn không vẽ điều đó trên sơ đồ của mình.”

Một số công cụ có thể xử lý các hệ thống phân cấp xấu nhưng việc sửa chúng sẽ tạo ra các vấn đề khác. Schultz nói: “Bạn có một hệ thống phân cấp hợp lý khi phát triển RTL và tổng hợp nó. “Khi bạn thực hiện thiết kế vật lý của mình, các hệ thống phân cấp logic đó phải ánh xạ từng cái một vào một phân vùng vật lý. Điều cuối cùng xảy ra là, trong hệ thống phân cấp logic của tôi, tôi có thể có một đứa trẻ đang nói chuyện với đứa trẻ bên dưới hệ thống phân cấp logic đó và thực sự đang nói rất nhiều với điều gì đó thuộc về cha mẹ khác, và hai cha mẹ đó trở thành những vách ngăn vật lý của riêng chúng. Hai cha mẹ đó có thể được đặt ở hai phía đối diện của con chip. Hệ thống phân cấp logic không có lợi cho việc triển khai vật lý. Cách xử lý vấn đề này là thông qua tái cấu trúc RTL. Bây giờ chúng tôi đang bắt đầu di chuyển mọi thứ và sửa chữa logic, nhưng đó không phải là điều mà một RTL hoặc nhà thiết kế logic thuần túy sẽ biết. Thông tin đó chỉ xuất hiện khi bạn tính đến hệ thống phân cấp vật lý. Cần phải có sự giao tiếp giữa hai bên để thực sự tối ưu hóa hệ thống phân cấp vật lý đó.”

Điều này xảy ra ở những nơi khác trong dòng chảy. Frank Schirrmeister, phó chủ tịch giải pháp và phát triển kinh doanh tại cho biết: “NoC nằm ở cấp độ buồng lái cao nhất, nơi bạn có các khía cạnh tích hợp của toàn bộ hệ thống phân cấp”. động mạch. “Khi cần thay đổi hệ thống phân cấp, có lẽ do hai thuộc tính phi chức năng khác nhau giữa các miền quyền lực, việc tái cấu trúc RTL có thể đơn giản. Việc có mức độ tích hợp cao hơn cho hệ thống phân cấp giúp bạn sắp xếp lại hệ số và cơ cấu lại RTL cho phù hợp và bạn thực sự không muốn thực hiện điều này bằng cách phải thay đổi tất cả các mô-đun của mình theo cách thủ công.”

Theo dõi điều này có thể là một cơn ác mộng. Rance nói: “Hãy nghĩ đến việc kiểm soát sửa đổi đối với một tài liệu hoặc một tệp là một phần của hệ thống phân cấp. “Sau đó, bạn có thể có nhiều phiên bản hoặc bản sửa đổi của hệ thống phân cấp đó, tùy thuộc vào việc bạn đang làm. Bạn có thể có một nhóm xác minh thực hiện phân tích PPA và nhận thấy rằng nếu họ điều chỉnh điều này một chút và tạo một phiên bản khác của hệ thống phân cấp này thì nó sẽ hoạt động tốt hơn. Bạn cần phải theo dõi điều đó.”

Mặc dù hệ thống phân cấp giúp chúng ta phân chia và chinh phục, nhưng một số thứ lại thách thức mọi nỗ lực thực hiện sự đơn giản hóa này. Schirrmeister của Arteris cho biết: “Những việc như phân tích nhiệt cần phải được thực hiện trên toàn bộ chip. “Nhưng bạn cần có khả năng liên hệ điều này với những gì đang diễn ra trong chức năng của chip, với dữ liệu chạy qua nó. Bạn muốn có thể chụp ảnh chip, nơi bạn có thể xem các điểm nóng và vị trí của từng phần chức năng, có thể là từ góc độ vòng đời và bị ảnh hưởng nhiều nhất. Việc so sánh điều này với dữ liệu là điều không hề đơn giản.”

Các hệ thống phân cấp khác

Các hệ thống phân cấp khác tồn tại, chẳng hạn như hệ thống phân cấp chức năng. Gần nhất mà chúng ta có ngày nay là một hệ thống theo dõi yêu cầu bắt đầu bằng các định nghĩa cấp cao về những gì hệ thống nên làm. Chúng được chia thành các nhiệm vụ ngày càng đơn giản hơn, cho đến khi xác định được logic hoặc mạch điện khác thực sự cung cấp nó, cùng với các bàn thử nghiệm xác minh rằng yêu cầu thích hợp được đáp ứng.

Một số hệ thống phân cấp đến và đi trong quá trình thiết kế. Schirrmeister nói: “Bạn có thể có một hệ thống phân cấp cho cây đồng hồ. “Có hệ thống phân cấp điện cho hệ thống phân phối điện. Và sau đó, các công cụ phân tích hệ thống sẽ nhìn thấy một hệ thống phân cấp về cách chúng kết nối mọi thứ lại với nhau để có được góc nhìn toàn diện về chip. Điều chúng tôi nghĩ đến với ESL (cấp độ hệ thống điện tử) là khái niệm về thông số kỹ thuật chức năng có thể thực thi được mô tả toàn bộ sự việc. Đây là điều vẫn chưa xuất hiện. Bằng cách nào đó, chúng tôi dường như đang thoát khỏi nó, điều này thật đáng ngạc nhiên.”

Bố cục vật lý cung cấp một hệ thống phân cấp khác. Ở cấp độ cao nhất là quy hoạch sàn, sử dụng hệ thống phân cấp cấu trúc làm điểm bắt đầu. Các khối này được đặt và kết nối được định tuyến giữa chúng. Mỗi khối được bố trí bằng cách sử dụng tổng hợp vật lý, một lần nữa xử lý kết nối cục bộ. 3D-IC sẽ bổ sung thêm một chiều hướng mới cho vấn đề này, trong đó việc định tuyến hiện có thể tồn tại theo hướng Z.

LaBorde của Cadence cho biết: “Khi chúng ta bắt đầu thấy các hệ thống 2.5D và 3D dựa trên chiplet thay thế các thiết kế hệ thống trên chip (SoC), hệ thống phân cấp sẽ không còn là một cấu trúc chiến lược mà là sự thể hiện thực tế vật lý”. “Các macro trong sơ đồ có thể đại diện cho các chip trong một hệ thống, mỗi macro có quy trình riêng. Các kết nối giữa chúng sẽ là các điểm hàn chứ không phải là các chốt tượng trưng trên bố cục.”

Kết luận

Mặc dù không hoàn hảo nhưng sự phân rã cấu trúc không chính thức được sử dụng ngày nay đã được chứng minh là một hệ thống phân cấp lão luyện. Một số khía cạnh của quy trình bị ảnh hưởng vì nó, nhưng hầu hết đều có thể sử dụng nó một cách hiệu quả và các công cụ có thể bù đắp cho những thiếu sót của nó. Mặc dù có một lượng tiềm năng tối ưu hóa nhất định bị mất đi vì nó, nhưng đây có lẽ là một trong những sự hy sinh nhỏ vì năng suất.

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiengineering.com/an-entangled-heterarchy/