Trong phương pháp thiết kế chip 3D-IC (Mạch tích hợp ba chiều), chiplet hoặc tấm wafer được xếp chồng lên nhau theo chiều dọc và được kết nối bằng Through Silicon Vias (TSV) hoặc liên kết lai.

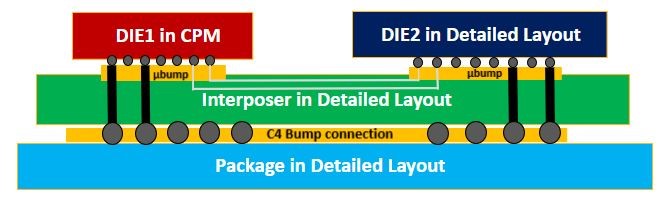

Phương pháp thiết kế 2.5D-IC đặt nhiều chiplet cạnh nhau trên một bộ xen kẽ silicon. Microbumps và dây kết nối thiết lập kết nối giữa các khuôn trong khi TSV được sử dụng để tạo kết nối với chất nền của gói.

Tại sao chúng ta cần 3D-IC?

Các công nghệ mới nổi như Trí tuệ nhân tạo, máy học và điện toán tốc độ cao yêu cầu các IC có chức năng cao, tốc độ cao và nhỏ gọn. Công nghệ thiết kế 3D-IC mang lại hiệu suất cực cao và giảm mức tiêu thụ điện năng, khiến nó phù hợp với CPU đa lõi, GPU, bộ định tuyến tốc độ cao, điện thoại thông minh và ứng dụng AI/ML. Khi ngành công nghệ cao phát triển, nhu cầu về kích thước nhỏ hơn và nhiều chức năng hơn cũng tăng lên. Khả năng tích hợp không đồng nhất của thiết kế 3D-IC cung cấp nhiều mật độ chức năng hơn trong một khu vực nhỏ hơn. Kiến trúc dọc của 3D-IC cũng làm giảm độ dài kết nối, cho phép trao đổi dữ liệu nhanh hơn giữa các khuôn. Nhìn chung, công nghệ đóng gói tiên tiến này là một phương pháp thiết kế vi mạch rất cần thiết để đáp ứng nhu cầu ngày càng tăng về tốc độ, nhiều chức năng hơn và mức tiêu thụ điện năng ít hơn.

Lợi ích của 3D-IC

Một ưu điểm chính của 3D-IC là tích hợp không đồng nhất. Nó cho phép tích hợp các bộ ba trong các nút công nghệ khác nhau trong cùng một không gian. Logic kỹ thuật số, mạch tương tự, bộ nhớ và cảm biến có thể được đặt trong một gói duy nhất. Điều này cho phép tạo ra các giải pháp tùy chỉnh cao và hiệu quả phù hợp với các yêu cầu ứng dụng cụ thể.

Mật độ tích hợp cao hơn là một lợi ích khác của thiết kế 3D-IC. Bằng cách xếp chồng nhiều lớp chiplet hoặc tấm wafer được kết nối với nhau theo chiều dọc, diện tích chip có sẵn được sử dụng hiệu quả hơn. Mật độ tích hợp tăng lên này cho phép bao gồm nhiều chức năng hơn trong một diện tích nhỏ hơn, điều này đặc biệt có lợi trong các ứng dụng mà giới hạn về kích thước và trọng lượng là rất quan trọng, chẳng hạn như thiết bị di động và thiết bị IoT.

3D-IC cũng thể hiện hiệu suất điện cao hơn. Chiều dài kết nối giảm trong các chip xếp chồng lên nhau theo chiều dọc dẫn đến đường dẫn tín hiệu ngắn hơn và điện trở thấp hơn, giúp cải thiện tính toàn vẹn của tín hiệu và giảm độ trễ tín hiệu. Điều này có nghĩa là tốc độ truyền dữ liệu cao hơn, tiêu thụ điện năng thấp hơn và nâng cao hiệu suất tổng thể của hệ thống.

Với các phương pháp cấu hình mới nhất như CoWoS của TSMC (Chip On Wafer on Substrate) và WoW (Wafer on Wafer), sử dụng các kỹ thuật liên kết lai, độ dài kết nối được giảm thiểu hơn nữa, dẫn đến giảm tổn thất điện năng và cải thiện hiệu suất.

Công nghệ 3D-IC cung cấp một loạt các lợi thế đặc biệt, bao gồm tích hợp không đồng nhất, mật độ tích hợp cao hơn, kích thước nhỏ hơn, hiệu suất điện cao hơn, giảm chi phí và thời gian đưa sản phẩm ra thị trường nhanh hơn. Những lợi thế này làm cho 3D-IC trở thành một giải pháp hấp dẫn cho các thiết kế chip tiên tiến trong các ngành công nghiệp khác nhau.

Những thách thức của thiết kế 3D-IC

Mặc dù các phương pháp thiết kế 2.5D/3D-IC có nhiều ưu điểm, nhưng các phương pháp mới này cũng đưa ra những thách thức mới liên quan đến vật lý. Tính toàn vẹn về cấu trúc, nhiệt, Nguồn và Tín hiệu của toàn bộ hệ thống 3D-IC phức tạp hơn. Các nhà thiết kế 3DIC đang ở giai đoạn đầu của quá trình học tập để nắm vững các thách thức về tính toàn vẹn trong quá trình triển khai thực tế của hệ thống. Các phương pháp mô phỏng chính xác là điều bắt buộc đối với bất kỳ nhà thiết kế chip nào, đặc biệt là khi xử lý 3D-IC. Mỗi thành phần trong hệ thống 3D-IC phải được kiểm tra và xác thực bằng các công cụ mô phỏng có độ chính xác cao.

Tìm hiểu thêm về những phát triển mới nhất trong thiết kế 3D-IC, các thách thức và mô phỏng cũng như chìa khóa để thiết kế 3D-IC thành công bằng cách đăng ký hội thảo trực tuyến này, Thiết kế và phân tích các hệ thống Multi-Die & 3D-IC bởi các chuyên gia Ansys. Ông cũng sẽ thảo luận về các phương pháp mô phỏng nâng cao để dự đoán các vấn đề về tính toàn vẹn cấu trúc, nhiệt, Nguồn và Tín hiệu có thể xảy ra trong 3D-IC.

Cũng đọc:

Chiplet Q&A với John Lee của Ansys

Phân tích đa vật lý từ chip đến hệ thống

Danh sách kiểm tra để đảm bảo các bộ chuyển đổi silicon không giết chết thiết kế của bạn

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- EVM tài chính. Giao diện hợp nhất cho tài chính phi tập trung. Truy cập Tại đây.

- Tập đoàn truyền thông lượng tử. Khuếch đại IR/PR. Truy cập Tại đây.

- PlatoAiStream. Thông minh dữ liệu Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- nguồn: https://semiwiki.com/eda/ansys-inc/330137-webinar-revolutionizing-chip-design-with-2-5d-3d-ic-design-technology/