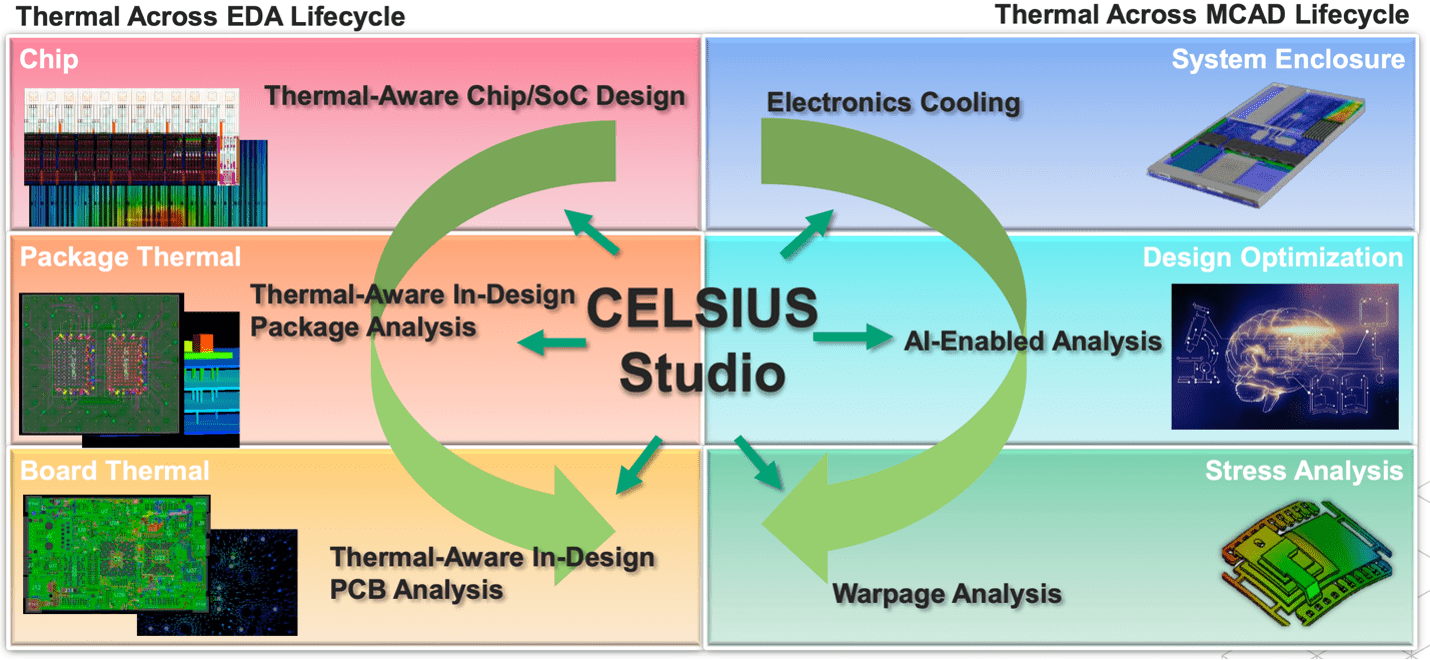

Tiếp tục chủ đề đa vật lý, gần đây tôi đã nói chuyện với Melika Rohandell (Giám đốc quản lý sản phẩm tại Cadence) về sự hội tụ liên tục giữa MCAD và ECAD. Trước tiên, bạn nên biết rằng Melika có bằng Tiến sĩ về kỹ thuật cơ khí và có kiến thức nền tảng sâu rộng về kỹ thuật nhiệt tại Broadcom và Qualcomm, tất cả đều rất phù hợp với chủ đề này. Một điều tiết lộ ngay lập tức từ cuộc thảo luận này đối với tôi là việc phân tích và tối ưu hóa nhiệt cho chip và hệ thống thường được xử lý bởi các kỹ sư cơ khí hợp tác với nhóm thiết kế điện. Điều này có ý nghĩa, nhưng sự khác biệt về chuyên môn và nguyên tắc có thể và thường gây ra sự va chạm tốc độ đáng kể giữa các yếu tố thiết kế này, dẫn đến sự thiếu hiệu quả trong việc thực hiện và tối ưu hóa. C Studio đặt mục tiêu làm phẳng những gờ giảm tốc độ này.

Có một trò đùa cũ trong vật lý. Một nông dân chăn nuôi bò sữa yêu cầu trường đại học địa phương giúp đỡ để tìm hiểu lý do tại sao sản lượng sữa tại trang trại của anh ta lại giảm. Sau khi tổ chức một chuyến tham quan trang trại của mình, thảo luận chi tiết và nghiên cứu nhiều ở trường đại học, anh nhận được một lá thư từ khoa vật lý lý thuyết. Họ nói với anh rằng họ đã tìm ra giải pháp, nhưng nó chỉ có tác dụng với những con bò hình cầu trong chân không. Vấn đề là các nhà vật lý phải đơn giản hóa một vấn đề rất nhiều, chỉ ưu tiên một thành phần để tìm ra giải pháp phân tích.

Phân tích số dựa trên máy tính không gặp phải hạn chế đó, bỏ qua các câu trả lời chính xác cho các câu trả lời gần đúng mặc dù cần có độ chính xác bất kỳ. Nó cũng không bị giới hạn khi chỉ xem xét tác dụng vật lý tại một thời điểm. Điều này cũng tốt vì trong thiết kế chip và hệ thống, nhiều yếu tố vật lý rất quan trọng ở mọi cấp độ thiết kế và không thể tách rời một cách rõ ràng.

Hoạt động điện chắc chắn tạo ra nhiệt (định luật thứ hai của nhiệt động lực học): trong bóng bán dẫn, khối logic, chip/chiplet, gói, trên bảng và trong giá đỡ. Nhiệt được tạo ra cục bộ trong các khu vực sử dụng tích cực, có thể dẫn đến hoạt động không đúng hoặc hư hỏng vật lý nếu không được tản nhiệt một cách hiệu quả. Một cách để giảm nhiệt độ là giảm tốc độ xung nhịp cho đến khi đủ nguội nhưng việc giảm đó cũng làm ảnh hưởng đến hiệu suất. Để vận hành tối ưu, nhiệt sinh ra từ hoạt động điện (động và rò rỉ) phải được tiêu tán một cách thụ động (khuếch tán nhiệt, bức xạ và đối lưu) và/hoặc chủ động (làm mát bằng không khí hoặc chất lỏng cưỡng bức). Nhiều loại vật lý phải được phân tích cùng nhau.

Một cân nhắc quan trọng khác là xu hướng cong vênh của các cấu trúc khi bị nung nóng. Chip/chiplets được chế tạo bằng nhiều lớp vật liệu, mỗi lớp có đặc tính giãn nở nhiệt khác nhau. Chiplets nằm trên các lớp xen kẽ và các lớp khác, bên trong một gói nằm trên PCB nhiều lớp, v.v. – nhiều vật liệu khác nhau hơn với hệ số giãn nở khác nhau. Khi hai (hoặc nhiều) lớp được kết nối giãn nở khi bị nung nóng, một lớp sẽ giãn nở nhiều hơn lớp kia. Nếu sự giãn nở vi sai này đủ lớn thì cấu trúc sẽ bị cong vênh. Điều đó làm tăng thêm áp lực lên các kết nối điện giữa các lớp, có thể bị gãy và ngắt kết nối. Các vấn đề thuộc loại này không tự phục hồi sau khi làm mát; cách duy nhất để sửa điện thoại của bạn nếu kết nối bị đứt là mua một chiếc điện thoại mới. Cần nhiều phân tích đa vật lý hơn.

Thêm một nếp nhăn nữa khiến vấn đề quản lý nhiệt càng trở nên phức tạp hơn. Tất cả các phân tích này phải hoạt động trên một phạm vi quy mô rất rộng, từ hàng chục micron trong thiết kế vi mạch đến hàng chục cm trên bảng, cho đến phạm vi hàng mét trong giá đỡ. Nhiệt có thể được tạo ra ở mọi cấp độ và việc làm mát phải có hiệu quả ở mọi cấp độ. Phân tích đa vật lý cũng phải thực hiện ở nhiều quy mô.

Cels Studio tích hợp những hiểu biết sâu sắc về triển khai và phân tích nhiệt từ Innovus cho mạch kỹ thuật số, Virtuoso cho mạch tùy chỉnh/analog, Tính toàn vẹn cho 3D-IC, AWR cho IC vi sóng và Allegro cho thiết kế bảng mạch. Những thông tin chuyên sâu này hướng dẫn việc phân tích ứng suất và nhiệt tổng thể của nguồn điện cùng với các chiến lược giảm nhiệt, tối ưu hóa vị trí cũng như vị trí cảm biến nhiệt và thông qua nhiệt độ.

Mô hình nhiệt và ứng suất được thực hiện thông qua phân tích phần tử hữu hạn (FEA), với các mắt lưới được thiết kế để hỗ trợ độ chính xác cần thiết từ các cấu trúc hạt mịn đến hạt thô trên phạm vi quy mô rộng đó. Sự tản nhiệt thông qua đối lưu và/hoặc thông qua làm mát tích cực (quạt, v.v.) được mô hình hóa trong Bộ giải Cadence Celc EC.

Rõ ràng, phân tích này yêu cầu các mô hình MCAD có thể được tạo trong công cụ hoặc có thể được nhập từ nhiều định dạng MCAD phổ biến. Nghe có vẻ dễ dàng nhưng về mặt lịch sử, theo Melika, những khó khăn trong việc ghép nối liền mạch MCAD và ECAD đã góp phần đáng kể vào những va chạm tốc độ đó. Trong Cels Studio, các chuyên gia MCAD và ECAD nội bộ của Cadence đã giảm nỗ lực nhập từ nhiều ngày xuống mức tác động không đáng kể đến quy trình phân tích. Do đó cung cấp một đường dẫn hợp lý để phân tích nhiệt, ứng suất và làm mát trên bo mạch và trong giá đỡ.

Con đường được sắp xếp hợp lý đó làm cho việc phân tích trong thiết kế (IDA) trở thành một đề xuất thực tế hơn nhiều. Những trao đổi xuyên suốt trước đây giữa kỹ thuật và kỹ thuật nhiệt rõ ràng đã hạn chế cơ hội cho việc đồng thiết kế/tối ưu hóa, có xu hướng đưa ra ước tính dự đoán tốt nhất để hướng dẫn các nhóm nhiệt, sau đó là sự tranh giành ở cuối để phù hợp với các phân tích cuối cùng từ các nhóm điện tử. Giờ đây, với thời gian quay vòng nhanh hơn để nhập các bản cập nhật mô hình cơ khí, việc đồng tối ưu hóa thông qua thiết kế trở nên khả thi, giảm nguy cơ tranh giành muộn và thay đổi lịch trình/BOM.

Thời gian quay nhanh hơn cũng cho phép phân tích hỗ trợ AI. Tôi sẽ đi ra ngoài ở đây với một chút suy đoán của riêng tôi. Để phân tích/tối ưu hóa một thiết kế phức tạp có nhiều tham số, bạn có thể quét các tham số đó trên tất cả các cài đặt và kết hợp có thể có. Tuy nhiên, độ phức tạp của việc quét sẽ tăng theo cấp số nhân khi có nhiều tham số được thêm vào. Có một khái niệm trong Thiết kế thí nghiệm được gọi là Mảng che phủ. chúng tôi đã viết trong blog Đổi mới, để giảm đáng kể số lượng kết hợp bạn phải xem xét trong khi chỉ giảm mức độ phù hợp một cách khiêm tốn. Chỉ có một vấn đề – việc tìm ra những phương án phù hợp để lựa chọn đòi hỏi rất nhiều sự khéo léo của con người. Học máy có thể là một cách khác để đạt được điều đó, thông qua nhiều thông số hơn.

Tôi không biết liệu đây có phải là phương pháp đằng sau Tính tối ưu hay các công cụ khác có tính chất này hay không, nhưng tôi nghĩ một số kỹ thuật liên quan có thể đóng một vai trò nào đó. Đặc biệt vì phương pháp này có thể được áp dụng cho bất kỳ vấn đề nào, cơ học hoặc điện tử, để chọn một tập hợp con nhỏ và có thể quản lý được từ một phạm vi quét không thực tế, nhằm đạt được phạm vi bao phủ gần như tối ưu trong phân tích 😀

Bạn có thể đọc thêm về C Studio nhấp vào ĐÂY .

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiwiki.com/artificial-intelligence/341997-cadence-debuts-celsius-studio-for-in-design-thermal-optimization/