Trước đây, tôi đã tránh các chủ đề về tín hiệu hỗn hợp, cho rằng chúng tách rời khỏi kỹ thuật số và có thể để lại cho các chuyên gia. Quan điểm đơn giản đó không còn giữ được nước nữa. Analog và kỹ thuật số đang ngày càng được liên kết chặt chẽ hơn thông qua các vòng điều khiển và đường dẫn dữ liệu, đòi hỏi phải có hành động cân bằng cẩn thận trong việc xác minh giữa hiệu suất, độ chính xác và xác minh theo chỉ số tổng thể.

Những cải tiến trong hỗ trợ cho lĩnh vực này không phải là điều dễ dàng có được. Một cuộc khảo sát của Wilson năm 2020 đã báo cáo rằng số vòng quay tăng vọt đáng kể do các vấn đề về analog. Tệ hơn nữa, khách hàng của hệ thống hiện đang yêu cầu dữ liệu số liệu thống nhất về phạm vi phủ sóng, độ an toàn và nguồn điện. Chúng tôi sẽ cần phải bước ra khỏi vùng an toàn kỹ thuật số của mình để hiểu rõ hơn về các thách thức và giải pháp xác minh toàn bộ hệ thống. Tôi xin cảm ơn Shekar Chetput (Giám đốc Nhóm R&D về Xcelium/Tín hiệu hỗn hợp) và Paul Graykowski (Giám đốc Tiếp thị Sản phẩm), cả hai đều tại Cadence, vì đã hướng dẫn tôi trên con đường này. 😊

Trình điều khiển ứng dụng và thách thức tín hiệu hỗn hợp

Tất cả các loại cảm biến đều yêu cầu hỗ trợ kỹ thuật số để thu thập dữ liệu hiệu chuẩn và bù sai lệch. Hiệu chuẩn cũng là một yếu tố đối với giao diện IO; DDR cung cấp một ví dụ quen thuộc. RF cho 5G/6G phải hỗ trợ nhiều băng tần và định dạng chùm tia lai, lại được quản lý từ miền kỹ thuật số. Hệ thống quản lý pin, cần thiết cho xe điện, xử lý các hành vi sử dụng và sạc phức tạp như điều hòa trước, sạc nhanh, nạp đầy và bảo vệ pin, tất cả (bạn đoán vậy) đều được giám sát kỹ thuật số.

Các thiết bị cấy ghép y tế, được tuân thủ các tiêu chuẩn rất cao về an toàn và độ tin cậy, hiện cung cấp khả năng liên lạc không dây, đồng thời cảm biến và bộ truyền động phải được xác minh dựa trên các mô hình cơ thể (mạng RC). Các ô nhớ không thay đổi xử lý nhiều điện áp và mạch hỗ trợ để đọc, lập trình và phát hiện hao mòn/lỗi. Ngay cả thiết kế kỹ thuật số cũng phụ thuộc vào IC quản lý nguồn (PMIC) cung cấp nhiều điện áp dưới sự điều khiển kỹ thuật số, giám sát các tình huống quản lý nguồn phức tạp. Những điều này hiện mở rộng sang quản lý điện áp cao trong xe điện.

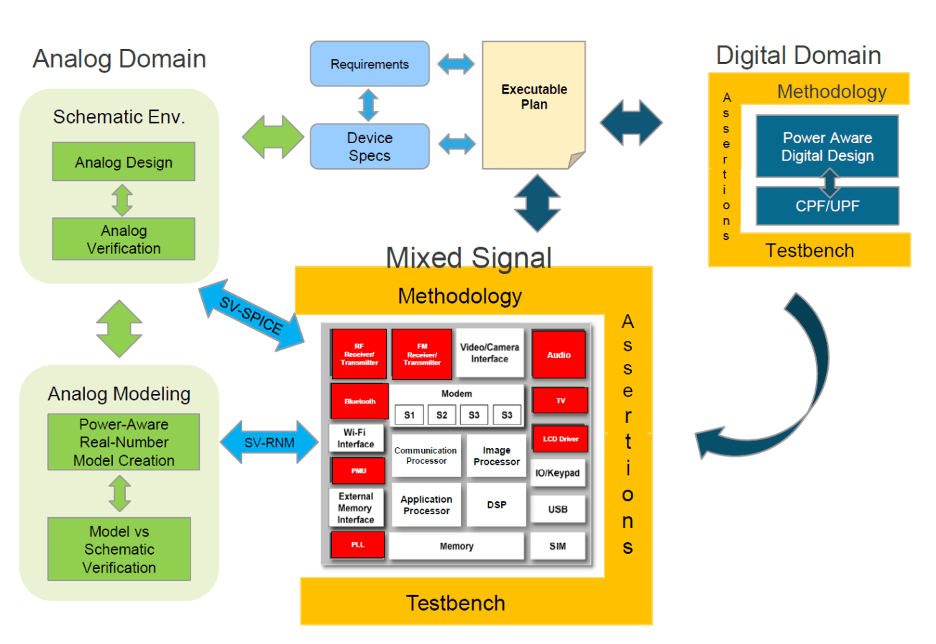

Điểm chung cho tất cả các mục tiêu là nhu cầu tìm sự cân bằng giữa thế giới analog/RF, trong đó các mô hình SPICE có độ chính xác cao nhưng chu kỳ/giây rất thấp và thế giới kỹ thuật số có thông lượng chu kỳ/giây rất cao nhưng độ chính xác tương tự rất thấp (0/ 1 cho điện áp và không có khái niệm về dòng điện hoặc trở kháng). Đồng mô phỏng là câu trả lời hiển nhiên, nhưng bạn không thể chỉ kết hợp độ chính xác thấp/hiệu suất cao và độ chính xác cao/hiệu suất thấp. Chúng cần giao diện thông minh.

Tìm sự cân bằng phù hợp

Đầu tiên hãy làm cho SPICE chạy nhanh hơn và làm cho mô phỏng kỹ thuật số chính xác hơn. Cadence tăng tốc SPICE thông qua trình mô phỏng Spectre FX, trong đó các phần của mạch có thể chạy ở bất kỳ chế độ nào trong số 4 chế độ, từ độ chính xác tương tự hoàn toàn đến các chế độ trừu tượng hóa dần dần duy trì một số mức độ chính xác trong khi vẫn ảnh hưởng đến độ chính xác hoàn toàn.

Để cải thiện độ chính xác trong kỹ thuật số, bước đầu tiên là hỗ trợ wreal Verilog-AMS/SystemVerilog, tín hiệu số thực đủ tốt cho các giao diện đơn giản. Có thể thực hiện một điều gì đó gần hơn với mô hình tương tự thông qua các mô hình số thực (RNM) được hỗ trợ bởi kiểu mạng Verilog/SV, trong đó tín hiệu được mô hình hóa dưới dạng cấu trúc điện áp, dòng điện và trở kháng, cho phép phân giải giữa các mạng được kết nối. Cadence cung cấp loại mạng RNM EEnet (Mạng tương đương điện). Với EEnets, có thể xây dựng một mô hình hành vi có ý nghĩa chạy các thử nghiệm có cường độ nhanh hơn trong khi vẫn có thể đạt được độ chính xác ở cấp độ SPICE trong một số trường hợp sử dụng.

Các mô hình Spectre FX và RNM/EEnet cùng nhau cung cấp nhiều khả năng cho việc lập mô hình. Một mô hình hành vi đầy đủ hoặc mô hình EEnet có thể rất hữu ích trong thiết kế kiến trúc để khám phá các tùy chọn khác nhau mà không bị sa lầy vào chi tiết. Khi có sẵn các mẫu, Shekar cho tôi biết trường hợp sử dụng này hiện đang thu hút rất nhiều sự chú ý.

Trong xác minh chi tiết hơn, việc trộn và kết hợp thường là lý tưởng: RNM cho một số khối tương tự nhất định về tốc độ và mức SPICE trong đó độ chính xác là quan trọng, chẳng hạn như trong phân tích độ nhạy đối với sự thay đổi điện áp nguồn và nhiệt độ, nằm ngoài phạm vi phân tích RNM.

Xây dựng mô hình

Tất cả điều này nghe có vẻ tuyệt vời, nhưng những mô hình này đến từ đâu? Loại mạng cơ bản rất linh hoạt nhưng ở mức độ rất thấp đòi hỏi sự đầu tư đáng kể từ một nhà thiết kế tương tự không quen thuộc với SystemVerilog. Cadence có thư viện tiêu chuẩn EEnet gồm các mạch cơ sở thông thường (như tụ điện, điốt, cuộn cảm, thiết bị MOS), cũng như thư viện thử nghiệm các mô-đun tín hiệu hỗn hợp hiển thị các ví dụ về cách sử dụng các thành phần này. Các nhà thiết kế có thể xây dựng các thành phần phức tạp hơn bằng cách sử dụng các thành phần này theo sơ đồ.

Shekar nói với tôi rằng làm việc với khách hàng ngay từ những ngày đầu của EEnet, thư viện cơ sở này rất ổn định và gần đây đã được phát hành như một phần của Ứng dụng Tín hiệu Hỗn hợp Xcelium. Cadence hiện đang nghiên cứu xây dựng và xem xét một số thành phần cấp trung (như PLL, bộ điều chỉnh điện áp, ADC, DAC). Khách hàng của họ cũng đang xây dựng các thành phần cấp trung của riêng mình, thậm chí còn mở rộng hơn nữa cho các chức năng phức tạp hơn. Có vẻ như sự cần thiết đang thúc đẩy tiến độ hơn là chờ đợi các thư viện được đóng gói sẵn.

Lạc đề nhanh chóng về tiêu chuẩn hóa do nỗ lực đáng kể được dành cho việc xây dựng các mô hình. Lu Dai (chủ tịch Accellera) nói với tôi tại DVCon năm nay rằng nhóm làm việc về tín hiệu hỗn hợp Accellera rất tích cực và nhu cầu từ người dùng rất lớn. Cadence là một bên tham gia và đã có danh tiếng trong lĩnh vực này, vì vậy tôi cho rằng các bản phát hành của họ có thể gần giống với bất kỳ điều gì đã được thống nhất cuối cùng trong tiêu chuẩn. Tuy nhiên, Lu cảnh báo rằng một số yêu cầu cập nhật tín hiệu hỗn hợp SV đang di chuyển chậm do tiêu chuẩn SV hiện thuộc IEEE nơi không thường xuyên cập nhật. Accellera đang xem xét cách giải quyết.

Tự động hóa testbench, xác nhận, phạm vi bảo hiểm, v.v.

Thông lượng mô phỏng cao hơn luôn là mục tiêu quan trọng nhưng các nhóm xác minh tín hiệu hỗn hợp cần nhiều hơn thế. Họ muốn khả năng tự động hóa mà các đồng nghiệp kỹ thuật số của họ thường xuyên sử dụng và đã nỗ lực vận động hành lang để mở rộng những tính năng này sang tín hiệu hỗn hợp. Một nhóm làm việc UVM-AMS dưới sự chỉ đạo của Accellera đã được tiến hành nhằm mục đích này. Một tiêu chuẩn vẫn chưa được ban hành và cũng đang phải vật lộn với các vấn đề về lịch trình, nhưng chúng đang đi đúng hướng.

Trong khi chờ đợi, các nhà thiết kế và người xác minh đáp ứng những nhu cầu này thông qua các luồng độc quyền; Tôi tưởng tượng những điều này cũng đang theo dõi tiêu chuẩn đang phát triển. Cadence hỗ trợ xác minh theo chỉ số trên kỹ thuật số và analog thông qua các bảng kiểm tra UVM, xác nhận thông thường và xác nhận tín hiệu hỗn hợp phức tạp, cùng với ngẫu nhiên hóa. Đối với tín hiệu tương tự thuần túy, phạm vi phủ sóng và trạng thái khác có thể được nhập từ Trình xác minh Virtuoso ADE vào vManager.

Tóm lại, đã có những tiến bộ đáng kể trong việc xác minh tín hiệu hỗn hợp và có hy vọng về sự tiến bộ thông qua việc tiêu chuẩn hóa. Xác minh tín hiệu hỗn hợp thực sự đang trở thành đối tác hạng nhất với xác minh kỹ thuật số. Bạn có thể biết thêm thông tin về ứng dụng Tín hiệu hỗn hợp Xcelium nhấp vào ĐÂY , trình mô phỏng Spectre FX nhấp vào ĐÂY và hội thảo trực tuyến hữu ích về tín hiệu hỗn hợp nhấp vào ĐÂY .

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Ô tô / Xe điện, Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- ChartPrime. Nâng cao trò chơi giao dịch của bạn với ChartPrime. Truy cập Tại đây.

- BlockOffsets. Hiện đại hóa quyền sở hữu bù đắp môi trường. Truy cập Tại đây.

- nguồn: https://semiwiki.com/eda/334146-mixed-signal-verification-is-growing-in-importance/