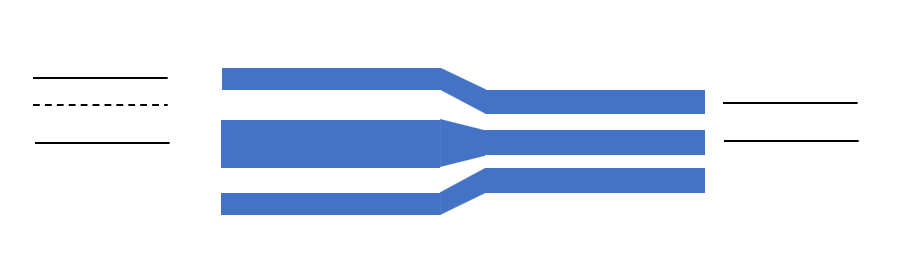

On a DRAM chip, the patterning of features outside the cell array can be just as challenging as those within the array itself. While the array contains features which are the most densely packed, at least they are regularly arranged. On the other hand, outside the array, the regularity is lost, but the in the most difficult cases, the pitches can still be comparable with those within the array, though generally larger. Such features are the lowest metal lines in the periphery for the sense amplifier (SA) and sub-wordline driver (SWD) circuits. A key challenge is that these lines are meandering in appearance, and the pitch is varying over a range (Figure 1). The max/min pitch ratio can range ~1.4 to 2. The imaging performances of two or more pitches together cannot be judged from the imaging performance of each of those pitches by themselves.

Figure 1. Varying pitch in metal lines in DRAM periphery. From the right, the pitch is at a minimum, but from the left, it is nearly twice the minimum pitch.

The image of lines for a fixed pitch is constructed from the interference of at least two beams that emerge from the pupil and go through the final objective with numerical aperture NA. The maximum phase error between any two of the beams affects the degradation of the image as it goes out of focus. In an EUV system with 0.33 NA, a 44 nm pitch image can only be formed from two beams, while the 66 nm pitch can be formed from two, three, or four beams. Figure 2 shows the interesting result that the two-beam image has the lowest maximum phase error. This underlies the existence of forbidden pitches with dipole illumination [1]. This has driven the two-mask exposure approach [2].

Figure 2. Phase errors for various images at 66 nm pitch vs 44 nm pitch under 45 nm defocus in a 0.33 NA EUV system. Two-beam images give the least phase error.

Unfortunately, only 10% of the pupil in the 0.33 NA EUV system supports two-beam imaging for both 44 nm and 66 nm pitches (Figure 3). Light cut out at the condenser reduces the light available for exposure [3]. The usable pupil fill is further reduced to 0 by considering pupil rotation across slit [4].

Figure 3. Portion of 0.33 NA EUV pupil supporting two-beam imaging for 44 nm and 66 nm pitches, at slit center (blue) and slit edge (orange) after 18 deg rotation. No part of the pupil supports the imaging consistently across slit.

It gets worse for the High-NA 0.55 NA EUV system, as there will definitely be at least three beams emerging from the pupil and the depth of focus is reduced further by the higher NA.

If a DUV 1.35 NA system were used instead, double patterning is necessary to achieve both 44 nm and 66 nm pitches. Thus, 88 nm and 132 nm pitches will be actually exposed. Both of these use two-beam imaging, which bodes well for finding illumination that has sufficient depth of focus for both pitches (Figure 4).

Figure 4. Phase errors for 88 nm and 132 nm pitches under 45 nm defocus in an 1.35 NA ArF (DUV) system, for an optimized dipole illumination shape (inset).

At this point, we can generalize to set some lithographic requirements for metal line patterning for SA and SWD circuits. In order to maintain two-beam imaging, the maximum-to-minimum pitch ratio should be <2, corresponding to half-pitch k1=0.5 and k1=0.25, respectively. For a max/min pitch ratio of 1.5, current 1.35 NA DUV systems can support down to 80 nm minimum pitch, 120 nm maximum pitch without double patterning. Once double patterning is used, however, the maximum line pitch should not exceed ~90 nm. The max/min pitch ratio may need to be correspondingly adjusted. Due to the meandering nature of the metal lines, it would not be unreasonable to have, for example, 3 metal lines (2 pitches) in one section span the same extent as 4 metal lines (3 pitches) in another section. This even-odd disparity could be resolved by splitting and stitching the odd metal feature, as shown in Figure 5 [5,6].

Figure 5. Splitting a layout containing even and odd numbers of lines can be resolved by splitting the odd feature to be stitched back together with the double patterning.

When the minimum line pitch gets smaller than ~40 nm (beyond 13nm DRAM node [7]), we should expect the DUV double patterning to become quadruple patterning (Figure 6). But why not consider EUV single exposure patterning?

Figure 6. Quadruple patterning (with a 1.35 NA DUV system); each color represents a separate exposure.

An additional consideration for SA and SWD metal patterning is that the layout requires two dimensions to accommodate the perpendicular bit line and word line directions. This entails the use of X+Y dipole, or cross-dipole illumination, which will restrict the mask types used. Essentially, the illumination can only support pitches in one orientation, and degrades pitches with the other orientation. Masks without pre-designed phase shifts (aka binary masks) suffer from a drop in an unwanted drop in normalized image log slope (NILS) (Figure 7). EUV currently contends with a lack of the necessary phase-shift masks [8,9]. Hence, two exposures (each already more than the cost of two DUV exposures [10]), one for X orientation, one for Y orientation, would be required.

Figure 7. Cross-dipole illumination reduces NILS for 2-beam imaging with binary masks.

DUV attenuated phase-shift masks (attPSMs) can be designed with 180 deg phase shifts between the bright and dark regions, mitigating this issue (Figure 8).

Figure 8. Cross-dipole illumination still reduces NILS for 2-beam imaging with attPSM masks, but the value stays above 2.

The scenarios described above are summarized in the table below.

Table 1. Scenarios for SA and SWD minimum pitch metal patterning in DRAM.

References

[1] M. Eurlings et al., Proc. SPIE 4404, 266 (2001).

[2] D. Nam et al., Proc. SPIE 4000, 283 (2000).

[3] M. van de Kerkhof et al., Proc. SPIE 10143, 101430D (2017).

[4] A. Garetto et al., J. Micro/Nanolith. MEMS MOEMS 13, 043006 (2014).

[5] Y. Kohira et al., Proc. SPIE 9053, 90530T (2014).

[6] S-Min Kim et al., Proc. SPIE 6520, 65200H (2007).

[7] J. Lee et al., Proc. SPIE 12495, 124950S (2023).

[8] F. Chen, “Phase Shifting Masks for NILS Improvement – A Handicap For EUV,” https://www.linkedin.com/pulse/phase-shifting-masks-nils-improvement-handicap-euv-frederick-chen

[9] A. Erdmann, H. Mesilhy, and P. Evanschitkzy, J. Micro/Nanopatterning, Materials, and Metrology 21, 020901 (2022).

[10] L. Liebmann, A. Chu, and P. Gutwin, Proc. SPIE 9427, 942702 (2015).

This article first appeared in LinkedIn Pulse: Application -Specific Lithography: Sense Amplifier and Sub-Wordline Driver Metal Patterning in DRAM

Also Read:

BEOL Mask Reduction Using Spacer-Defined Vias and Cuts

Predicting Stochastic Defectivity from Intel’s EUV Resist Electron Scattering Model

China’s hoard of chip-making tools: national treasures or expensive spare parts?

Share this post via:

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiwiki.com/lithography/339965-application-specific-lithography-sense-amplifier-and-sub-wordline-driver-metal-patterning-in-dram/