Trong nhiều năm nay, tôi đã gặp AMIQ EDA đồng sáng lập Cristian Amitroaie vài tháng một lần để thảo luận về tình trạng của ngành, các xu hướng chính trong thiết kế và xác minh cũng như những cách chúng giúp tạo điều kiện và đẩy nhanh quá trình phát triển chip. Tôi nhận thấy một tính năng mới thú vị được đề cập trong tài liệu mới nhất của họ nhấn phát hành, vì vậy tôi đã hỏi Cristian để biết thêm thông tin. Điều này dẫn đến một cuộc thảo luận sôi nổi và thú vị.

Hầu hết các nhà thiết kế và kỹ sư xác minh đều viết mã của họ trong SystemVerilog ngày nay, nhưng vẫn có những trường hợp ngoại lệ. Một số tận dụng các công cụ tổng hợp cấp cao (HLS) để thiết kế bằng SystemC hoặc các ngôn ngữ khác trừu tượng hơn một chút so với SystemVerilog. Những người khác viết bằng ngôn ngữ riêng của họ và sử dụng các công cụ tùy chỉnh để tạo các tệp SystemVerilog dùng để mô phỏng, xác minh chính thức, tổng hợp và các bước khác trong quá trình phát triển.

Cristian nói rằng đôi khi họ thấy một nền tảng trung gian trong đó các kỹ sư viết mã chủ yếu là SystemVerilog nhưng cũng chứa các câu lệnh “tiền xử lý” bằng các ngôn ngữ đã được thiết lập như thư viện Jinja2 của Perl và Python hoặc bằng các ngôn ngữ độc quyền. Họ sử dụng các tập lệnh để xử lý các tệp này và tạo các tệp SystemVerilog thuần túy cho phần còn lại của quy trình. Tôi đã hỏi Cristian việc sử dụng bộ tiền xử lý sẽ thay đổi cách các kỹ sư sử dụng môi trường phát triển tích hợp (IDE) như thế nào.

Tôi được biết rằng người dùng Công cụ xác minh và thiết kế AMIQ EDA (DVT) Gia đình IDE muốn có quyền truy cập vào tất cả các tính năng yêu thích của họ ngay cả khi chỉnh sửa tệp bằng mã tiền xử lý. Nhóm AMIQ EDA đã phát triển các phương pháp phỏng đoán thông minh để kích hoạt đầy đủ các khả năng của IDE khi chỉnh sửa các tệp như vậy, giống như cách họ thực hiện với SystemVerilog thuần túy. Các tính năng này bao gồm siêu liên kết điều hướng, tự động hoàn thành, phát hiện lỗi nhanh chóng, sửa lỗi nhanh, tái cấu trúc và tất cả các chức năng nâng cao mà người dùng DVT IDE yêu thích.

Điều này thật hấp dẫn đối với tôi. Chúng ta đang nói về việc “hiểu” các tệp ngôn ngữ hỗn hợp, thực sự không phải là điều mà bất kỳ trình biên dịch nào cũng có thể dễ dàng hiểu được. Để đảm bảo rằng tôi hiểu đúng và đây là sự thật, Cristian đã mời Zeljko Zurzic, trưởng nhóm điều phối việc phát triển khả năng này, để giải thích cách thức hoạt động của nó. Ông nói rằng tất cả những gì người dùng cần làm là thông báo cho DVT IDE về việc ánh xạ giữa các tệp chứa các câu lệnh tiền xử lý (“tệp p”) và các tệp được tạo (“tệp g”).

Điều này được thực hiện bằng cách sử dụng các chỉ thị trình biên dịch chuyên dụng hỗ trợ các trường hợp sử dụng khác nhau. Ví dụ: có một cách để yêu cầu trình biên dịch DVT IDE “tìm ra tệp p tương ứng từ nhận xét tiêu đề tệp g”. Sau khi hoàn tất việc này, người dùng chỉ cần chỉnh sửa các tệp p của họ như thể không có gì đặc biệt về chúng. Quá trình biên dịch gia tăng nhanh chóng sẽ gắn cờ bất kỳ lỗi SystemVerilog nào khi chúng nhập, các siêu liên kết đưa chúng đi xung quanh mã, tính năng tự động hoàn thành và tái cấu trúc hoạt động tốt, chúng có thể yêu cầu nhiều sơ đồ khác nhau, v.v.

Các phần chứa mã tiền xử lý được đánh dấu rõ ràng để người dùng biết chúng sẽ được chuyển thành mã SystemVerilog. TRONG IDE Eclipse DVT họ có thể xem cách tạo mã bằng cách sử dụng Chế độ xem Kiểm tra; TRONG DVT IDE cho Mã VS họ có thể “nhìn trộm” các biến đổi. DVT IDE có thể được cấu hình để tự động chạy tập lệnh tiền xử lý bất cứ khi nào mã tiền xử lý được thay đổi. Người dùng có thể dễ dàng so sánh file ap với file g tương ứng nếu muốn.

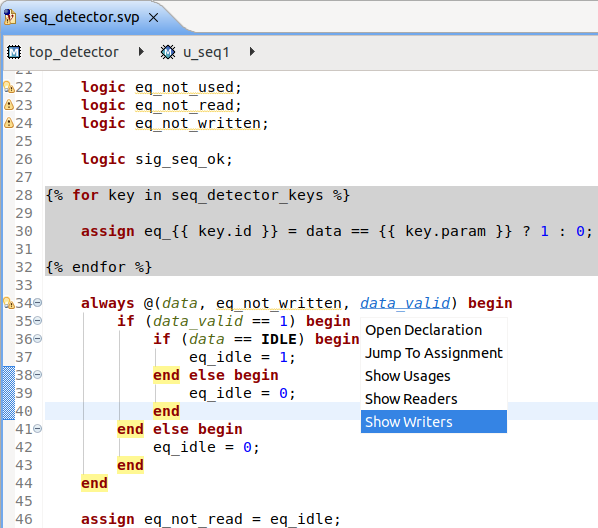

Zeljko đã cung cấp ba ảnh chụp màn hình cho thấy khả năng mới này đang hoạt động. Tệp đầu tiên bên dưới hiển thị một tệp trong DVT Eclipse IDE bao gồm câu lệnh tiền xử lý Jinja2. Bất chấp sự hiện diện của mã không phải SystemVerilog này, người dùng vẫn có thể tận dụng tính năng “Show Writers” mạnh mẽ để nhanh chóng hiểu cách một biến được điều khiển. Các lỗi biên dịch và cảnh báo được chỉ định ở cột ngoài cùng bên trái của màn hình.

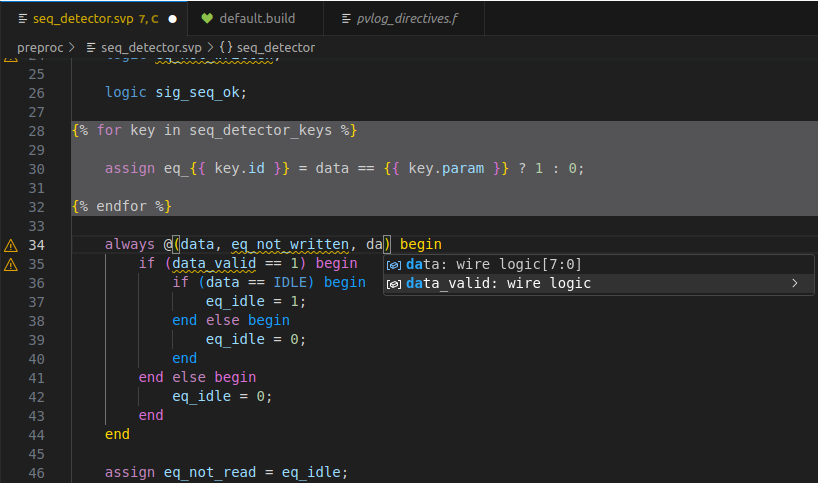

Ảnh chụp màn hình bên dưới hiển thị cùng một tệp trong DVT IDE cho VS Code, hiển thị các vấn đề về trình biên dịch ở cột bên trái và cho phép sử dụng tính năng tự động hoàn thành. Điều này cho thấy ngay cả những hàm DVT tiên tiến nhất cũng có sẵn trong mã với các câu lệnh tiền xử lý.

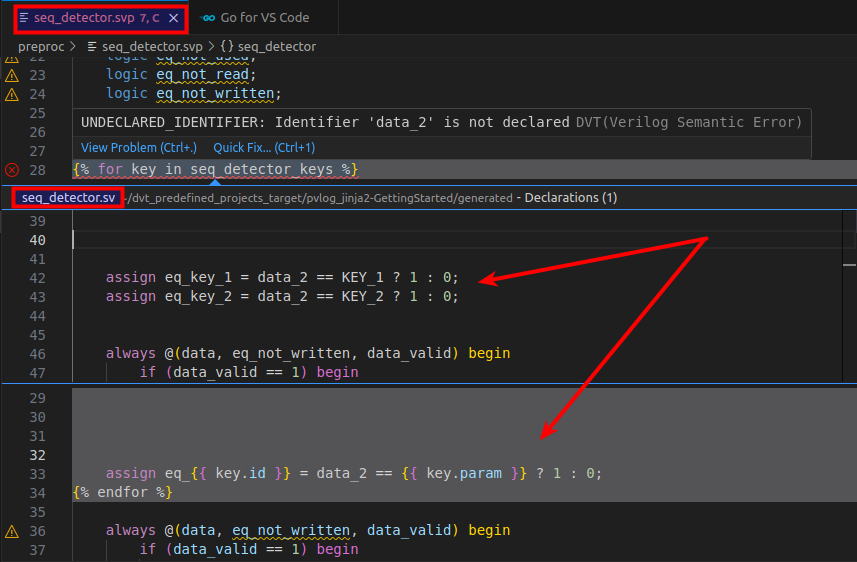

Zeljko nhấn mạnh rằng IDE kiểm tra mã SystemVerilog được tạo, điều này quan trọng vì có thể có lỗi trong câu lệnh tiền xử lý hoặc lỗi trong tập lệnh tiền xử lý. Ảnh chụp màn hình bên dưới chỉ hiển thị một ví dụ như vậy. Mã SystemVerilog được tạo chứa một biến chưa được xác định trong tệp nguồn. DVT IDE hiển thị lỗi biên dịch, tệp p và mã được tạo trong tệp g.

Việc xem các tệp g có thể hữu ích trong việc gỡ lỗi, nhưng điểm mấu chốt là người dùng phải làm việc trực tiếp với các tệp p, phân tích và chỉnh sửa chúng bằng một IDE mạnh mẽ. Các tệp g được gắn thẻ là “chỉ đọc” và người dùng sẽ được cảnh báo nếu chúng bị sửa đổi. Tôi rất vui khi nghe điều này; tất cả chúng ta đều biết rằng thực hiện các thay đổi thủ công đối với bất kỳ tệp nào sẽ bị ghi đè bởi quá trình tạo mã là một ý tưởng thực sự tồi.

Cuối cùng, Cristian nhấn mạnh rằng toàn bộ mục đích của tính năng mới này là người dùng có thể chỉnh sửa mã bằng các câu lệnh tiền xử lý giống như thể nó là SystemVerilog thuần túy. Việc biến điều này thành hiện thực là nỗ lực đáng kể của một số khách hàng chủ chốt dựa vào các luồng dựa trên bộ tiền xử lý. Tôi cảm ơn Zeljko và Cristian vì những lời giải thích và thời gian của họ.

Nếu bạn muốn tìm hiểu thêm về cách sử dụng các tệp tiền xử lý hoặc bất kỳ khía cạnh nào của giải pháp AMIQ EDA, bạn có thể ghé thăm chúng tại Gian hàng 107 tại Hội nghị và Triển lãm Thiết kế và Xác minh (DVCon) Hoa Kỳ tại San Jose, California vào ngày 5 tháng 6 và ngày XNUMX tháng XNUMX.

Cũng đọc:

Triển vọng 2024 với Cristian Amitroaie, Người sáng lập và Giám đốc điều hành của AMIQ EDA

Sử dụng Linting để viết mã Testbench không có lỗi

AMIQ: Kỷ niệm 20 năm hoạt động trong lĩnh vực Tư vấn và EDA

Chia sẻ bài đăng này qua:

- Phân phối nội dung và PR được hỗ trợ bởi SEO. Được khuếch đại ngay hôm nay.

- PlatoData.Network Vertical Generative Ai. Trao quyền cho chính mình. Truy cập Tại đây.

- PlatoAiStream. Thông minh Web3. Kiến thức khuếch đại. Truy cập Tại đây.

- Trung tâmESG. Than đá, công nghệ sạch, Năng lượng, Môi trường Hệ mặt trời, Quản lý chất thải. Truy cập Tại đây.

- PlatoSức khỏe. Tình báo thử nghiệm lâm sàng và công nghệ sinh học. Truy cập Tại đây.

- nguồn: https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/