チップレットは自動車市場で再び注目を集めており、電動化の進展と激しい競争により、企業は設計と生産スケジュールの加速を余儀なくされています。

電動化は、非常に短い市場ウィンドウと絶えず変化する要件に直面して、競争力を維持するのに苦労しているいくつかの最大手で最も有名な自動車メーカーに火をつけました。自動車メーカーが通常 5 ~ 7 年の設計サイクルで運営していた過去とは異なり、今日の自動車の最新テクノロジーは数年以内に時代遅れになると考えられるかもしれません。そして、彼らが追いつけないとしても、ソフトウェアのアップデートと同じくらい早く機能を更新したり変更したりできる機能を備えた安価な車両を製造する新興企業がまったく新しい存在となる。

しかし、ソフトウェアには速度、セキュリティ、信頼性の制限があり、ハードウェアをカスタマイズできることに多くの自動車メーカーが現在力を入れています。ここにチップレットが適しており、現在焦点は、これをプラグアンドプレイ市場にするために、大規模なエコシステム間で十分な相互運用性を構築する方法にあります。自動車用チップレットの相互運用性を可能にする重要な要素には、標準化、相互接続技術、通信プロトコル、電力と熱の管理、セキュリティ、テスト、エコシステムのコラボレーションが含まれます。

基板レベルでの非自動車アプリケーションと同様に、多くの設計作業はダイツーダイのアプローチに焦点を当てており、これにより多くの新しい設計上の考慮事項とトレードオフが生じています。チップ レベルでは、設計パフォーマンス要件の増加により、さまざまなプロセッサ、チップ、メモリ、I/O 間の相互接続がより複雑になり、標準化活動が急増しています。さまざまな目的に応えるために、さまざまな相互接続およびインターフェイスのタイプが提案されていますが、 チップレット 専用機能 (プロセッサ、メモリ、I/O など) のテクノロジは、チップ設計へのアプローチを変えています。

「自動車 OEM 各社は、自らの運命をコントロールするには、自社の SoC をコントロールする必要があるという認識を持っています」と、シーメンス EDA の仮想およびハイブリッド システム担当バイスプレジデントであるデビッド フリッツ氏は述べています。 「しかし、彼らは、1982 年に大学に通っていた頃から EDA がどれほど進歩したかを理解していません。また、マスク セットには 100 億ドルかかる最新のプロセス ノードに行く必要があると信じています。彼らにはそんな余裕はない。また、人材プールがかなり小さいため、人材にアクセスすることもできません。これらすべてを総合すると、OEM 企業は、自社の運命をコントロールするには、他社が開発したテクノロジーが必要であるという認識に至ります。ただし、そのテクノロジーは必要に応じて組み合わせることができ、少なくとも少数の企業にとっては将来も使用できると確信している独自の差別化された製品を実現できます。モデル年。そうすれば経済的にも成り立ちます。この法案に適合する唯一のものはチップレットです。」

チップレットは特定の機能に合わせて最適化できるため、自動車メーカーは複数の車両設計で実証済みのテクノロジーを使用して信頼性、安全性、セキュリティ要件を満たすことができます。さらに、市場投入までの時間を短縮し、最終的にはさまざまな機能のコストを削減できます。

チップの需要は過去 49.8 年間で増加しています。 Allied Market Research によると、世界の自動車用チップの需要は 2021 年の 121.3 億ドルから 2031 年までに XNUMX 億ドルに増加すると予想されています。この成長はさらに多くの自動車用チップのイノベーションと投資を呼び込むことになり、チップレットは大きな恩恵を受けると予想されています。

しかしチップレットの市場が成熟するには時間がかかり、段階的に展開される可能性が高い。最初は、ベンダーがさまざまな種類の独自のダイを提供します。その後、一部のベンダーですでに行われているように、パートナーは協力してチップレットを供給して相互にサポートすることになります。最終段階は、UCIe またはその他の相互接続スキームによってサポートされる、普遍的に相互運用可能なチップレットになります。

最終段階に到達するのが最も難しく、大幅な変更が必要になります。相互運用性を確保するには、ハードウェアとソフトウェアの開発者、ファウンドリ、OSAT、材料と機器のサプライヤーを含む、自動車エコシステムとサプライ チェーンの十分な規模の部分が団結する必要があります。

勢いが増している

プラスの面としては、すべてがゼロから始まるわけではありません。ボード レベルでは、モジュールとサブシステムは常にオンボードのチップ間インターフェイスを使用しており、今後も使用し続けるでしょう。 Cadence、Diode、Microchip、NXP、Renesas、Rambus、Infineon、Arm、Synopsys などのさまざまなチップおよび IP プロバイダーが、インターフェース シリコンを作成するための既製のインターフェース チップまたは IP を提供しています。

Universal Chiplet Interconnect Express (UCIe) コンソーシアム は、ダイツーダイのオープン相互接続規格の推進力です。このグループは、1.1 年 2023 月に最新の UCIe XNUMX 仕様をリリースしました。理事会メンバーには、Alibaba、AMD、Arm、ASE、Google Cloud、Intel、Meta、Microsoft、NVIDIA、Qualcomm、Samsung などが含まれます。業界パートナーは幅広いサポートを示しています。 AIB や Bunch of Wires (BoW) も提案されています。さらに、Arm は独自のチップレット システム アーキテクチャと、チップレットのプロトコルを標準化するための更新された AMBA 仕様をリリースしたばかりです。

ケイデンスのデザインIP担当シニアプロダクトマーケティンググループディレクターのアリフ・カーン氏は、「チップレットは必要性に駆られてすでに登場している」と語った。 「プロセッサーと SoC のサイズが拡大し、レチクルの限界に達し、規模の不経済が生じています。プロセス技術の進歩による増分利益は、トランジスタおよび設計あたりのコストの上昇よりも低くなります。パッケージング技術 (2.5D/3D) の進歩と、UCIe などのダイツーダイ レベルでのインターフェイスの標準化により、チップレットの開発が促進されるでしょう。」

現在使用されているほぼすべてのチップレットは、Intel、AMD、Marvell などの大手チップメーカーによって自社開発されています。これは、チップレットの特性や動作を厳密に制御できるためです。しかし、この市場をより多くのプレイヤーに開放するための取り組みがあらゆるレベルで進行中です。それが実現すると、中小企業は著名な先駆者がこれまでに達成してきたことを活用し、それらの開発を中心に革新を始めることができます。

「私たちの多くは、既製の相互運用可能なチップレット ポートフォリオを持つという夢は、現実になるまでに何年もかかるだろうと考えています」と Arteris の戦略マーケティング シニア ディレクターの Guillaume Boillet 氏は述べ、相互運用性はパートナーのグループによって生まれるだろうと付け加えました。不完全な仕様のリスクに対処しています。

これにより、現場のハードウェアにレベルのカスタマイズとアップデートを提供できる FPGA と eFPGA の魅力も高まります。 「チップレットは本物です」と Flex Logix の CEO、ジェフ・テイト氏は述べています。 「現時点では、2 つ以上のチップレットを製造している企業は、歩留まりがほとんどないレチクル サイズに近いダイを製造している企業よりもはるかに経済的に運営できます。チップレットの標準化はまだ遠いようです。 UCIeですらまだ規格が定まっていません。 UCIe、ベア ダイ テスト、統合パッケージが動作しない場合の問題の責任者などについては、全員が同意しているわけではありません。UCIe のように規格が流動的なインターフェイスに eFPGA を使用している、または評価している顧客もいます。今すぐシリコンを実装し、後で規格の変更に準拠するために eFPGA を使用できます。」

チップレットをサポートする他の取り組みもありますが、理由はやや異なります。特に、デバイスのスケーリングのコストの上昇と、最先端のノードではレチクルの制約を受けるチップにより多くの機能を組み込む必要性です。しかし、これらの取り組みは自動車におけるチップレットへの道も切り開き、これをすべて機能させるための強力な業界の支援があります。たとえば、SEMI、ASME、および 2.5 つの IEEE 協会の後援の下、新しいヘテロジニアス インテグレーション ロードマップ (HIR) では、さまざまなマイクロエレクトロニクスの設計、材料、およびパッケージングの問題を検討して、半導体業界のロードマップを作成しています。現在の焦点には、3D、XNUMXD-IC、ウェーハレベルのパッケージング、統合フォトニクス、MEMS およびセンサー、システムインパッケージ (SiP)、航空宇宙、自動車などが含まれます。

最近開催されたヘテロジニアス インテグレーション グローバル サミット 2023 では、AMD、Applied Materials、ASE、Lam Research、MediaTek、Micron、Onto Innovation、TSM の代表者が出席しました。Cなどはチップレットに対する強力な支持を示しました。チップレットをサポートする別のグループは、 チップレットデザインエクスチェンジ (CDX) ワーキング グループ。 オープンドメイン固有のアーキテクチャ (ODSA) と Open Compute Project Foundation (OCP)。チップレット設計交換 (CDX) 憲章は、2.5D スタックおよび 3D 集積回路 (3D-IC) の電気的、機械的、および熱的設計交換標準を含む、チップレットとチップレット統合のさまざまな特性に焦点を当てています。その代表者としては、 ANSYS、アプライド マテリアルズ、Arm、Ayar Labs、Broadcom、Cadence、Intel、Macom、Marvell、Microsemi、NXP、Siemens EDA、Synopsys など。

シーメンスのフリッツ氏は、「各チップレットの機能面での自動車会社の要望は依然として激動の状態にある」と指摘した。 「一方の極端にはこれらの問題があり、もう一方の極端にはこれらの問題があります。ここがスイートスポットです。これが必要なのです。そして、これらの企業は、そのような仕事を行うことができ、それらを統合することができます。そうすれば、この相互運用性のことは大したことではありません。 OEM は、「あらゆる可能性のすべてを処理しなければならない」と言って、作業を複雑にしすぎる可能性があります。代替案としては、「高速 PCIe のようなものです」と言えるかもしれません。一方から他方へ通信したい場合、その方法はすでに知っています。オペレーティング システムを実行するドライバーがあります。そうすれば非常に多くの問題が解決されるでしょうし、最終的にはそこに行き着くだろうと私は信じています。」

ユニバーサルチップレット開発への1つの道?

今後、チップレットは自動車業界とチップ業界の両方にとって焦点となり、チップレット IP からメモリの相互接続、カスタマイズのオプションと制限に至るまで、あらゆるものが関係することになります。

たとえば、ルネサス エレクトロニクスは、2023 年 XNUMX 月に次世代 SoC および MCU の計画を発表しました。同社は、高度なパッケージ内チップレット統合テクノロジーを備えた高性能アプリケーション向けの第 XNUMX 世代 R-Car SoC に関する事前情報を含む、自動車デジタル領域全体のすべての主要アプリケーションをターゲットにしています。これは、自動車エンジニアにカスタマイズの柔軟性を提供することを目的としています。彼らのデザイン。

ルネサスは、先進運転支援システム(ADAS)でより多くのAIパフォーマンスが必要な場合、エンジニアはAIアクセラレータを単一チップに統合できる機能を備えていると指摘した。同社によると、このロードマップは、ハードウェアが入手可能になる前でもソフトウェアの設計と検証を行うなど、品質を損なうことなく開発を加速する方法を求めてきたティア1およびOEM顧客との長年にわたる協力と議論の末に策定されたという。

「オンデマンドのコンピューティングを向上させるニーズがますます高まっており、将来の自動車におけるより高いレベルの自律性のニーズが高まっているため、今後数年間、モノリシック ソリューションを拡張し、市場のパフォーマンス ニーズに対応することが課題になると考えています。」と同氏は述べています。ルネサスの SoC ビジネスおよび戦略担当シニア ディレクター、Vasanth Waran 氏は次のように述べています。 「チップレットにより、市場のニーズを超えてコンピューティング ソリューションを拡張できるようになります。」

ルネサスは、 チップレットベースの製品ファミリー 特に2025年以降の自動車市場をターゲットとしています。

標準インターフェイスにより SoC のカスタマイズが可能

現在、ほとんどのチップレットが使用されている標準プロセッサと、車載アプリケーション用に開発されたチップレットとの間にどの程度の重複があるのかは完全には明らかではありません。しかし、このテクノロジーが新しい市場に移行するにつれて、基礎となるテクノロジーと開発は確実に相互に構築されていくでしょう。

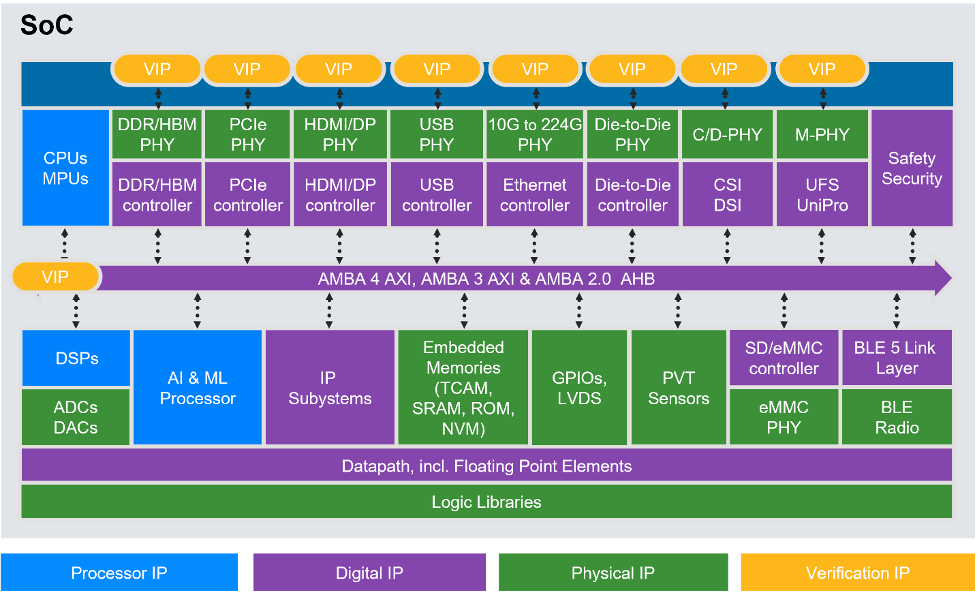

「AI アクセラレータであれ、ADAS 自動車アプリケーションであれ、顧客は標準インターフェイス IP ブロックを必要としています」と、シノプシスの IP アクセラレーション ソリューション グループのシニア プロダクト マネージャーである David Ridgeway 氏は述べています。 「顧客の SoC で使用されるサブシステム コンポーネントをサポートするには、IP カスタマイズ要件に合わせて完全に検証された IP サブシステムを提供することが重要です。カスタマイズと言うとき、過去 10 ~ 20 年の間に、IP がコントローラ側だけでなく PHY 側でもどれほどカスタマイズ可能になったかを理解していないかもしれません。たとえば、PCI Express は PCIe Gen 3、Gen 4、Gen 5、そして Gen 6 に移行しました。コントローラーは、16 つの x8、4 つの xXNUMX、または XNUMX つの xXNUMX など、より小さいリンク幅の複数の分岐モードをサポートするように構成できます。当社のサブシステム IP チームはお客様と協力して、すべてのカスタマイズ要件が確実に満たされるようにします。 AI アプリケーションの場合、パフォーマンス要件を満たすために信号と電力の整合性が非常に重要です。ほぼすべてのお客様は、TPU が XNUMX 秒あたりより多くのトランザクションを処理できるように、可能な限り最高のメモリ帯域幅速度を達成するために限界に挑戦することを求めています。アプリケーションがクラウド コンピューティングまたは人工知能である場合、顧客は可能な限り最速の応答速度を望んでいます。」

図 1: プロセッサ、デジタル、PHY、検証を含む IP ブロックは、開発者が SoC 全体を実装するのに役立ちます。出典: シノプシス

PPA を最適化することは、効率を向上させるという最終的な目標に役立ち、これにより、チップレットは自動車アプリケーションにおいて特に魅力的になります。 UCIe が成熟すると、全体的なパフォーマンスが飛躍的に向上することが期待されます。たとえば、UCIe は、標準パッケージで 28 ~ 224 GB/s/mm、高度なパッケージで 165 ~ 1317 GB/s/mm の海岸線帯域幅を提供できます。これは、20 ~ 100 倍のパフォーマンスの向上を表します。レイテンシーが 20 ナノ秒から 2 ナノ秒に短縮されると、10 倍の改善になります。電力効率が約 10 倍高く、0.5 pJ/b (標準パッケージ) と 0.25 pJ/b (高度なパッケージ) であることも利点です。重要なのは、可能な限りインターフェイスの距離を短くすることです。

チップレット設計を最適化するために、UCIe コンソーシアムはいくつかの提案を提供しています。

- アーキテクチャ上のカットライン (チップレット境界など) を慎重に計画し、電力、遅延、シリコン領域、IP の再利用を最適化します。たとえば、古いノードで他のチップレットを再利用しながら、最先端のプロセス ノードを必要とする 1 つのチップレットをカスタマイズすると、コストと時間が影響を受ける可能性があります。

- パッケージの熱エンベロープ、ホット スポット、チップレットの配置、I/O ルーティングとブレークアウトについて、熱的および機械的なパッケージングの制約を計画する必要があります。

- プロセス ノードは、特に関連する電力供給スキームの観点から慎重に選択する必要があります。

- チップレットおよびパッケージ/組み立て部品のテスト戦略は、シリコンの問題がパッケージに組み立てられた後ではなく、チップレットレベルのテスト段階で確実に検出されるように、事前に開発する必要があります。

まとめ

ダイツーダイインターフェースを標準化するという考えは急速に広まりつつありますが、そこに至るまでの道のりには時間と労力、そしてお互いにあまり話し合うことのない企業間での多大な協力が必要になります。自動車を製造するには、自動車メーカーの決断力が必要です。チップレットを搭載した車両を構築するには、開発者、ファウンドリ、OSAT、材料および機器のサプライヤーを含むエコシステム全体が協力する必要があります。

自動車 OEM は、システムを組み立て、コストを削減する革新的な方法を見つける専門家です。しかし、相互運用可能なチップレットのエコシステムをいかに迅速かつ効果的に構築して活用して、設計サイクルを短縮し、カスタマイズを改善し、完全に設計されテストされるまでに最先端のテクノロジーが時代遅れになる可能性がある世界に適応できるかはまだ分からない。 、消費者が利用できます。

— Ann Mutschler がこのレポートに貢献しました。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/