Bởi Kelly Damalou và Matt Commens

Sự đổi mới trong thiết kế chất bán dẫn ngày nay chủ yếu được thúc đẩy bởi AI/ML, trung tâm dữ liệu, xe điện và xe tự lái, 5G/6G và IoT. Các công nghệ đóng gói dựa trên silicon 2.5 và 3D-IC được phát triển gần đây đã nâng cao trình độ nghệ thuật ngoài các công nghệ SoC vốn lần đầu tiên kết hợp các chức năng kỹ thuật số, analog và bộ nhớ trên một con chip vào những năm 90. Những công nghệ đóng gói tiên tiến này đã mang lại sự tái sinh hiệu quả của Định luật Moore vốn đã bị chậm lại trong những năm gần đây do những hạn chế đối với kích thước tính năng của bóng bán dẫn do tác động nhiệt. và hiệu ứng lượng tử trong silicon.

Đạt được mức tăng mong muốn về chức năng và hiệu suất đòi hỏi phải vượt qua một loạt thách thức về kỹ thuật, thiết kế và sản xuất. Những vấn đề từng là quy mô PCB giờ đây được dồn vào một thiết bị xếp chồng lên nhau hoặc được kết nối với nhau, dẫn đến yếu tố hình thức nhỏ hơn mong muốn và tiềm năng tăng hiệu suất nhưng đi kèm với những thách thức về tính toàn vẹn của tín hiệu và nguồn cùng với các hiệu ứng nhiệt và cơ học. Sự kết hợp của những thách thức này cuối cùng đòi hỏi phải sử dụng mô hình và mô phỏng đa môi trường.

Bộ xen kẽ là một cách tiếp cận mới đối với việc đóng gói vi mạch và thường được thiết kế và sản xuất theo quy trình silicon. Các thiết bị xen kẽ được xem là một con đường quan trọng phía trước để cung cấp công nghệ 3D-IC và hiện là một lĩnh vực hoạt động sôi nổi trong thiết kế và mô phỏng. Một trong những ưu điểm của việc sử dụng silicon làm chất nền là khả năng hỗ trợ các tính năng tiêu chuẩn của chip như dấu vết kim loại và vias, trái ngược với các công nghệ hữu cơ, sự phù hợp nhiệt của nó với khuôn có khả năng giải quyết nhiều vấn đề về nhiệt.

Có một số kỹ thuật số để giải quyết điện từ của bộ xen kẽ và 3D-IC. Cho đến nay, kỹ thuật có mục đích chung nhất trong điện từ là phương pháp phần tử hữu hạn (FEM). FEM được sử dụng rộng rãi và thành công do tính linh hoạt của nó trong cả CAD, xử lý vật liệu và khả năng ứng dụng sẵn sàng cho các giải pháp đa vật lý. Và khi được kết hợp với chia lưới thích ứng tự động dựa trên vật lý, FEM mang đến các giải pháp chính xác và đáng tin cậy. Với điều này, FEM đã được áp dụng trên các tính năng tốt của quy mô chip lên gói, PCB và ăng-ten và khi được mở rộng với các công nghệ bộ giải tiên tiến như phương pháp phân tách miền (DDM) được áp dụng trên phần cứng điện toán hiệu năng cao đàn hồi (HPC), tất cả các con đường lên thông qua các hệ thống lớn. Hơn nữa, FEM có thể được kết hợp với các kỹ thuật quy mô lớn khác như Phương pháp Khoảnh khắc (MoM) hoặc chụp và dội tia (SBR).

Hình 1: Hệ thống đầy đủ trong FEM: Nghiên cứu EMI/EMC từ-gói-điện thoại-buồng-xe-chip.

Khai thác điện từ trên chip đã sử dụng các bộ giải gần như tĩnh trả về các mô hình định dạng SPICE RC (điện trở, điện dung). Những bộ giải này có thể hấp dẫn vì tốc độ và đầu ra mô hình của chúng dễ dàng được sử dụng bởi các bộ giải mạch. Tuy nhiên, đầu ra RC rời rạc của chúng bỏ qua điện cảm và có băng thông tần số hạn chế, do đó chỉ áp dụng được ở các kích thước hình học tương đối nhỏ. Khi kích thước tăng lên, các hiệu ứng sóng đầy đủ trở nên quan trọng, ví dụ như cuộn cảm xoắn ốc phẳng trên chip và balun trong đó biên độ và độ lệch pha cần được xem xét. Một giải pháp phổ biến trong chế độ này là Phương pháp Khoảnh khắc (MoM). MoM có thể hoạt động hiệu quả với giả định về các lớp kim loại rất mỏng trên chất điện môi với phạm vi vô hạn. Tuy nhiên, những giả định này bị phá vỡ do kích thước của tính năng đã bị thu hẹp và các lớp kim loại không còn xuất hiện mỏng và 2D nữa mà là 3D ở gần các dây dẫn lân cận. Trong “chế độ 3D” này, các phần tử 1D và 2D do MoM triển khai gặp khó khăn trong việc nắm bắt đầy đủ các tác động ghép nối từ các dây dẫn lân cận trên cùng một lớp hoặc các lớp liền kề tác động đến dòng điện tử. Điều này ảnh hưởng trực tiếp đến bản thân dấu vết và điện dung và độ tự cảm lẫn nhau, điều quan trọng đối với hệ số chất lượng chính xác, Q. Các phương pháp như Phương pháp đa cực nhanh (FMM) bỏ qua việc ghép các phần tử cách xa nhau để cải thiện tốc độ và công suất của MoM, nhưng tính toán bị tổn hại của khớp nối yếu này là một vấn đề. Mặt khác, PEEC-RWC tính toán khớp nối giữa tất cả các phần tử lưới, do đó có thể dự đoán rất chính xác khớp nối yếu ngay cả ở tần số cao nhất.

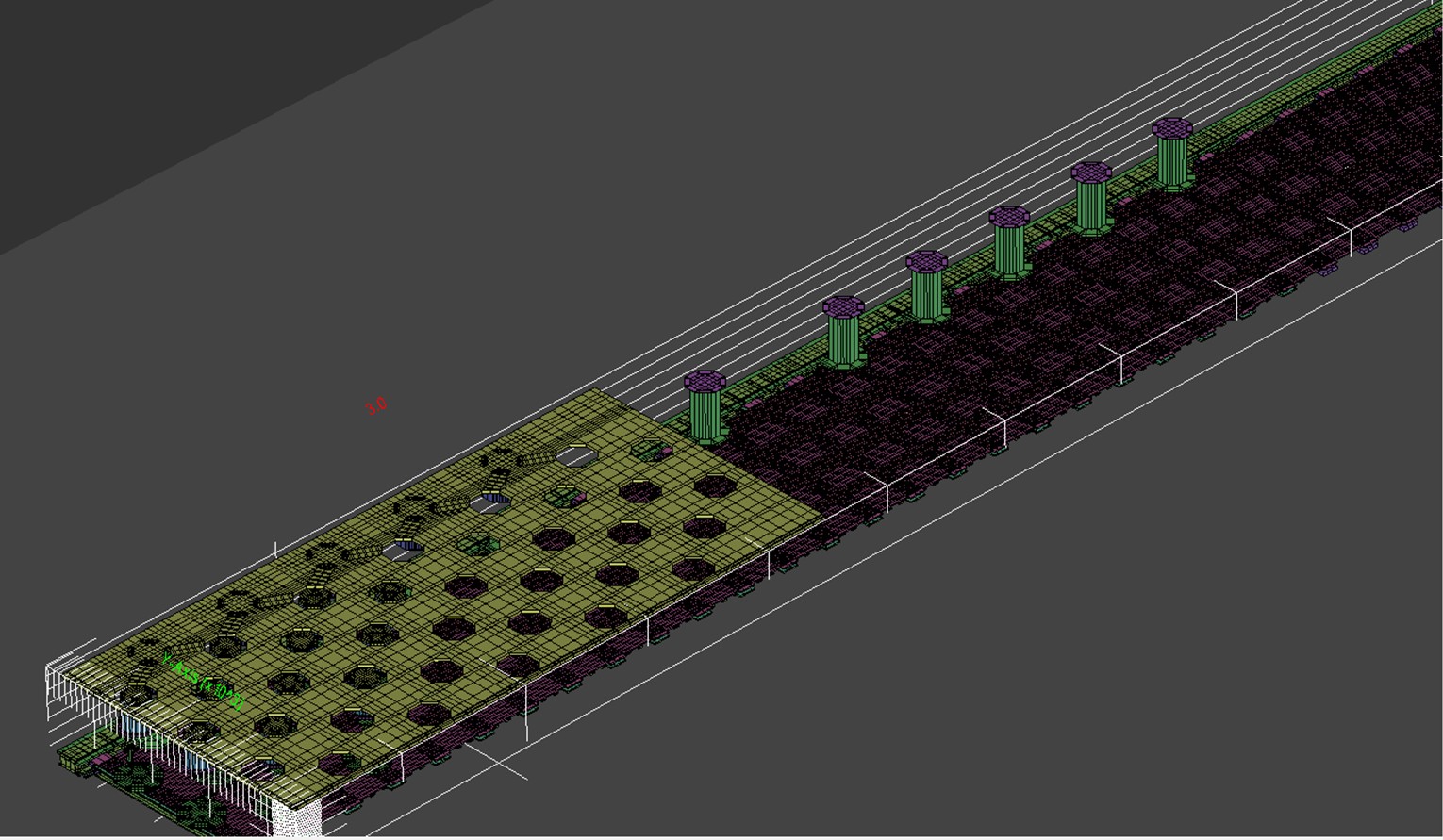

Chuyển sang các bộ xen kẽ dựa trên silicon, theo bản chất thiết kế, mục đích và sản xuất của chúng, chúng nằm trong một chế độ vật lý trong đó mô hình RLC gần như tĩnh sẽ không có đủ băng thông, bộ giải MoM sẽ gặp vấn đề về độ chính xác và không hiệu quả theo bộ xen kẽ bản chất 3D và khi có thể không cần đến sự nghiêm ngặt về mục đích chung của FEM. Đây là một tập hợp các kỹ thuật kết hợp được gọi là mạch tương đương phần tử (PEEC) và điện dung đi bộ ngẫu nhiên (RWC) có thể cùng nhau trích xuất, một cách rất hiệu quả, các mô hình điện từ toàn sóng có độ chính xác cao.

Hình 2: Lưới PEEC của interposer với 48 đường tín hiệu và mạng phân phối điện.

PEEC-RWC đạt được hiệu suất này thông qua việc tạo ra mô hình RLCk phân tán, thông qua các kỹ thuật giảm thứ tự mô hình (MOR) hỗ trợ HPC tiên tiến, có thể trích xuất mô hình toàn sóng rất nhanh. Ngoài ra, có thể mở rộng PEEC-RWC để xử lý các hiệu ứng phụ thuộc bố cục (LDE) phổ biến ở kích thước tính năng nhỏ của các quy trình bán dẫn hiện đại. Và PEEC-RW hoàn toàn không bị giới hạn trong việc giải quyết các bộ xen kẽ, nó cũng có thể mô hình hóa các thành phần rời rạc như cuộn cảm xoắn ốc và balun theo cách hiệu quả tương tự. Ngoài ra, mô hình thiết bị riêng biệt không bị giới hạn ở một hoặc một vài thành phần. Bộ giải PEEC-RW có thể thực hiện mô phỏng được ghép nối đầy đủ trên nhiều thiết bị ở quy mô chẳng hạn như có thể tìm thấy trong bộ thu phát RF đa kênh.

Hình 3: Bộ thu phát RF với nhiều đài ở ngoại vi.

Ngoài những cân nhắc về bộ giải là khả năng sử dụng chúng một cách hiệu quả của người dùng. Tuy nhiên, bộ giải mạnh mẽ đến đâu, việc người dùng không thể truy cập chức năng sẽ hạn chế tính hữu dụng của nó. Việc có các nền tảng bao gồm nhiều quy trình công việc như IC hoặc gói/PCB/hệ thống phục vụ cho bộ kỹ năng kỹ thuật phù hợp là rất quan trọng để cho phép các kỹ thuật này đáp ứng các nhu cầu khác nhau của ngành và trao quyền cho các kỹ sư cung cấp các giải pháp tiên tiến cho thị trường của họ.

3D-IC sẽ là một công nghệ tiên tiến và thú vị trong nhiều năm nữa. Đa vật lý tính toán đã được chứng minh là một phần thiết yếu của các phương pháp thiết kế và xác minh khác nhau cũng như các công cụ EDA liên quan để phát triển các thiết bị đó và nó đang tham gia vào các lĩnh vực công nghệ tiên tiến khác bao gồm lĩnh vực mô phỏng này để tạo nguyên mẫu ảo cho các sản phẩm và hệ thống người dùng cuối của họ .

Ansys sẽ thường xuyên thảo luận về mô phỏng điện từ và đa vật lý tính toán cho 3D-IC trong năm tới. Bạn có thể tham gia thảo luận tại các liên kết dưới đây. Hãy theo dõi để biết thêm thông tin vào năm 2023.

Matt Commens là quản lý cấp cao về quản lý sản phẩm tại Ansys.

Kelly Damalou

(tất cả những bài viết)

Kelly Damalou là giám đốc sản phẩm chính cho danh mục mô phỏng điện từ trên chip của Ansys.

- Coinsmart. Sàn giao dịch Bitcoin và tiền điện tử tốt nhất Châu Âu.Bấm vào đây

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- nguồn: https://semiengineering.com/the-computational-electromagnetics-simulation-challenge-of-3d-ic/