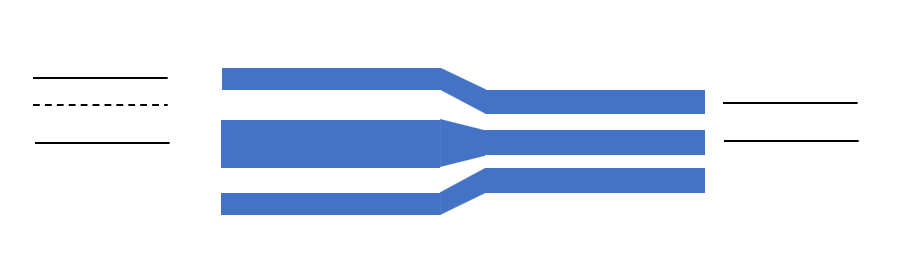

DRAM チップ上では、セル アレイの外側のフィーチャのパターニングは、アレイ自体内のフィーチャのパターニングと同じくらい難しい場合があります。配列には最も高密度にパックされたフィーチャが含まれていますが、少なくとも規則的に配置されています。一方、配列の外側では規則性が失われますが、最も困難なケースでは、ピッチは依然として配列内のピッチと同等ですが、一般的には大きくなります。このような機能は、センスアンプ (SA) およびサブワードラインドライバー (SWD) 回路の周辺部の最も低い金属ラインです。重要な課題は、これらの線が蛇行しているように見え、ピッチが範囲にわたって変化していることです (図 1)。最大/最小ピッチ比は、約 1.4 ~ 2 の範囲にあります。XNUMX つ以上のピッチを合わせた結像性能は、それらの各ピッチの結像性能だけから判断することはできません。

図1. DRAM周辺部の金属線のピッチの変化。右からはピッチが最小ですが、左からは最小ピッチのXNUMX倍近くになります。

固定ピッチのラインの画像は、瞳から出て開口数 NA の最終対物レンズを通過する少なくとも 0.33 つのビームの干渉から構築されます。任意の 44 つのビーム間の最大位相誤差は、焦点が外れるときの画像の劣化に影響します。 NAが66のEUVシステムでは、2nmピッチの画像は1本のビームからのみ形成できますが、2nmピッチの画像はXNUMX本、XNUMX本、またはXNUMX本のビームから形成できます。図 XNUMX は、XNUMX ビーム画像の最大位相誤差が最も低いという興味深い結果を示しています。これは、双極子照明における禁制ピッチの存在の根底にあります [XNUMX]。これにより、XNUMX マスク露光アプローチが推進されました [XNUMX]。

図 2. NA 66 EUV システムにおける 44 nm デフォーカス下での 45 nm ピッチと 0.33 nm ピッチでのさまざまな画像の位相誤差。 XNUMX ビーム画像では位相誤差が最小になります。

残念ながら、NA 10 EUV システムでは、0.33 nm ピッチと 44 nm ピッチの両方で 66 ビーム イメージングをサポートしている瞳は 3% のみです (図 3)。コンデンサーで光が遮断されると、露光に利用できる光が減少します [0]。使用可能な瞳フィルは、スリットを横切る瞳の回転を考慮することによってさらに 4 に減ります [XNUMX]。

図 3. 0.33 nm および 44 nm ピッチの 66 ビームイメージングをサポートする 18 NA EUV 瞳の部分、XNUMX 度回転後のスリット中心 (青) とスリットエッジ (オレンジ)。スリット全体の結像を一貫してサポートする瞳孔の部分はありません。

高NA 0.55 NA EUVシステムでは、少なくともXNUMX本のビームが瞳から出てくることは間違いなく、NAが高くなることで焦点深度がさらに減少するため、状況はさらに悪化します。

代わりに DUV 1.35 NA システムを使用した場合、44 nm と 66 nm の両方のピッチを達成するにはダブルパターニングが必要です。したがって、88 nm および 132 nm ピッチが実際に露光されることになります。これらはどちらも 4 ビーム イメージングを使用しており、両方のピッチに対して十分な焦点深度を持つ照明を見つけるのに適しています (図 XNUMX)。

図 4. 最適化されたダイポール照明形状の、NA 88 ArF (DUV) システムにおける 132 nm デフォーカス下での 45 nm および 1.35 nm ピッチの位相誤差 (挿入図)。

この時点で、SA および SWD 回路の金属線パターニングに関するいくつかのリソグラフィ要件を設定することを一般化できます。 2 ビーム イメージングを維持するには、最大対最小のピッチ比が 1 未満である必要があり、それぞれ半ピッチ k0.5=1 と k0.25=1.5 に対応します。最大/最小ピッチ比が 1.35 の場合、現在の 80 NA DUV システムは、ダブル パターニングなしで最小ピッチ 120 nm、最大ピッチ 90 nm までサポートできます。ただし、ダブルパターニングを使用した場合、最大ラインピッチは約 3 nm を超えてはなりません。最大/最小ピッチ比もそれに応じて調整する必要がある場合があります。金属線の曲がりくねった性質により、たとえば、あるセクションの 2 本の金属線 (4 ピッチ) が別のセクションの 3 本の金属線 (5 ピッチ) と同じ範囲に及ぶことは不合理ではありません。この偶数と奇数の不一致は、図 5,6 に示すように、奇数の金属フィーチャを分割してステッチすることで解決できます [XNUMX]。

図 5. 偶数と奇数のラインを含むレイアウトの分割は、奇数フィーチャを分割してダブル パターニングでステッチバックすることで解決できます。

最小ラインピッチが約 40 nm より小さくなると (13 nm DRAM ノード [7] を超える)、DUV のダブル パターニングが 6 重のパターニングになることが予想されます (図 XNUMX)。しかし、EUV 単一露光パターニングを検討してみてはいかがでしょうか?

図 6. 四重パターニング (NA 1.35 DUV システムを使用)。各色は個別の露出を表します。

SA および SWD の金属パターニングに関する追加の考慮事項は、垂直なビット線とワード線の方向に対応するためにレイアウトに 7 次元が必要であることです。これには、X+Y ダイポールまたはクロスダイポール照明の使用が必要となり、使用されるマスクの種類が制限されます。基本的に、照明は 8,9 つの方向のピッチのみをサポートし、他の方向のピッチを低下させます。事前に設計された位相シフトのないマスク (別名バイナリ マスク) は、正規化イメージ ログ スロープ (NILS) の望ましくない低下の影響を受けます (図 10)。 EUV は現在、必要な位相シフト マスクの不足と闘っています [XNUMX]。したがって、XNUMX 回の露光 (それぞれすでに XNUMX 回の DUV 露光のコストを超えています [XNUMX])、X 方向に XNUMX 回、Y 方向に XNUMX 回の露光が必要になります。

図 7. クロスダイポール照明は、バイナリ マスクを使用した 2 ビーム イメージングの NILS を低減します。

DUV 減衰位相シフト マスク (attPSM) は、明るい領域と暗い領域の間で 180 度の位相シフトを持つように設計でき、この問題を軽減できます (図 8)。

図 8. クロスダイポール照明は、attPSM マスクを使用した 2 ビーム イメージングの NILS を依然として減少させますが、値は 2 を超えたままです。

上記のシナリオを以下の表にまとめます。

表 1. DRAM における SA および SWD の最小ピッチ金属パターニングのシナリオ。

参考文献

[1] M. Eurlings ら、Proc. SPIE 4404、266 (2001)。

[2]D.Namら、Proc. SPIE 2、4000 (283)。

[3] M.ファン・デ・ケルクホフら、Proc. SPIE 10143、101430D (2017)。

[4] A. Garetto et al.、J. Micro/Nanolith. MEMS MOEMS 13、043006 (2014)。

[5]Y.Kohiraら、Proc. SPIE 5、9053T (90530)。

[6] S-Min Kim 他、Proc. SPIE 6520、65200H (2007)。

[7] J.Leeら、Proc. SPIE 12495、124950S (2023)。

[8] F. Chen、「NILS 改善のための位相シフトマスク – EUV のハンディキャップ」 https://www.linkedin.com/pulse/phase-shifting-masks-nils-improvement-handicap-euv-frederick-chen

[9] A. Erdmann、H. Mesilhy、および P. Evanschitkzy、J. マイクロ/ナノパターニング、材料、および計測学 21、020901 (2022)。

[10] L. Liebmann、A. Chu、および P. Gutwin、Proc. SPIE 9427、942702 (2015)。

この記事は、LinkedIn Pulse に最初に掲載されました。 アプリケーション固有のリソグラフィー: DRAM のセンス アンプおよびサブワードライン ドライバーの金属パターニング

また読む:

スペーサー定義のビアとカットを使用した BEOL マスク削減

インテルの EUV レジスト電子散乱モデルからの確率的欠陥の予測

中国のチップ製造ツールの宝庫:国宝か、それとも高価なスペアパーツか?

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/lithography/339965-application-specific-lithography-sense-amplifier-and-sub-wordline-driver-metal-patterning-in-dram/