In the age of rapid technological innovation, hyperscale datacenters are evolving at a breakneck pace. With the continued advancements in CPUs, GPUs, accelerators, and switches, faster data transfers are now paramount. At the forefront of this advancement is PCI Express (PCIe®), which has become the de-facto standard of interconnect for high-speed data transfers between processing and computing nodes.

Doubling Data Rates: The Trend Continues

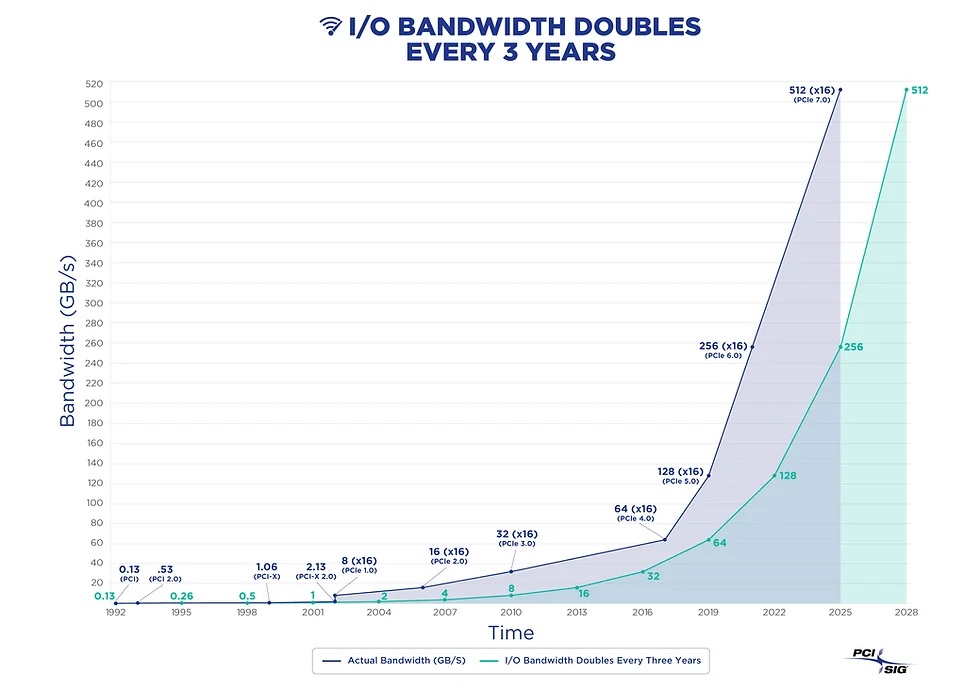

The PCI-SIG® consortium, responsible for the PCIe interface, has a history of launching a new PCIe generation approximately every three years. This invariably has doubled the data rate over the past decade. PCI-SIG’s latest release, PCIe 6.0.1, ushers in multi-level Pulse Amplitude Modulation (PAM4) signaling, boasting a staggering transfer rate of 64 GT/s in one direction on a single lane. Notably, during the 2022 PCI-SIG DevCon, the announcement of PCIe 7.0 specification came, doubling the data rate to 128 GT/s, emphasizing both power efficiency and higher bandwidth.

Figure 1. PCI-SIG I/O Bandwidth doubles every 3 years. From PCI-SIG

Stringent Testing for Compliance and Interoperability

It’s important to understand that beyond hyperscale data centers, the deployment of PCIe technology in fields like handheld devices, servers, automotive, industrial applications, and more demands high reliability and cost-effectiveness. This necessitates rigorous compliance testing for products to ensure they align with the PCIe 6.0.1 specification and can successfully interoperate with other PCIe devices.

Unveiling PAM4 Signaling and its Implications

The integration of PAM4 signaling in PCIe 6.0.1 is key. Unlike the Non-Return-to-Zero (NRZ) signaling, which used two distinct signal levels, PAM4 uses four, transmitting two bits of information within a single unit interval (UI). This modification introduces new challenges like cross-talk interferences, signal reflections, and power supply noise. The PCIe 6.0.1 specification has introduced the Signal-to-Noise Distortion Ratio (SNDR) to address these challenges, encapsulating both the traditional noise and non-compensable impairments within the electrical signal. Understanding of signal integrity issues in the high-speed communication channels due to cross-talk, reflection losses with frequency and time domain analysis is the key. Channel measurement techniques and various signal enhancement techniques with PCIe 6.0 Transmitter and Receiver equalization are used to compensate for non-ideal channel characteristics.

Summary

The advancements in PCIe technology have paved the way for a new age of data transfer capabilities, with PCIe 6.0.1 and the forthcoming PCIe 7.0 setting new benchmarks. However, with greater capabilities come greater challenges, particularly in ensuring compliance and interoperability. Partnerships like Synopsys and Tektronix are leading the charge in addressing these challenges, ensuring that the technology not only meets but exceeds the demands of today’s digital age.

Join Our Webinar!

Want to delve deeper into PCIe simulations and electrical testing? Join our upcoming webinar on Tuesday October 10, from 9:00 am to 10:00 am PDT, where Synopsys and Tektronix industry experts will discuss the latest in PCIe technology and the significance of robust testing methodologies. Click here to register now!

Speakers:

David Bouse is a Principal Technology Leader at Tektronix and an active contributor to PCI-SIG with expertise in highspeed SERDES including transmitter and receiver test methodologies, DSP algorithms for NRZ/PAM4 signaling, clock characterization, and automation software architecture.

Madhumita Sanyal is a Sr. Staff Technical Manager for Synopsys high-speed SerDes portfolio. She has +17 years of experience in design and application of ASIC WLAN products, logic libraries, embedded memories, and mixed-signal IP.

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day. As an S&P 500 company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and offers the industry’s broadest portfolio of application security testing tools and services. Whether you’re a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing more secure, high-quality code, Synopsys has the solutions needed to deliver innovative products. Learn more at www.synopsys.com.

Also Read:

Next-Gen AI Engine for Intelligent Vision Applications

VC Formal Enabled QED Proofs on a RISC-V Core

Share this post via:

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Automotive / EVs, Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- ChartPrime. Elevate your Trading Game with ChartPrime. Access Here.

- BlockOffsets. Modernizing Environmental Offset Ownership. Access Here.

- Source: https://semiwiki.com/events/333825-why-rigorous-testing-is-so-important-for-pci-express-6-0/