몇년째 만나고 있어요. 아미크 에다 공동 창립자 Cristian Amitroaie는 몇 달에 한 번씩 업계 현황, 설계 및 검증의 주요 동향, 칩 개발을 촉진하고 가속화하는 데 도움이 되는 방법에 대해 논의합니다. 최근에 언급된 흥미로운 새 기능을 발견했습니다. 릴리스를 누르십시오, 그래서 저는 Cristian에게 더 많은 정보를 요청했습니다. 이로 인해 활기차고 흥미로운 토론이 이어졌습니다.

요즘 대부분의 설계자와 검증 엔지니어는 SystemVerilog에서 코드를 작성하지만 예외도 있습니다. 일부는 HLS(고수준 합성) 도구를 활용하여 SystemC 또는 SystemVerilog보다 좀 더 추상적인 다른 언어로 설계합니다. 다른 사람들은 자신의 언어로 작성하고 사용자 정의 도구를 사용하여 개발 프로세스의 시뮬레이션, 공식 검증, 합성 및 기타 단계에 사용되는 SystemVerilog 파일을 생성합니다.

Cristian은 엔지니어들이 주로 SystemVerilog이지만 Perl 및 Python의 Jinja2 라이브러리와 같은 확립된 언어나 독점 언어로 "전처리기" 문을 포함하는 코드를 작성하는 중간 지점을 가끔 본다고 말했습니다. 그들은 스크립트를 사용하여 이러한 파일을 처리하고 나머지 흐름에 대한 순수 SystemVerilog 파일을 생성합니다. 저는 Cristian에게 전처리기 사용이 엔지니어가 IDE(통합 개발 환경)를 사용하는 방식을 어떻게 변화시키는지 물었습니다.

저는 AMIQ EDA 설계 및 검증 도구(DVT) IDE 제품군은 전처리기 코드로 파일을 편집할 때에도 즐겨 사용하는 모든 기능에 액세스하기를 원합니다. AMIQ EDA 팀은 순수 SystemVerilog에서와 마찬가지로 이러한 파일을 편집할 때 전체 IDE 기능을 활성화하는 영리한 경험적 방법을 개발했습니다. 이러한 기능에는 탐색 하이퍼링크, 자동 완성, 즉각적인 오류 감지, 빠른 수정, 리팩토링 및 DVT IDE 사용자가 즐겨 사용하는 모든 고급 기능이 포함됩니다.

이것은 나에게 흥미로웠다. 우리는 혼합 언어 파일을 "이해"하는 것에 대해 이야기하고 있지만 실제로는 컴파일러가 쉽게 소화할 수 있는 것이 아닙니다. 내가 제대로 작동하는지, 그리고 이것이 실제로 가능한지 확인하기 위해 Cristian은 이 기능의 개발을 조정한 팀 리더인 Zeljko Zurzic을 초대하여 작동 방식을 설명했습니다. 그는 모든 사용자가 해야 할 일은 전처리기 명령문이 포함된 파일("p 파일")과 생성된 파일("g 파일") 간의 매핑에 대해 DVT IDE에 알리는 것이라고 말했습니다.

이는 다양한 사용 사례를 지원하는 전용 컴파일러 지시문을 사용하여 수행됩니다. 예를 들어 DVT IDE 컴파일러에 "g 파일 헤더 주석에서 해당 p 파일을 찾아보세요"라고 지시하는 방법이 있습니다. 이 작업이 완료되면 사용자는 마치 특별한 내용이 없는 것처럼 p 파일을 편집하면 됩니다. 즉각적인 증분 컴파일은 SystemVerilog 오류가 입력될 때 플래그를 지정하고, 하이퍼링크를 통해 코드 주위로 오류를 표시하고, 자동 완성 및 리팩토링이 제대로 작동하고, 다양한 다이어그램을 요청할 수 있습니다.

전처리기 코드가 포함된 섹션은 사용자가 SystemVerilog 코드로 변환될 것임을 알 수 있도록 눈에 띄게 표시됩니다. ~ 안에 DVT 이클립스 IDE Inspect View를 사용하여 코드가 어떻게 생성되는지 확인할 수 있습니다. ~에 VS 코드용 DVT IDE 그들은 변화를 “엿볼” 수 있습니다. 전처리기 코드가 변경될 때마다 전처리 스크립트를 자동으로 실행하도록 DVT IDE를 구성할 수 있습니다. 원하는 경우 사용자는 ap 파일을 해당 g 파일과 쉽게 비교할 수 있습니다.

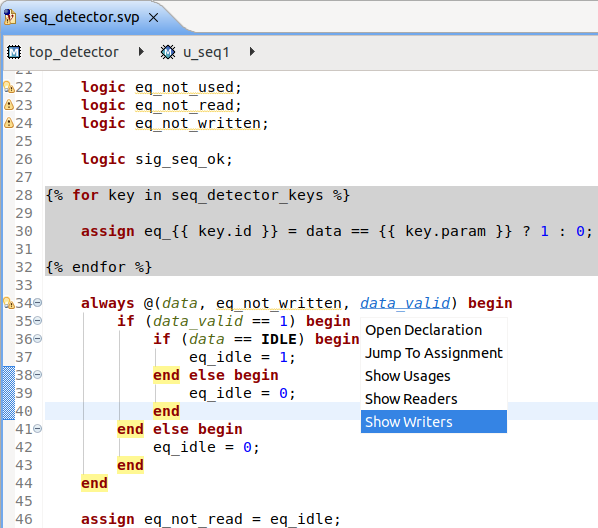

Zeljko는 이 새로운 기능이 실제로 작동하는 모습을 보여주는 세 가지 스크린샷을 제공했습니다. 아래 첫 번째 항목은 Jinja2 전처리기 문을 포함하는 DVT Eclipse IDE의 파일을 보여줍니다. SystemVerilog 코드가 아닌 코드가 있음에도 불구하고 사용자는 강력한 "Show Writers" 기능을 활용하여 변수가 어떻게 구동되는지 빠르게 이해할 수 있습니다. 컴파일 오류와 경고는 디스플레이의 가장 왼쪽 열에 표시됩니다.

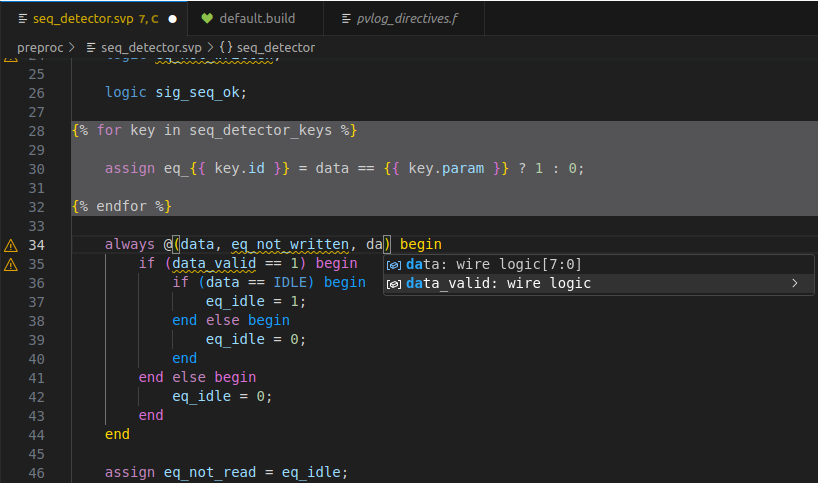

아래 스크린샷은 VS Code용 DVT IDE에 동일한 파일을 표시하며 왼쪽 열에 컴파일러 문제를 표시하고 자동 완성 사용을 활성화합니다. 이는 전처리기 문이 있는 코드에서 가장 고급 DVT 함수를 어떻게 사용할 수 있는지 보여줍니다.

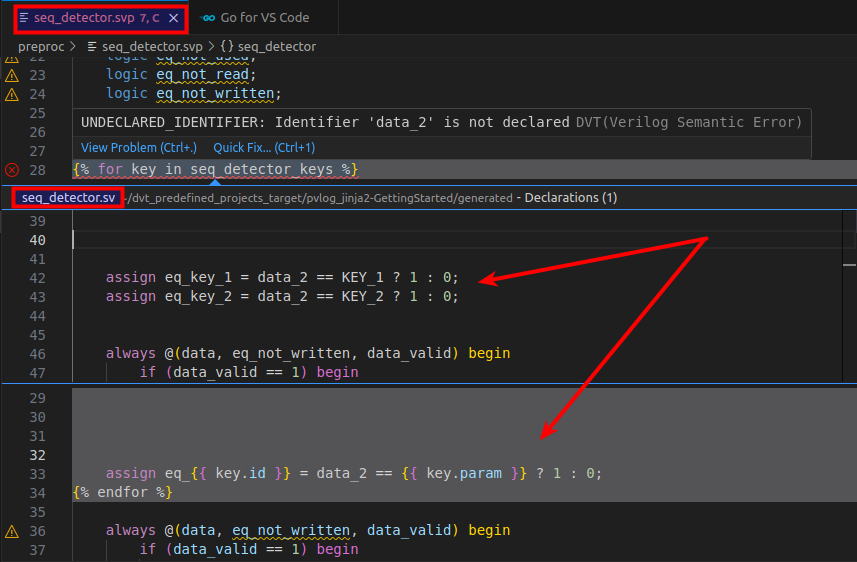

Zeljko는 IDE가 생성된 SystemVerilog 코드를 확인한다는 점을 강조했습니다. 이는 전처리기 명령문에 오류가 있거나 전처리 스크립트에 버그가 있을 수 있기 때문에 중요합니다. 아래 스크린샷은 그러한 예를 보여줍니다. 생성된 SystemVerilog 코드에는 소스 파일에 정의되지 않은 변수가 포함되어 있습니다. DVT IDE는 컴파일 오류, p 파일, g 파일에 생성된 코드를 표시합니다.

g 파일을 보는 것은 디버그에 도움이 될 수 있지만 중요한 점은 사용자가 p 파일로 직접 작업하고 강력한 IDE를 사용하여 파일을 분석하고 편집한다는 것입니다. g 파일은 "읽기 전용"으로 태그가 지정되며 수정되면 사용자에게 경고가 표시됩니다. 나는 이 말을 듣고 기뻤습니다. 코드 생성 과정에서 덮어쓰게 될 파일을 수동으로 변경하는 것은 정말 나쁜 생각이라는 것을 우리 모두 알고 있습니다.

마지막으로 Cristian은 이 새로운 기능의 핵심은 사용자가 마치 순수한 SystemVerilog인 것처럼 전처리기 문을 사용하여 코드를 편집할 수 있다는 것이라고 강조했습니다. 이를 가능하게 하는 것은 전처리기 기반 흐름에 의존하는 몇몇 주요 고객의 노력으로 이루어졌습니다. 설명과 시간을 내어 주신 Zeljko와 Cristian에게 감사드립니다.

전처리기 파일 사용이나 AMIQ EDA 솔루션의 모든 측면에 대해 자세히 알아보려면 설계 및 검증 컨퍼런스 및 전시회(DVCon) 미국 캘리포니아주 산호세에서 5월 6일과 XNUMX일.

또한 읽기 :

AMIQ EDA 창립자 겸 CEO Cristian Amitroaie와 함께하는 2024년 전망

Linting을 사용하여 오류 없는 테스트벤치 코드 작성

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/