2024年のSEMI国際戦略シンポジウムに向けて、私は組織委員会のメンバーから、テクノロジー、経済学、持続可能性の観点からXNUMX年後のロジックがどうなるかを検討するよう求められました。以下は私のプレゼンテーションについての議論です。

ロジックを理解するには、最先端のロジックデバイスがどのように構成されているかを理解することが役立つと思います。 TechInsights は詳細なフットプリント分析レポートを作成しており、私は Intel および AMD マイクロプロセッサ、Apple A シリーズおよび M シリーズ プロセッサ、NVIDIA GPU、およびその他のデバイスを含む 7 個の 5nm および 1nm クラスのデバイスに関するレポートを作成しました。図 XNUMX は、ダイ領域を構成するものを示しています。

図 1 からわかるように、ロジックはダイ領域の XNUMX 分の XNUMX 弱、メモリはダイの XNUMX 分の XNUMX 弱、残りは I/O、アナログ、その他です。興味深いのは、実際に測定された SRAM メモリ領域が、System On a Chip (SOC) 製品についてよく言われるパーセンテージよりもはるかに小さいことです。右下のプロットは、外れ値が XNUMX つあることを示していますが、それ以外の値は密にクラスター化されています。

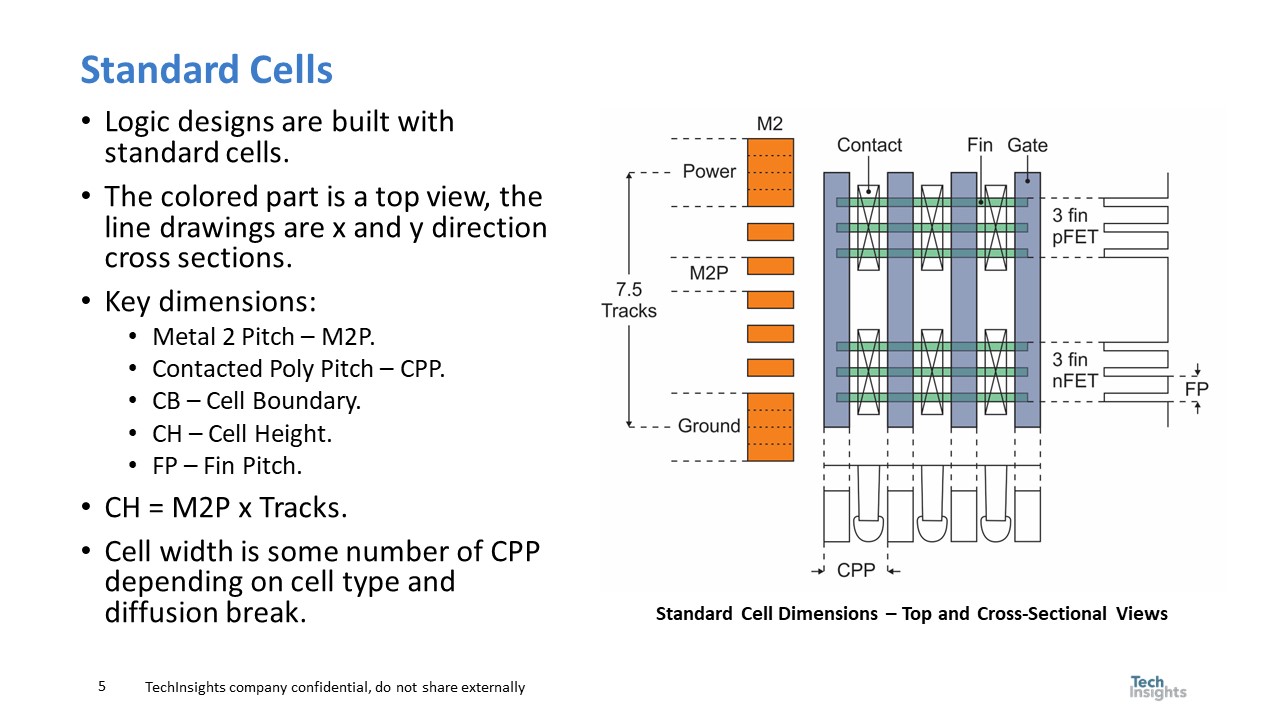

単一のロジックはダイ領域のほぼ半分を占めており、デザインのロジック部分から始めるのが理にかなっています。ロジック設計はスタンダード セルを使用して行われます。図 2 はスタンダード セルの平面図です。

標準セルの高さは通常、メタル 2 ピッチ (M2P) にトラック数を掛けたものとして特徴付けられますが、図の右側を見ると、セルの高さと一致する必要があるデバイス構造の断面図が示されています。そしてデバイスの物理的な制約を受けます。同じことは、接触ポリピッチ (CPP) に依存するセル幅の場合にも当てはまります。図の下部には、再び物理学によって制約されるデバイス構造の断面図が示されています。

図 3 は、セル幅とセル高さのスケーリングの実際的な限界を決定するための分析の結果を示しています。スケーリング制約について詳しく説明したプレゼンテーションがあり、そのプレゼンテーションには図 2 と図 3 の間に数十枚のスライドがありますが、時間が限られていたため、結論しか示すことができませんでした。

セル幅のスケーリングは CPP に依存します。図の左側は、CPP がゲート長 (Lg)、コンタクト幅 (Wc)、および 30 つのコンタクトからゲート スペーサーまでの厚さ (Tsp) でどのように構成されるかを示しています。 Lg は漏れによって制約され、許容可能な漏れの最小 Lg はデバイスのタイプによって異なります。無制限の厚さでチャネルの表面を制御する単一のゲートを備えたプレーナ デバイスは、約 5 nm に制限されます。 FinFET と水平ナノシート (HNS) はチャネルの厚さ (約 3nm) を制限し、それぞれ 4 つと 2 つのゲートを持ちます。最後に、1D 材料では、チャネル厚が 5nm 未満の非シリコン材料が導入され、最大 2nm までの Lg を生成できます。 Wc と Tsp は両方とも、寄生成分により拡張能力が限られています。結論として、今日の CPP が ~30nm であるのに対し、50D デバイスは ~XNUMXnm の CPP を生成できる可能性が高いということです。

セルの高さのスケーリングを図の右側に示します。 HNS は、複数のフィンの代わりに単一のナノシート スタックを提供します。その後、CFET を備えたスタック型デバイスへの進化により、水平方向の np 間隔が排除され、nFet と pFET がスタックされます。現在 150nm ~ 200nm であるセルの高さは、約 50nm まで減らすことができます。

CPP とセル高さのスケーリングを組み合わせると、平方ミリメートルあたり約 1,500 億個のトランジスタ (MTx/mm) のトランジスタ密度を実現できます。2) 対今日 <300MTx/mm2。 2D 材料は 2030 年中期から後期の技術となる可能性が高いため、1,500 MTx/mm であることに注意してください。2 ここで説明するタイミングの外にあります。

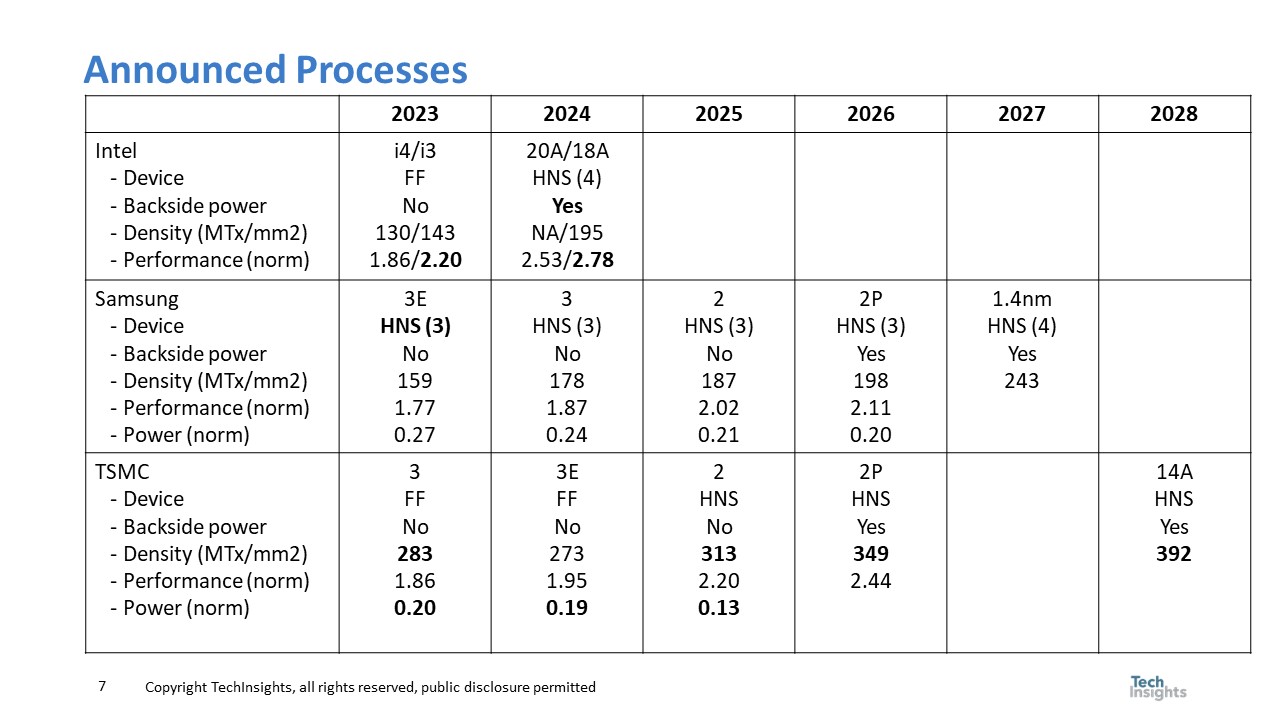

図 4 は、Intel、Samsung、TSMC が発表したプロセスの概要を示しています。

企業および年ごとに、デバイスの種類、裏面電源の使用の有無、密度、電力、およびパフォーマンスが表示されます (利用可能な場合)。電力とパフォーマンスは相対的な指標であり、Intel では電力を利用できません。

図 4 では、主要なパフォーマンスと技術革新が太字で強調表示されています。 Samsung は 2023 年に HNS を初めて量産しますが、Intel は 2024 年まで、TSMC は 2025 年まで HNS を導入しません。Intel が 2024 年に初めてバックサイド電源を量産に導入し、Samsung と TSMC は 2026 年まで HNS を導入しません。

私の分析では、Intel が i3 でパフォーマンスのリーダーであり、図示されている期間そのステータスを維持しており、TSMC が電力のリーダー (Intel データは利用できません) と密度のリーダーであると結論付けています。

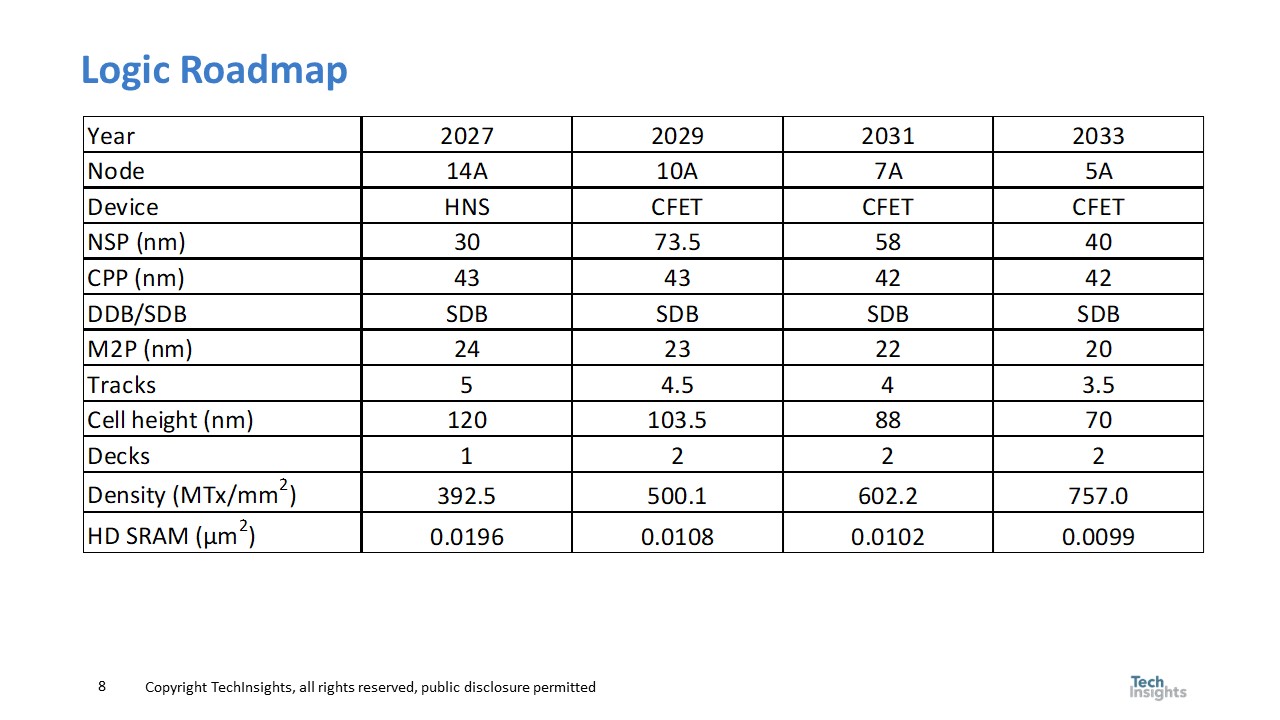

図 5 は、ロジック ロードマップを示しており、予測される SRAM セル サイズも含まれています (これについては後で詳しく説明します)。

図 5 から、CFET は 2029 年頃に導入され、ロジック密度が向上し、SRAM セル サイズがほぼ半分に削減されると予想されます (SRAM セル サイズのスケーリングは実質的に最先端で停止しています)。ロジック密度は最大 757MTx/mm に達すると予想されます2 2034によります。

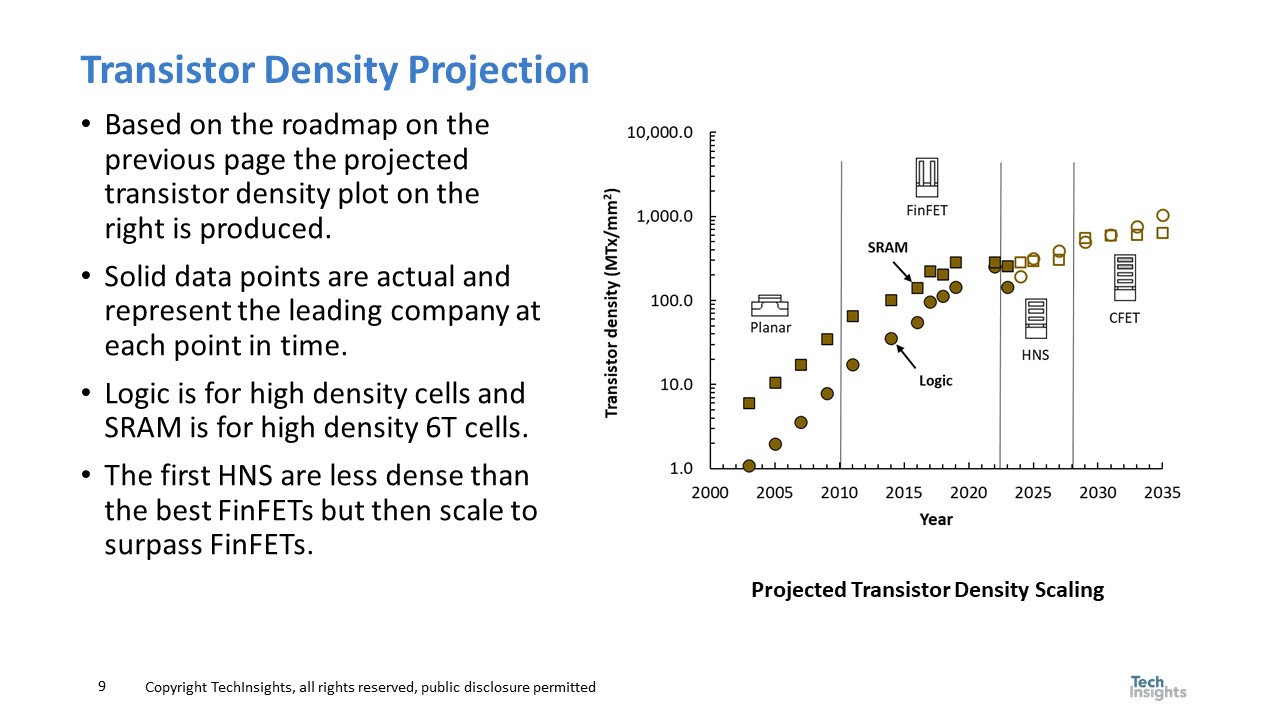

ロジック トランジスタ密度の予測と SRAM トランジスタ密度の予測の両方を図 6 に示します。

ロジックと SRAM の両方のトランジスタ密度のスケーリングは鈍化していますが、SRAM は大幅に増加しており、ロジックは現在 SRAM と同様のトランジスタ密度を持っています。

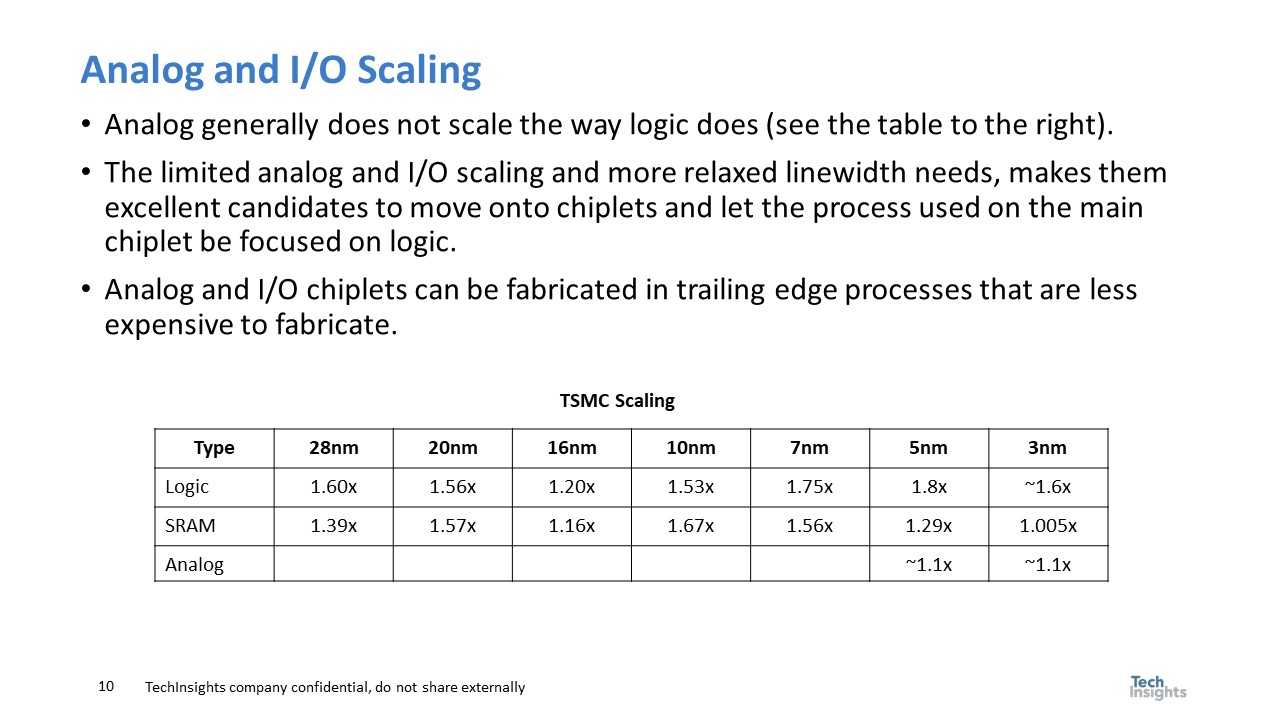

スライド 7 は、ロジックおよび SRAM と比較したアナログ スケーリングに関する TSMC データをまとめています。アナログおよび I/O スケーリングもロジック スケーリングよりも遅くなります。

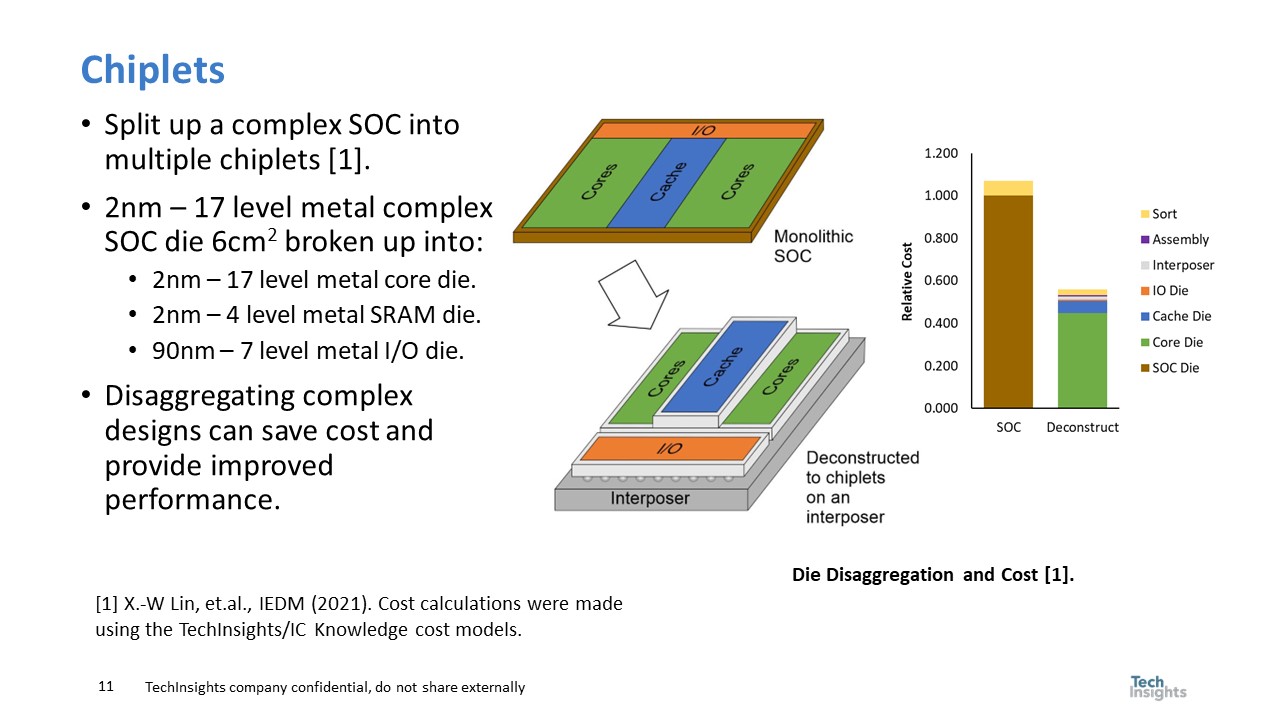

遅い SRAM、アナログおよび I/O スケーリングに対する考えられる解決策は、チップレットです。チップレットを使用すると、より低コストで、より最適化されたプロセスを利用して SRAM と I/O を作成できます。

図 8 の右側の図は、私がシノプシスと共著した 2021 年の論文からのものです。私たちの結論は、大きな SOC をチップレットに分割すると、パッケージング/組み立てコストの増加を考慮してもコストを半分に削減できるということでした。

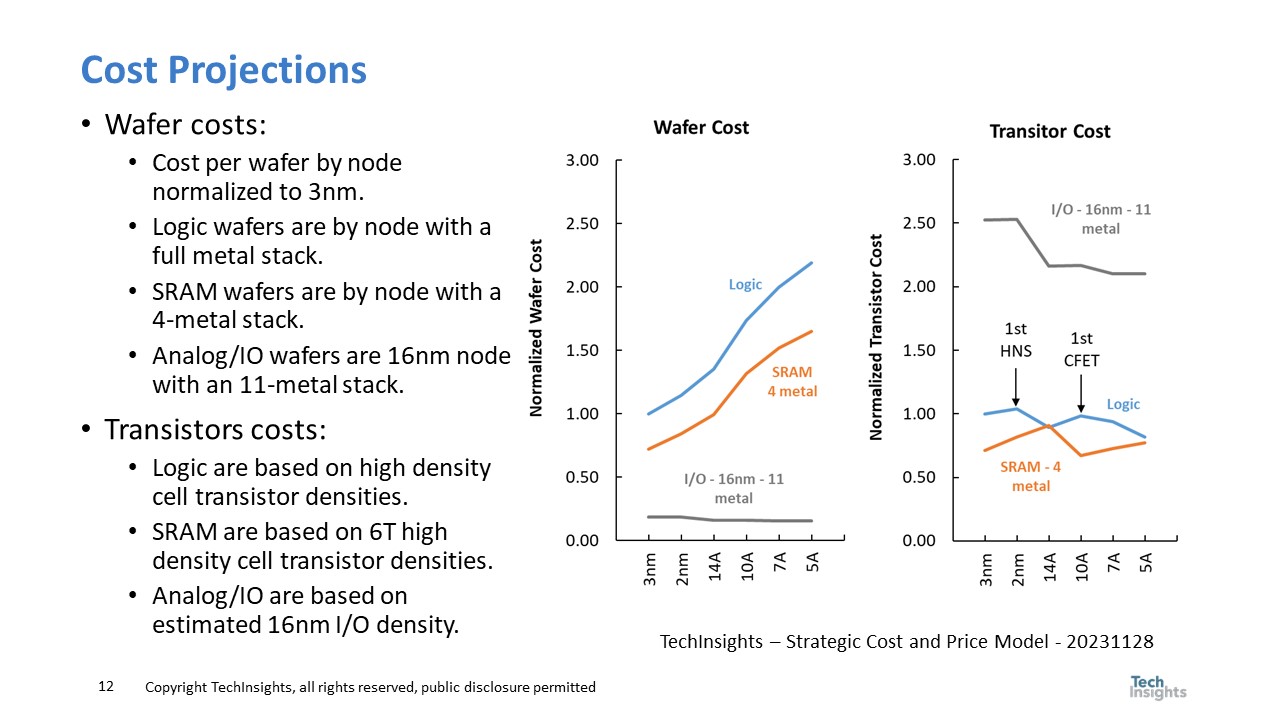

図 9 は、ロジック、SRAM、および I/O の正規化されたウェーハおよびトランジスタのコストを示しています (この図は元のプレゼンテーションから更新されていることに注意してください)。

右の図には、正規化されたウェーハコストが示されています。ロジック ウェーハのコストは、メタル層の数が増加しているフルメタル スタックのものです。 SRAM ウェーハは同じノードですが、SRAM のレイアウトがより規則的であるため、金属層は 4 つに制限されています。 I/O ウェーハのコストは、16nm – 11 メタル プロセスに基づいています。適切な I/O パフォーマンスを確保するために、最小コストの FinFET ノードを得るために 16nm を選択しました。

右図はウエハコストをトランジスタコストに換算したものです。興味深いことに、I/O トランジスタは非常に大きいため、低コストの 16nm ウェハでもコストが最も高くなります (I/O トランジスタのサイズは、TechInsights による実際の I/O トランジスタの測定に基づいています)。ロジックトランジスタのコストは、縮小が緩やかな最初のTSMC HNSシートノードの2nmで上昇します。第 14 世代 HNS ノードとして XNUMXA でのシュリンクはさらに大きくなると予想されます (これは TSMC が最初の FinFET ノードで行ったことと同様です)。もう一度言いますが、最初の CFET ノードのコストにより、XNUMX つのノードのトランジスタのコストも増加します。 SRAM トランジスタのコストは、XNUMX 回限りの CFET 縮小を除いて縮小が限定されているため、上昇傾向にあります。この分析の結論は、チップレットは一度限りのメリットを提供できるものの、トランジスタのコスト削減はわずかであるということです。

持続可能性に移り、図 10 は二酸化炭素排出量を構成するさまざまな「範囲」を説明します。

スコープ 1 は、プロセス化学物質および燃焼によるサイトでの直接排出量であり (電気もサイトで生成される場合はスコープ 1 になります)、スコープ 2 は購入した電力の二酸化炭素排出量によるものです。スコープ 3 はこの分析には含まれていませんが、購入した材料、製造された製品の使用、および企業の従業員が運転する車両などの二酸化炭素排出量によるものです。

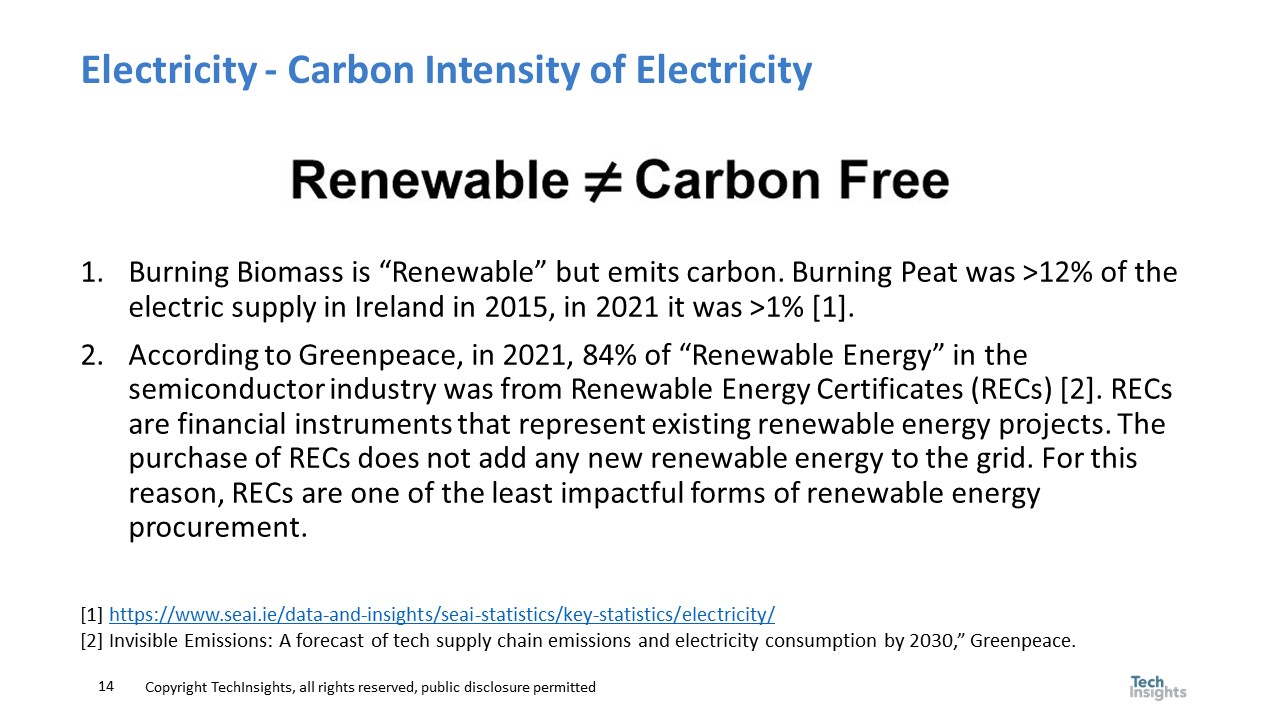

半導体業界の多くの企業は、電力はすべて再生可能であるため、電力による二酸化炭素排出はないと主張しています。図 11 は、再生可能エネルギーとカーボンフリーエネルギーを比較しています。

重要な問題は、84年の半導体業界の再生可能エネルギーの2021%が、他の誰かがすでに行った削減を請求する権利を企業が購入する再生可能エネルギー証書であることがグリーンピースによって判明したことだ。これは、低炭素電源を設置したり、低炭素電力を提供するために他者にお金を払ったりすることと同じではなく、実際に世界の二酸化炭素排出量を削減するものではありません。

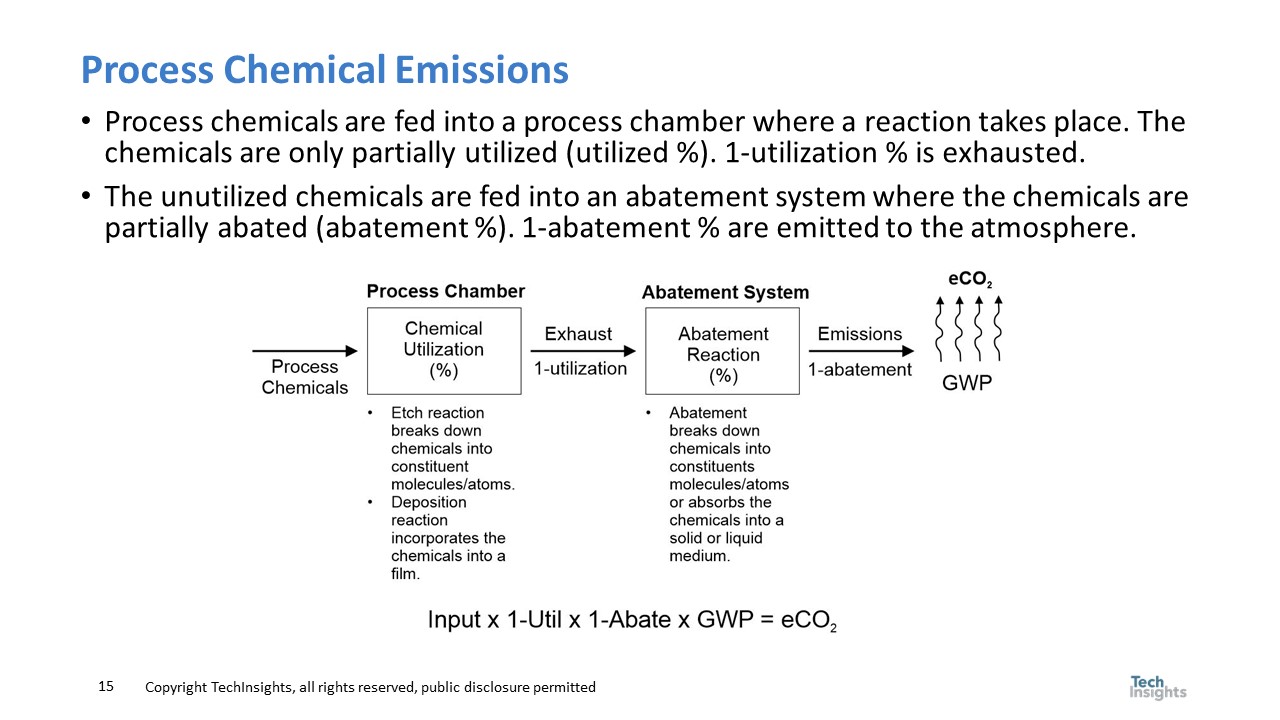

図 12 は、プロセス化学物質の放出がどのように発生し、特徴付けられるかを示しています。

プロセス化学物質はプロセス チャンバーに入り、そこで化学物質の一部がエッチングまたは堆積反応に利用され、化学物質が分解されたり、堆積膜に化学物質が組み込まれたりします。 1-utilization は、ツールの排気口から漏れ出る化学薬品の量です。その後、ツールの排気は除害チャンバーに入り、化学物質の一部がさらに分解され、除害による大気中への排出量は 1 除になります。最後に、地球温暖化係数 (GWP) を適用して、排出量の炭素当量を計算します。 GWP では、化学物質が大気中にどれだけの時間残留するか、また二酸化炭素と比較して化学物質が反射する熱の量が考慮されます。二酸化炭素のGWPは1、SFなどの半導体プロセスケミカル6 およびNF3 GWP 値はそれぞれ 24,300 と 17,400 です (IPCC AR6 による)。

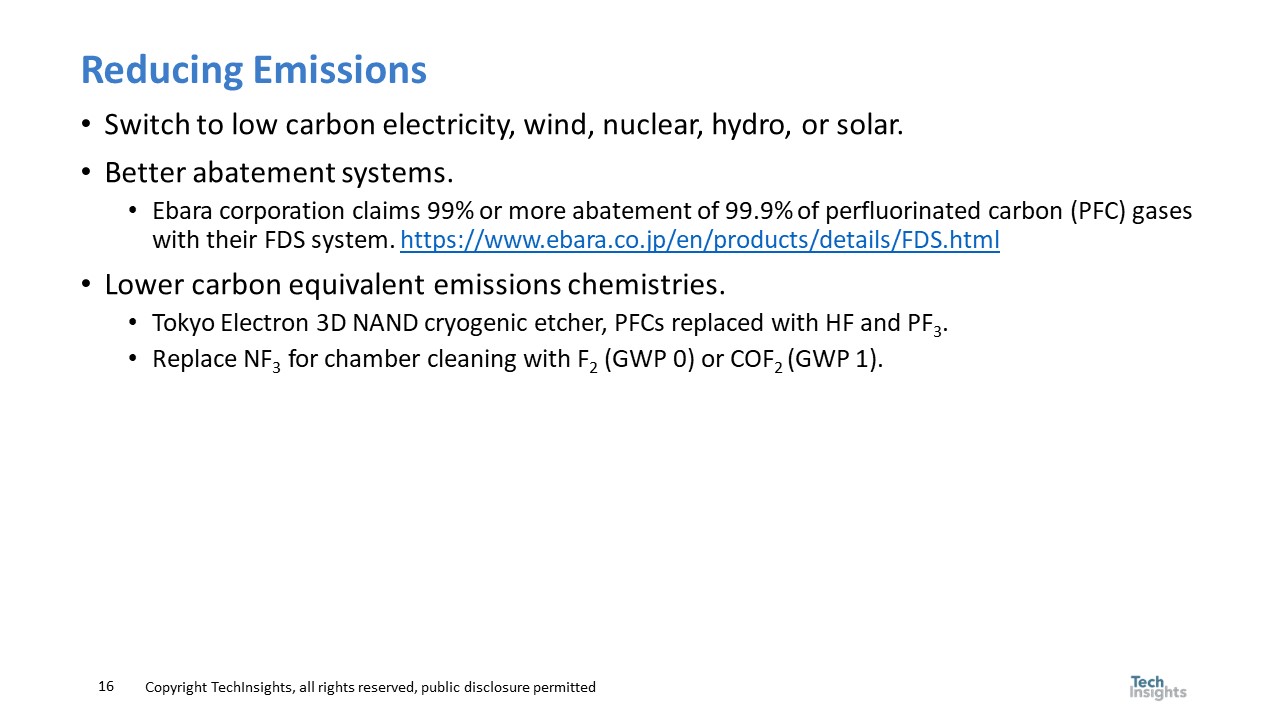

図 13 は、排出量を削減するためのいくつかのオプションを示しています。

石炭などの電源は 820 グラムの CO を排出します2 キロワット時あたりの等価排出量 (gCO2e/KWh) に対し、太陽光、水力発電、風力、原子力はそれぞれ 48、24、12、12 gCO2e/KWh を生成します。

より効率的な除害システムは、プロセスガスをより効果的に分解できます。 Fab 削減システムの効率は、報告されている米国の一部のサイトで 0% (削減なし) から最大 90% までの範囲です。私たちは、世界の 300mm ファブの平均は約 70% であり、200mm 以下のウェハ サイズのファブのほとんどは削減の余地がないと推定しています。最大 99% の効率を実現するシステムが利用可能です。

より低放出の化学物質も使用することができる。東京エレクトロンは、GWPゼロのガスを使用する3D NAND用の新しいエッチングツールを発表した。 SFなどのガス6 およびNF3 主に洗浄のためにチャンバー内にフッ素 (F) を供給し、F を置換するために使用されます。2 (GWP 0) または COF2 (GWP 1) はこの排出源を本質的に排除できます。

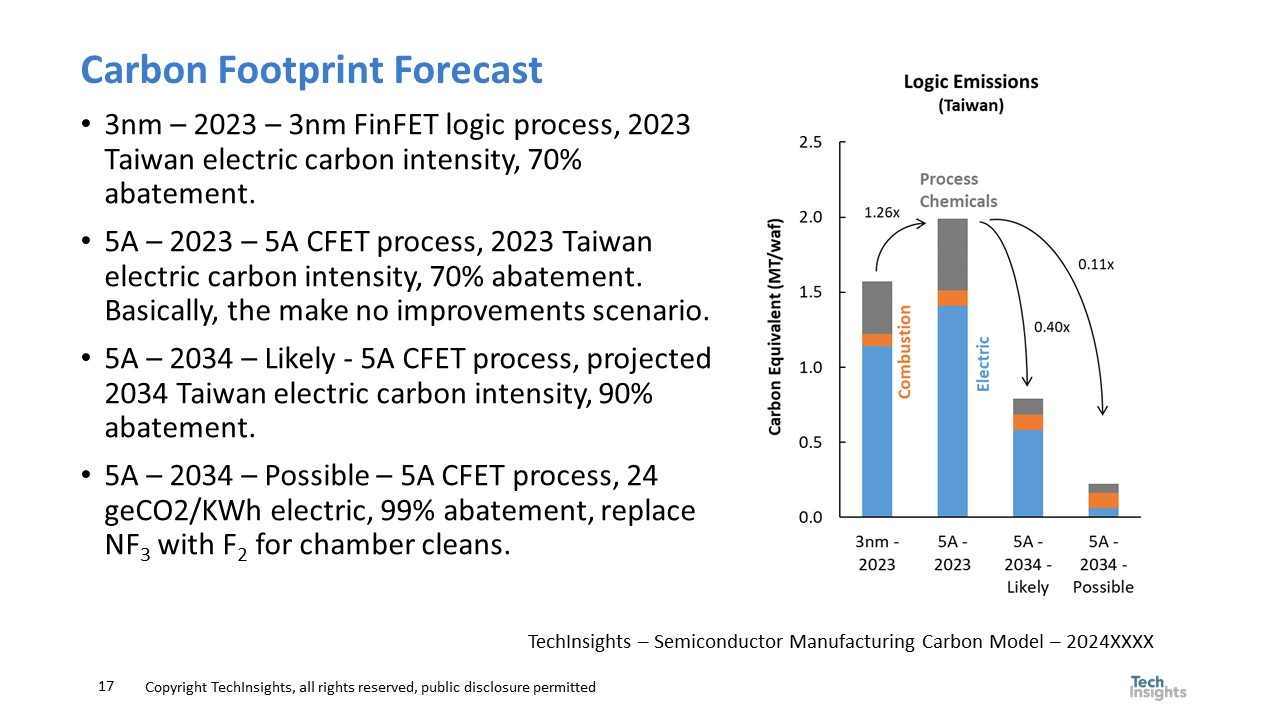

図 14 は、ロジックの二酸化炭素排出量予測を示しています。

図の左側の最初のバーは、台湾の電力二酸化炭素排出量と 3% 削減を想定して、2023 年に台湾で実行された 70nm プロセスです。 5 番目のバーは、2023A プロセスと、同じ 70 年の台湾の電力炭素強度と 1.26% 削減が使用された場合に生じる排出量です。プロセスの複雑さが増すと、全体の設置面積が 2034 倍に増加します。 90 年に向けて、台湾の電力は大幅に脱炭素化すると予想されており、5% 削減も一般的になるはずです。2034 番目のバーは、この条件下での 99A プロセスがどのようになるかを示しています。これは排出量を半分以上削減することを意味しますが、XNUMX 年に業界が稼働するウェーハ数の増加がこの改善を圧倒する可能性があります。右側の最後のバーは、十分な投資で可能なもので、低炭素電力、XNUMX% 削減、F の使用に基づいています。2 チャンバークリーニング用。

図 15 は、私たちの結論を示しています。

トランジスタ密度、ウェーハおよびダイのコスト見積もりは、コストと価格の見積もり、および詳細な機器と材料の要件を生成する業界ロードマップである TechInsights の戦略的コストおよび価格モデルを使用して生成されました。 GHG 排出量の推定値は、TechInsights Semiconductor Manufacturing Carbon Model を使用して生成されました。詳細については、sales@techinsights.com までお問い合わせください。

TechInsights のリバース エンジニアリング ビジネス ユニットの同僚に感謝したいと思います。彼らのデジタル フロアプランとプロセス レポートは、このプレゼンテーションの作成に非常に役立ちました。また、この作業のために I/O トランジスタのサイジング データを抽出してくれた TechInsights の Alexandra Noguera 氏。

また読む:

IEDM 2023 – 300mm ウェーハ製造時の炭素排出量のモデリング

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/