増加し続けるデータ速度の絶え間ない追求により、1.6 テラビット/秒 (Tbps) 時代が目前に迫っており、データセンター内で前例のないレベルの接続と帯域幅が約束されています。データ集約型アプリケーションが急増し、リアルタイム処理の需要が高まるにつれ、堅牢で効率的な通信インフラストラクチャの必要性が最も重要になっています。このインフラストラクチャの中心には電気光相互接続があり、高速、低遅延、電力効率の高い機能を組み合わせてデータ伝送に革命を起こそうとしています。 224G シリアル リンクの採用は、エンドツーエンドの 1.6Tbps トラフィック容量を実現するための重要な要素として浮上しています。これらの高速シリアル リンクはデータ伝送のバックボーンとして機能し、ネットワーク内のさまざまなコンポーネント間のシームレスな通信を促進します。超高速のデータ レートと帯域幅の要求を処理できるため、次世代通信システムの実現には不可欠です。あらゆる主要なテクノロジーの進歩と同様、克服すべき固有の課題が存在します。光チャネルと光エンジンは両方とも非線形動作を導入します。従来のシミュレーション支援設計手法では、線形チャネルを想定して電気回路言語とシミュレータを使用して光学エンジンをモデル化することが多く、相互接続性能の評価が過度に楽観的になってしまいます。

最近開催された DesignCon 2024 カンファレンスで、シノプシスは、ネイティブな電気および光信号表現を使用した電気・光協調シミュレーション研究の結果を発表しました。この調査のハイライトは、使用されたシステム設計手法が、テクノロジー、データ レート、変調形式に依存せず、線形障害と非線形障害の両方を考慮していることです。 「224Gbps シリアル リンクのシステム設計方法論、シミュレーションおよびシリコン検証」 論文提出 DesignCon 2024 Best Paper Awardを受賞しました。

以下は、DesignCon でシノプシスが提出した 112 つの論文、すなわち「ダイレクトドライブ光学エンジンを備えた高速 224G/224G SerDes のパフォーマンス評価」と「XNUMXGbps シリアル リンクのシステム設計方法論、シミュレーションおよびシリコン検証」からの一部の抜粋です。 」

1.6T時代の前方誤り訂正

前方誤り訂正 (FEC) メカニズムは、特に 1.6Tbps トラフィックのコンテキストにおいて、高速リンク上のデータ伝送の信頼性を高める上で極めて重要な役割を果たします。 FEC はエラーに対処し、データの整合性を確保するのに役立ちますが、その実装には電力消費や遅延などの追加の考慮事項が必要になります。 1.6T 時代の効率的な通信システムを設計するには、ビット誤り率 (BER)、電力効率、遅延の間の適切なバランスをとることが不可欠になります。

電気光学インターフェースの出現

1.6Tbps 時代の進化する需要を満たすために、電気光インターフェースは変革的な役割を果たす準備ができています。これらのインターフェイスは、光テクノロジーの利点を活用して、高速、低遅延、電力効率の高い通信ソリューションを提供します。 Co-Packaged Optics (CPO) や Die-to-Die (D2D) 相互接続などのテクノロジーは、光コンポーネントを既存のデータセンター アーキテクチャにシームレスに統合するための有望な手段を提供し、効率とパフォーマンスの新時代の到来をもたらします。

エンドツーエンド リンクの障害を回避する

ただし、エンドツーエンドの 224G リンクの導入には課題がないわけではありません。電気回路言語とシミュレータを使用して光インターコネクトをシミュレーションする従来のアプローチは、場合によっては効果的ですが、いくつかのトレードオフを伴います。ノイズ、ジッター、歪み、クロストークなどの障害は、信号品質を大幅に低下させ、全体的なパフォーマンスに影響を与える可能性があります。これらの課題に対処するには、障害のモデリングと軽減に細心の注意を払い、光および電気光学インターフェースに固有の非線形効果に直面しても通信インフラストラクチャの堅牢性と信頼性を確保する必要があります。

正確なシステムモデリングの役割

正確なシステムモデリングは、電気光相互接続の複雑さを回避し、光伝送に固有の非線形効果に対抗するために最も重要です。さまざまなコンポーネントとその相互作用を綿密にシミュレーションすることで、設計者はシステムの動作に関する貴重な洞察を取得し、最適化の余地がある領域を特定できます。さらに、シリコン実装との相関により、シミュレーション結果が現実世界のパフォーマンスと厳密に一致することが保証され、情報に基づいた意思決定と効率的な設計の反復が可能になります。

システム シミュレーションとシリコンの相関比較

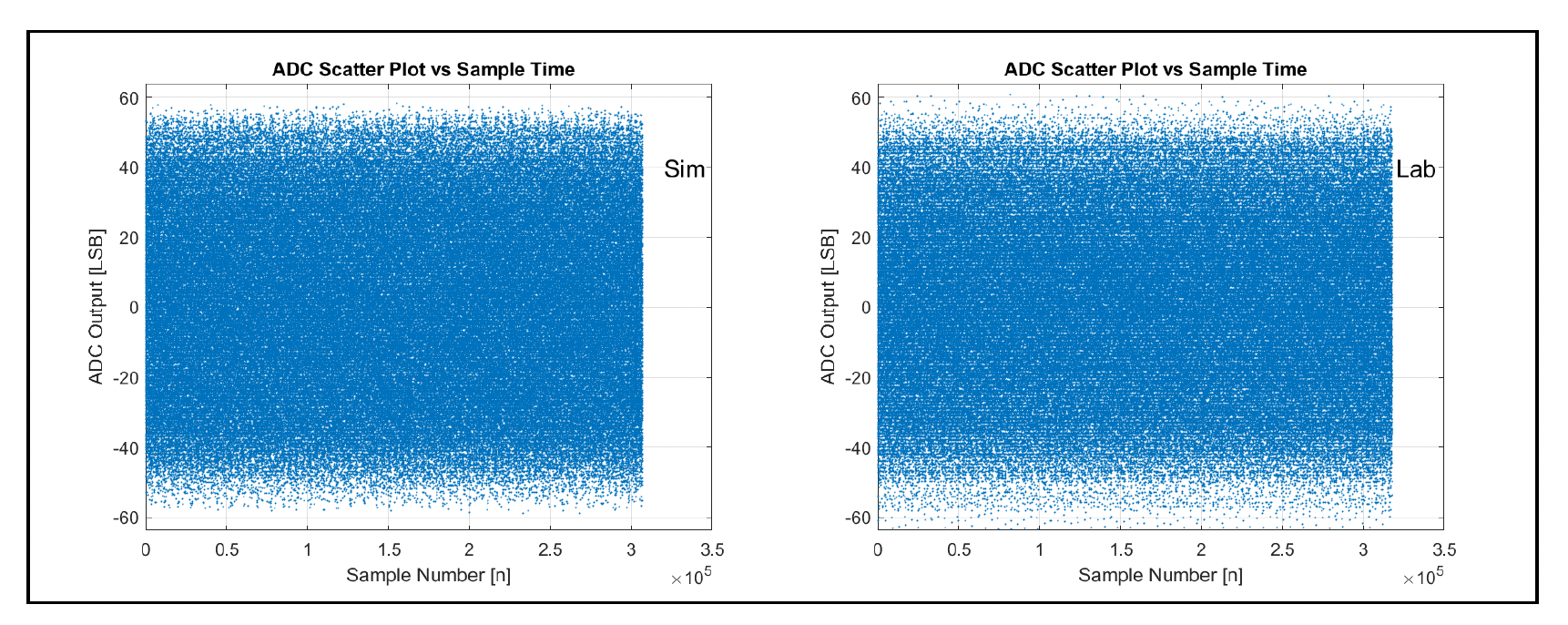

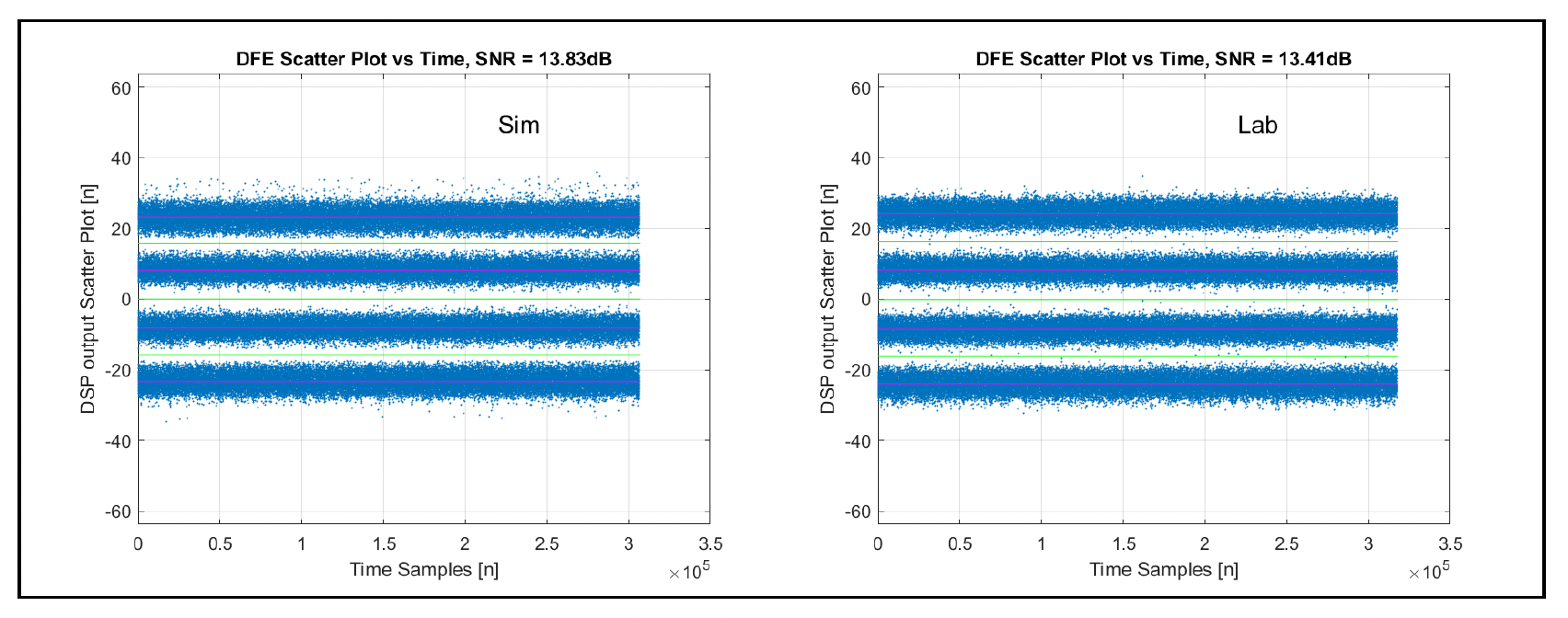

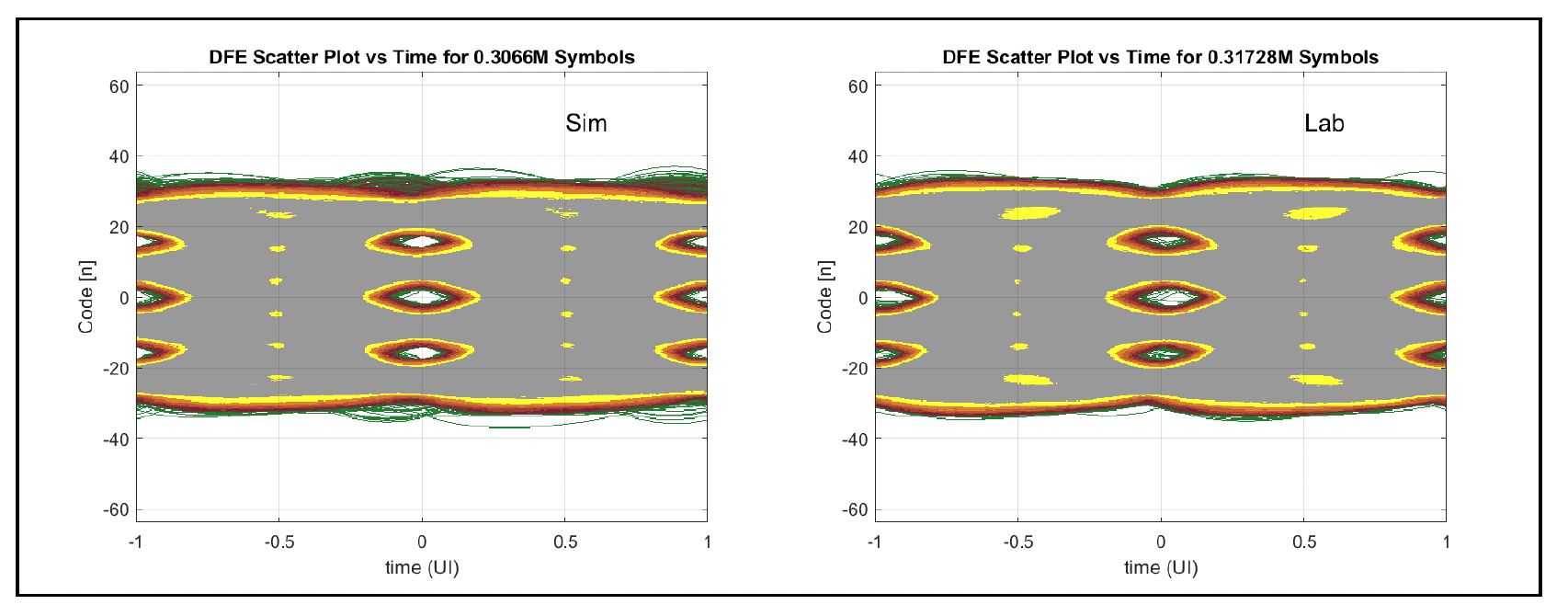

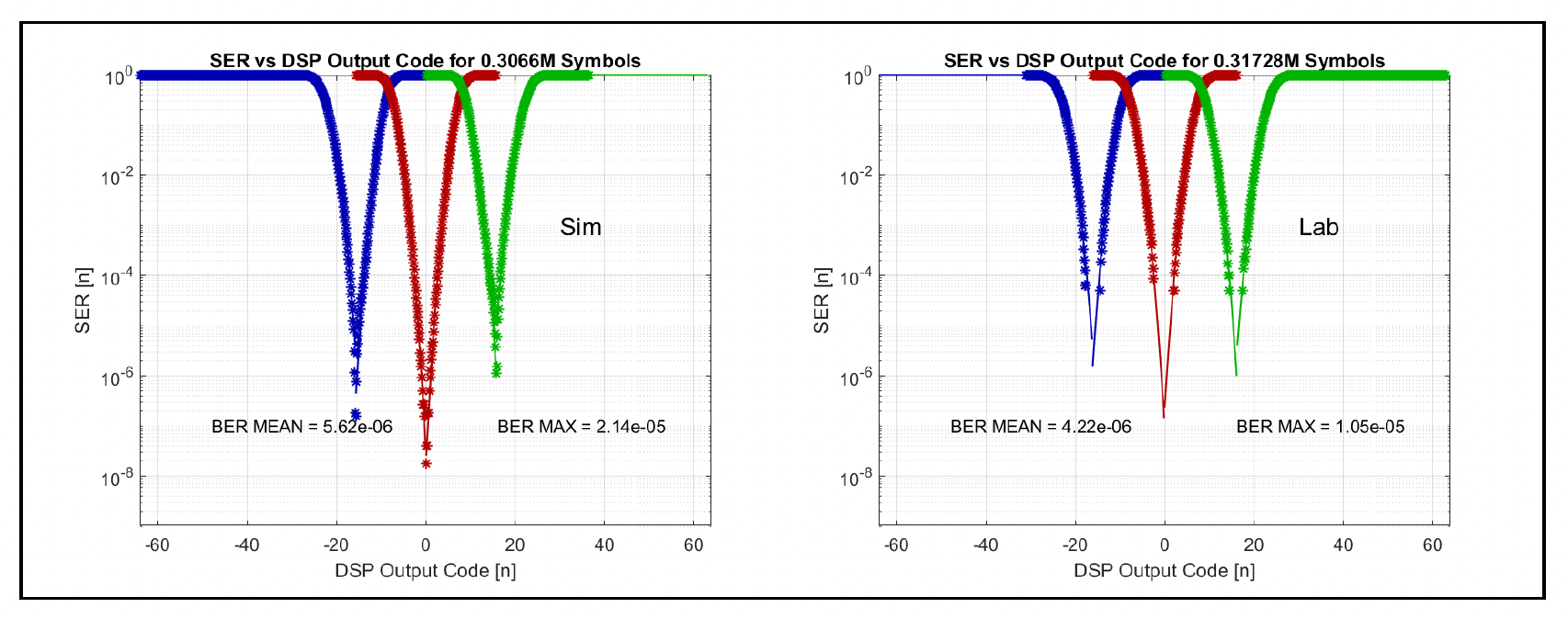

シノプシスの電気光学協調シミュレーション研究では、システム シミュレーションとシリコンを相関付けるプロセスに、実験室での性能特性評価のための詳細なセットアップが含まれていました。セットアップには、BERT、ケーブル、テスト ボード ドーター カード、Ironwood ソケットにあるテスト対象デバイスなどのさまざまなコンポーネントが含まれていました。システム モデルで考慮された s パラメータには、Wildriver、taconic fastrise 12 層ドーター カード、およびテストチップ パッケージからの応答が含まれています。シリコンの結果とシステム シミュレーションの出力を比較すると、両者の相関関係が明らかになりました。全体として、この研究の結果は、シリコンの動作を把握する際のシステム シミュレーション モデルの有効性を強調し、システムのパフォーマンスと最適化に関する貴重な洞察を提供しました。

以下の 4 つのグラフは、シミュレーションとシリコンを比較した場合の、PAMXNUMX レベル、EYE 開口部、および BER パフォーマンスの類似性を示しています。

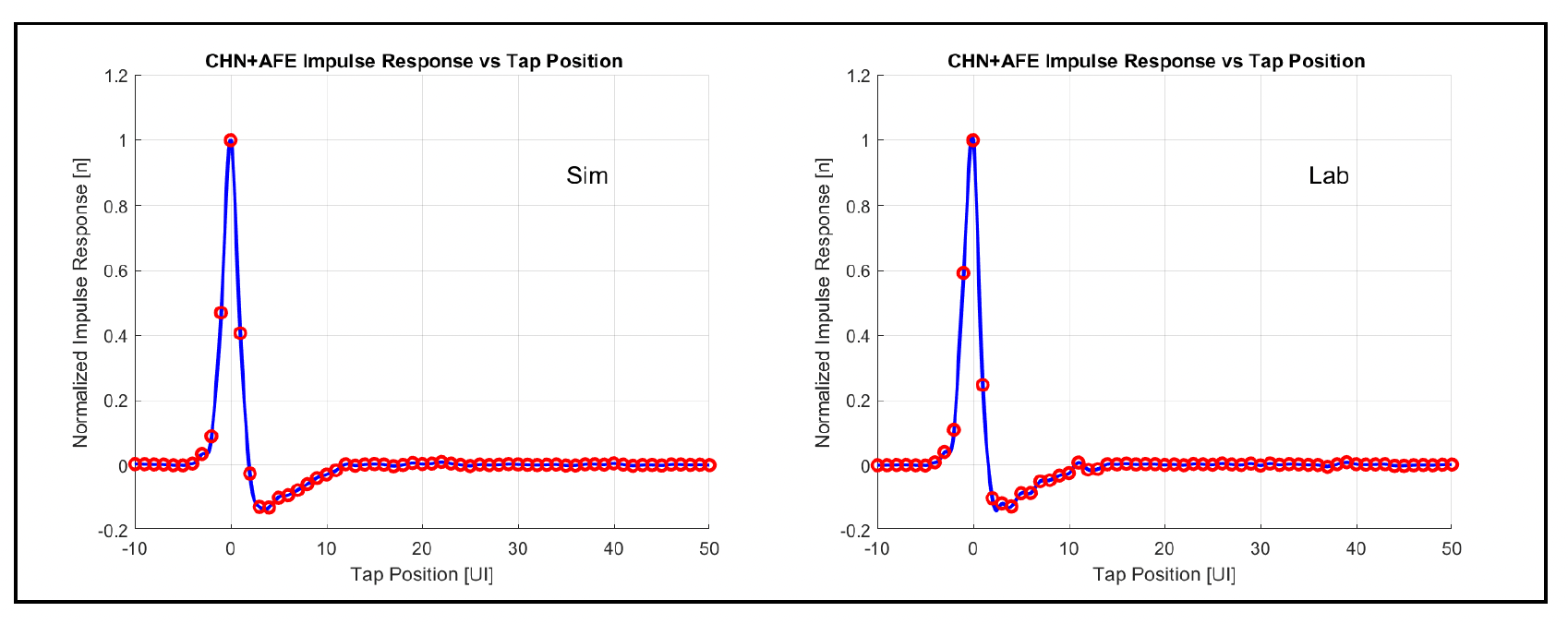

以下のインパルス応答の比較は、シミュレーションとシリコンの間でロック ポイントにわずかな違いがあるものの、全体的な形状の相関関係を示しています。

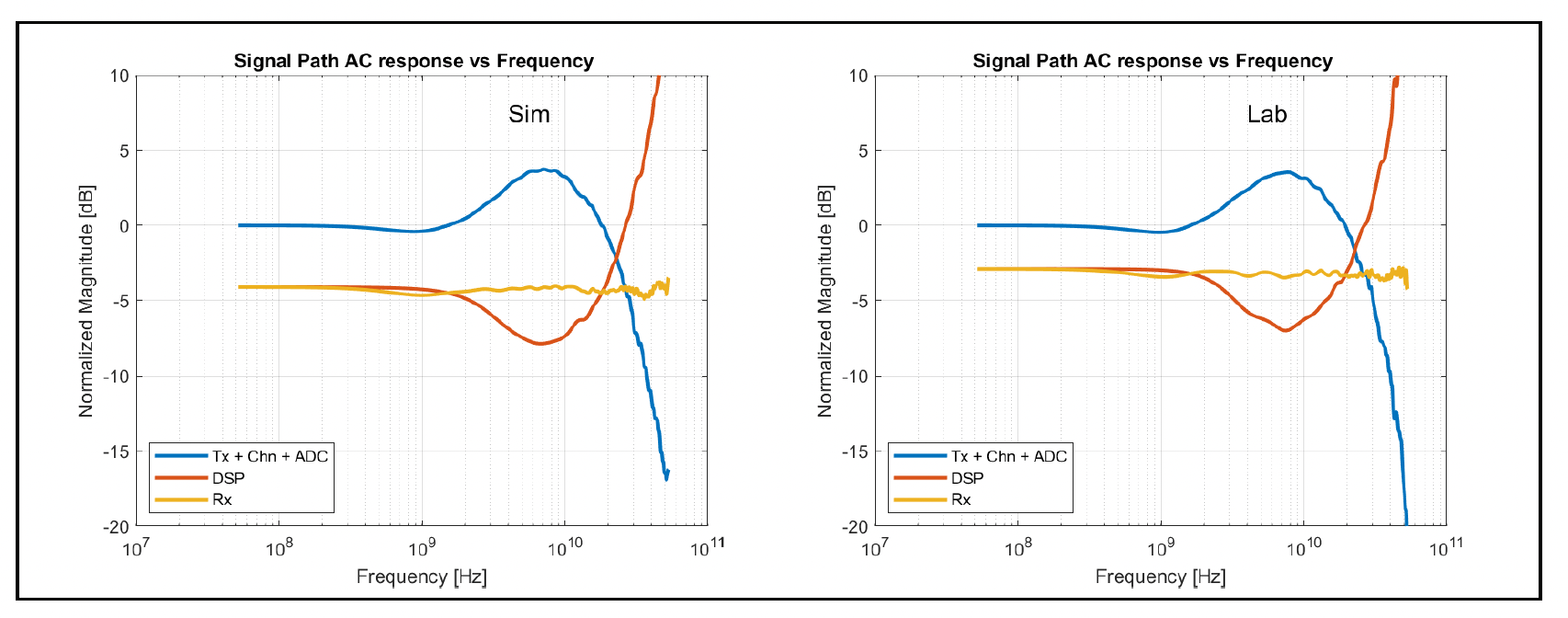

以下のグラフは、DSP が ISI を補償し、全体的なチャネル応答を平坦化する、受信機のイコライゼーション機能を示しています。

以下のグラフは、シミュレーションとシリコンの測定値から FFE 係数と DFE 係数を取得しており、AFE 伝達関数と CDR ロック ポイントの変動に起因するいくつかの違いを示しています。

まとめ

データセンターが 1.6Tbps 時代に移行する中、電気と光の相互接続の統合が、前例のないレベルの接続性、帯域幅、効率性を実現する鍵を握っています。綿密なシステム モデリング、シミュレーション、シリコン実装との相関関係を通じて、設計者はこれらのテクノロジーの可能性を最大限に活用し、データセンター インフラストラクチャの革新とパフォーマンスの新時代を切り開くことができます。高速シリアル リンク、高度な FEC メカニズム、および新たな電気光学インターフェイスの統合により、データ センターは現代のコンピューティングおよびネットワーキング アプリケーションの増大する需要に対応する態勢を整え、前例のない接続性と効率性の未来への道を切り開きます。

詳細および DesignCon で発表された論文全文へのアクセスについては、シノプシスにお問い合わせください。

シノプシスの高速イーサネット ソリューションの詳細については、次のサイトをご覧ください。 www.synopsys.com/ethernet

また読む:

IP から複雑な SoC 設計への自動制約プロモーション手法

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/eda/342124-navigating-the-1-6tbps-era-electro-optical-interconnects-and-224g-links/