IR ドロップとしても知られる電圧垂下は、ワークロードの変動により電力供給ネットワーク内の電流が突然変化するときに発生する現象です。 これにより、システムオンチップ (SoC) 全体の電源電圧降下が発生し、深刻なパフォーマンスの低下を引き起こし、エネルギー効率を制限し、極端な場合には致命的なタイミング障害を引き起こす可能性があります。 これらの問題を回避するために、従来の設計ではクロック周波数、電圧ガードバンド、および/またはソフトウェア ガードバンドを適用することで、電力が増加したり、アーキテクチャが複雑になったり、パフォーマンスが制限されたりします。 また、場合によっては、システム設計者はソフトウェアでのワークロードの管理に取り組むことを余儀なくされることさえあり、これにより複雑さやその他のパフォーマンスの制限が増大します。

よりオーダーメイドのソリューションでは、チームはドループ効果を軽減するために動的に調整する密結合適応回路を採用しています。 ただし、これらの技術には応答時間やアナログの複雑さなどの制限があるため、一部の研究者はオールデジタルの回復力のあるドループ応答ソリューションを調査するようになりました。 このブログ投稿では、シリコン回路の統合または密結合ドループ検出器と適応クロッキングの利点を探ります。

静的ガードバンド

ドループに対処するための従来の技術には、クロック周波数、電圧、およびソフトウェア ガードバンドの使用が含まれます。 これに関連して、周波数ガードバンドとは、電圧低下が発生したときにタイミング グリッチが発生しないように設計者が最大周波数を意図的に下げる技術です。 電圧ガードバンドも同様ですが、設計者が最小電圧 (V分)。 前者はシステム全体のパフォーマンスを低下させることになりますが、後者は平均システム電力を指数関数的に増加させます (V2 関係)。 あるいは、設計チームはソフトウェア ガードバンドを実装して負荷をずらし、スイッチング アクティビティの瞬間的なラッシュを防ぐこともできます。 ただし、これには独自のパフォーマンス上のペナルティが伴い、ソフトウェア、ファームウェア、およびハードウェア スタックのアーキテクチャが複雑になる可能性があります。

図 1: 静的ガードバンディングと電圧垂下による悪影響。

アダプティブ回路とクロック応答

電圧垂下に対する静的ガードバンディングの次のステップは、適応回路です。 アダプティブ回路は、電圧降下によるクリティカル パスのタイミング マージン障害を防ぐように調整するように設計されています。 これらには通常、電源の電圧と電流を監視し、それに応じてクロック周波数を調整する複雑なアナログ制御ループが含まれます。 これは、プルアップ/プルダウン トランジスタを調整するか、発振器のデューティ サイクルを調整することによって行われます。 これらの適応回路の目標は、エネルギー効率を維持しながら、電圧降下によるパフォーマンスの低下を最小限に抑えることです。 これを実現するために、アプリケーション要件に応じて、自己適応クロッキング、動的電源スケーリング、適応電圧スケーリングなどのさまざまな技術が採用されています。 これらの適応技術を利用することで、電圧低下イベントに対するより高いレベルの回復力を提供し、システムのパフォーマンスとエネルギー効率を向上させることができます。

これらの技術には、応答時間とアナログの複雑さの点で重大な制限があります。 適応回路で使用されるアナログ制御ループは複雑で、設計と特性評価が困難な場合があります。 さらに、使用される適応技術は、アナログ回路の速度が遅いことや温度などの外部要因に依存するため、待ち時間が長くなり、突然の電圧降下に十分迅速に反応できない可能性があります。 これにより、急速な電圧低下現象を軽減する効果が制限されます。

オールデジタルの統合ドループ応答ソリューション

近年、研究者らは、電圧降下を軽減する方法として、オールデジタルの回復力のあるタイミングエラー検出および回復回路の使用を検討しています。 これらの技術は、デジタル回路を利用して、遅延を最小限に抑えながらリアルタイムで電圧降下イベントを検出して応答し、アナログベースの技術と比較して、高速降下イベントの検出精度を向上させることができます。 さらに、複雑なアナログコンポーネントに依存しないため、電圧降下に対する高レベルの回復力を提供しながら、プロセスノードに合わせて効率的に拡張できます。 このため、ワークロードの変動がシステムのパフォーマンスとエネルギー効率に及ぼす影響を軽減するための魅力的なソリューションとなります。

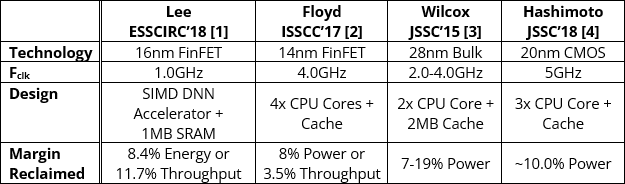

統合または緊密に結合されたドループ検出器と適応クロッキングは、シリコン回路に多くの利点をもたらします。 これらのソリューションは、検出と適応クロック ジェネレーターを組み合わせた密結合 IP を活用します。 統合システムにより、ドループ応答がシステム IP 内で完全に自己完結することが可能になり、適応までの合計時間 (検出 + 適応時間) を驚くほど高速化できます。 さまざまな論文を通じて、研究者らは、密結合ドループ応答により、さまざまなアーキテクチャ (シストリック アレイ、メニーコア CPU アレイ、および GPU) 全体で (10% ドループの場合) システム電力を静的ガード バンディングと比較して 10% 以上削減でき、総消費電力を最小限に抑えることができることを発見しました。適応するまでの時間が 10 倍以上かかります。

表 1: 公開された密結合ドループ応答システムから回収されたマージン。

まとめ

統合または緊密に結合された垂下検出器と適応クロッキングは、主にシステムのパフォーマンスとエネルギー効率を低下させる、ワークロードの変動による電圧垂下による影響を軽減するための有望なソリューションです。 デジタル アーキテクチャを活用して遅延を最小限に抑えたリアルタイム検出を実現し、電源電圧の突然の低下に迅速に対応できます。 さらに、複雑な制御ループを必要とせず、温度などの外部要因によって変化することもないため、アナログベースのソリューションよりも複雑さが軽減され、プロセスの移植性が向上します。 統合または緊密に結合されたドループ応答ソリューションは、自己完結型の迅速なドループ応答ソリューションを作成しながら、システムの大幅な電力節約を実現します。

参考文献

[1] SK リー、P.N. ワットモウ、N. マルホランド、P. ハンセン、D. ブルックス、および G.-Y. Wei、「16 nm FinFET のマルチサイクル バンク SRAM 読み取りおよび適応クロッキングを備えたワイド ダイナミック レンジ スパース FC-DNN プロセッサ」、Proc. IEEE 44th EU. ソリッドステート回路会議(ESSCIRC)、2018 年 158 月、161 ~ XNUMX ページ

[2] MS Floyd et al.、「26.5 電圧垂下保護のための POWER9 プロセッサーの適応クロッキング」、IEEE Int. ソリッドステート回路会議(ISSCC) 掘削。 技術。 Papers、米国カリフォルニア州サンフランシスコ、2017 年 444 月、445-XNUMX ページ

[3] K. Wilcox et al.、「28 nm CMOS の Steamroller モジュールと適応クロッキング システム」、IEEE J. Solid-State Circuits、vol. 50、いいえ。 1、24–34ページ、2015年XNUMX月

[4] T. 橋本他、「SPARC プロセッサ向け 7.5% の周波数ゲインを備えた適応クロック制御回路」、IEEE J. Solid-State Circuits、vol. 53、いいえ。 4、1028–1037ページ、2018年XNUMX月

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- EVMファイナンス。 分散型金融のための統一インターフェイス。 こちらからアクセスしてください。

- クォンタムメディアグループ。 IR/PR増幅。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/mitigating-voltage-droop/