間に ゴマックテック 先週サウスカロライナで開催されたカンファレンスで、Mirabilis Design Inc. の創設者兼技術担当副社長である Deepak Shankar 氏と Zoom 通話を行い、質問したり、ライブ デモを見たりしました。 ビジュアルシム – エレクトロニクスおよび SoC を開発するためのモデリング、シミュレーション、探索および共同作業のプラットフォーム。 VisualSim の特徴は、500 個の ARM プロセッサ、約 35 個のプロセッサ、および 100 を超える異なる相互接続を含む、すぐに使用できる約 30 個の高レベル IP ブロックがバンドルされていることです。 VisualSim のユーザーは、これらの IP ブロックを視覚的にすばやく接続して、ネットワークを備えたシステムを作成します。自動車設計者は、VisualSim を使用して、5G 通信、イーサネット、SDA、OTA アップデートを含むネットワーク全体をモデル化できます。

高レベルのモデルを使用すると、RTL コードで実装が開始されるずっと前に、最も迅速にアーキテクチャを探索し、アーキテクチャのトレードオフを行うことができます。バス、メモリ、さらにはキャッシュなどの複雑なアクティビティをモデル化し、エンドツーエンドの遅延や待ち時間などを測定できます。エンジニアは、キャッシュのヒット/ミス率や、L2 キャッシュへのリクエストで何が起こるかを測定できます。 AXI、CHI、CMN600、Arteris NOC、UCIe などのすべての一般的なネットワーク プロトコルがモデル化されています。

このモデリング アプローチを使用すると、アーキテクトは SoC、完全な航空機または自動車システムをモデル化し、そのパフォーマンスの測定を開始して要件を満たしているかどうかを確認できます。 VisualSim は、アナログ、ソフトウェア、電源システム、デジタル、ネットワークを 1 つのモデルに統合できるマルチドメイン シミュレーターです。

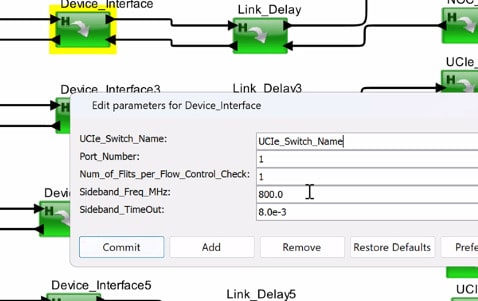

ライブ デモで Deepak は、DSP、GPU、AI プロセッサ、CPU 用の個別のチップレットがすべて UCIe を使用して接続され、各 IP ブロックがカスタマイズと調査を可能にするためにパラメータ化されているチップレット ベースの設計を見せてくれました。

UCIe ブロックにプッシュすると、UCIe スイッチと呼ばれる IP があり、ユーザーはこのブロックを 5 つのパラメーターですべて高レベルでカスタマイズできます。

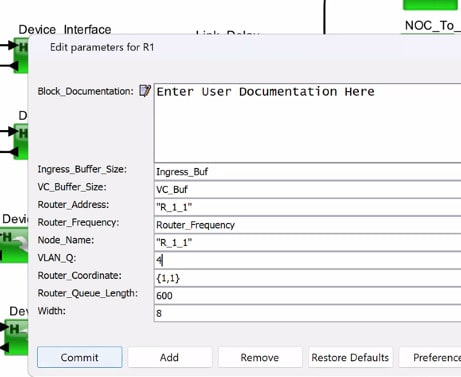

ルーターの IP ブロックには、カスタマイズ用の 10 個のパラメーターがありました。

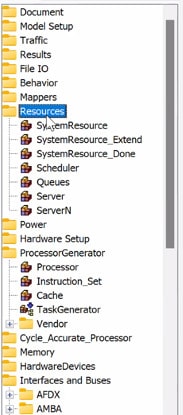

各 IP ブロックを見つけるために、GUI の左側にスクロール可能なリストがあり、ライブラリ内の各 IP ファミリが示されていました。ほんの数秒で、IP を参照して選択し、カスタマイズを開始できます。

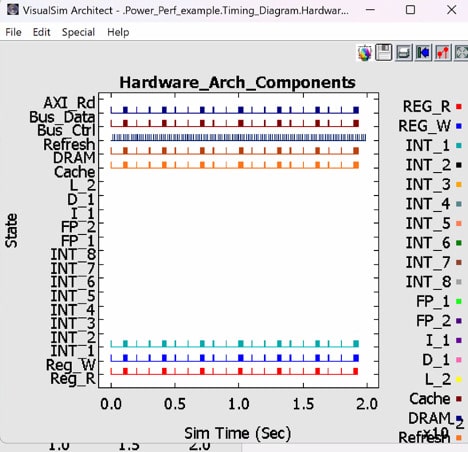

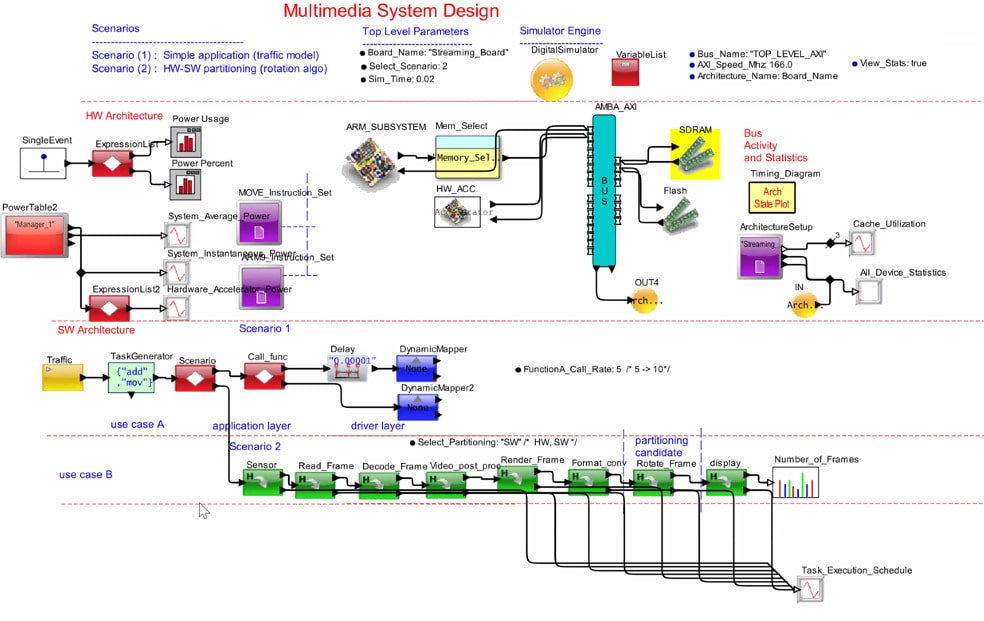

VisualSim では、データフロー内の各 IP を高いレベルで接続します。次のライブ デモはマルチメディア システム設計に関するもので、ラップトップで実行した場合、20 ミリ秒のシミュレーションには約 15 秒の所要時間がかかりました。シミュレーションの実行中、システムのパフォーマンスを瞬間電力として表示したり、パイプライン使用率、キャッシュ使用率、メモリ使用量を測定したり、タイミング図を表示したりすることができます。このリアルタイム シミュレーションは 7.5 万のイベントをトリガーし、顧客は SoC 全体を含むこのモデルを 2 週間以内に構築しました。

Deepak 氏が言及した別の顧客例には 45 個のマスターが含まれており、完全にテストされて約 4 週間で完成しました。

IP ブロックの内部を調べて、合格/不合格などのメトリクスを分析し、失敗した理由を理解できます。障害の原因となったバッファ オーバーフローの発見など、データをより効率的に分析するのに役立つ AI エンジンもあります。モデルの実行中に、システムのパフォーマンスを測定し、アーキテクチャ上のボトルネックを特定するために収集される分析が行われます。

VisualSim は年に 2 回更新され、新しい IP ブロックが追加された場合にはパッチ更新が行われます。アーキテクトは、遅延制限やバッファ占有率などのメトリクスを使用して、Excel ファイルで要件を定義します。

VisualSim のユーザーは、バイト、速度範囲、優先値の観点からペイロード サイズの範囲を定義できます。システム モデルをさまざまな組み合わせでスイープして、最適なパラメーターのセットを見つけることができます。シミュレーターは、最小値、最大値、推奨値を調べる方法も理解します。どのシステムパラメータを調査するかを定義できます。次にマルチメディア システムのデモが表示され、ライブでシミュレーションが行われました。

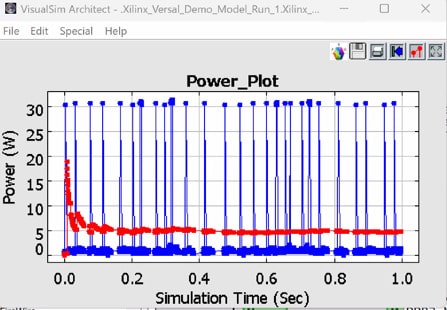

FPGA ブロックの場合、ベンダーと部品番号を選択すると、シミュレーションの実行後に各タスクのレイテンシと NOC のチャネル統計を確認できます。 Xilinx Versal 部品を使用した場合の 1 秒間の動作時の電力プロットが表示されました。

すべてのライブ デモは Windows ラップトップ上で実行されました。その他のサポートされる OS は、Unix、Mac です。モデルは高レベルであるため、VisualSim を実行するには最小限の HW インフラストラクチャが必要です。

VisualSim ユーザーは、アンテナ、トランシーバー、ベースバンドを備えた FPGA、およびイーサネット インターフェイスを備えた完全な通信システムなど、すぐに開始できるように事前に構築された 500 を超えるサンプルを受け取ります。 VisualSim を使用するシステム アーキテクトは、RTL 設計者などの下位レベルの専門家全員と協力できます。

システムレベルのトレードオフは、次のようにモデル化して評価できます。

- 64-QAM から QPSK 変調への変更

- 高速プロセッサから低速プロセッサへ

- イーサネット仕様の変更

VisualSim を使用してモデル化、実装、測定を開始すると、RTL 実装の結果と比較して 95% の精度が得られることが期待されます。高レベルのモデルを使用すると、実装または統合の前にパフォーマンスの問題を解決できることが約束されます。実際、システム モデル全体にコーディングは必要ありません。

Mirabilis にはこれまでに世界中に 65 社の顧客があり、約 250 のプロジェクトが完了しました。有名なクライアントには、NASA、Samsung、Qualcomm、Broadcom、GM、Boeing、HP、Imagination、Raytheon、AMD、Northrup Grumman などがあります。

まとめ

昔、システム設計者はレストランで食事中にナプキンにアイデアを書き出し、その後仕事に戻り、難解な方程式を含む Excel スプレッドシートを組み合わせてモデルを作成したかもしれません。今日、新しい選択肢があり、それが与えられています ビジュアルシム ミラビリスから試してみます。わずか数週間でシステム全体をモデル化し、実装の詳細に入る前に、実際のシミュレーションを実行しながらアーキテクチャ上のトレードオフを行うことができるようになりました。

関連ブログ

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/