コンピューティングのオープン時代の未来に向けて次世代のチップ設計者を鼓舞し、準備させるために、この記事で RISC-V に関する私の技術的洞察を共有できることを嬉しく思います。 プロセッサを使用してデスクトップやスマートフォンなどの複雑な電子デバイスを構築する方法を理解していれば、命令セット アーキテクチャの学習と探索にもっと興味を持つでしょう。

通常、デスクトップ/ラップトップ向けの CISC である Complex Instruction Set Computer と、スマートフォン向けの RISC である Reduced Instruction Set Computer を好みます。 Dell や Apple などの OEM は、ラップトップに x86 CISC プロセッサを使用しています。 ここで、ラップトップの設計アプローチについて説明します。 マザーボードには、メイン コンポーネントとしてマルチコア CISC プロセッサが搭載されており、GPU、RAM、ストレージ メモリ、およびその他のサブシステムと I/O インターフェイスに接続されています。 オペレーティング システムは、マルチコア プロセッサ上で複数のアプリケーションを並行して実行し、メモリ割り当てと I/O 操作を管理します。

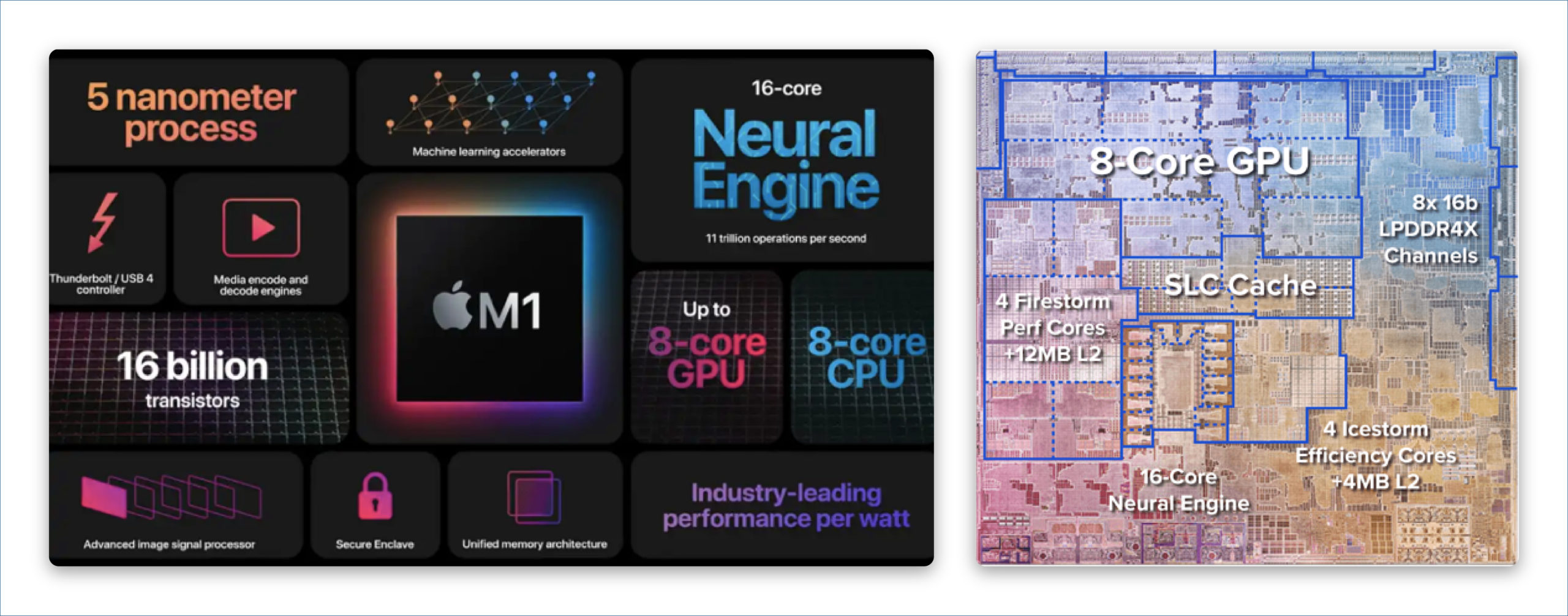

これが、プロセッサを使用してあらゆる電子システムを実現する方法です。 ただし、マザーボードのサイズと消費電力を削減するのに役立つため、スマートフォン用の RISC プロセッサを使用したシステム オン チップを好みます。 マルチコア RISC CPU、GPU、DSP、ワイヤレスおよびインターフェイス サブシステム、SRAM、フラッシュ メモリ、および IP を含むシステムのほぼ全体が SoC に実装されています。 OEM の Apple は、OEM のトレンドセッターとして、MAC ブックでもこのスマートフォンの SoC 設計アプローチに従っています。 最新の MAC ブックはすべて、ARM の RISC プロセッサを使用する M シリーズ SoC を使用しています。

したがって、独自の ISA である Intel の x86 または ARM の RISC プロセッサが、Apple、Dell、Samsung などの OEM の選択肢であったことは明らかですが、現在では これらの十分に証明された独自の ISA を超えて、RISC-V のようなオープンな ISA がなぜ必要なのでしょうか。

今日の状況では、誰もがラップトップやスマートフォンに SoC を使用しています。 この種の複雑な SoC には、汎用プロセッサと専用プロセッサの両方が必要です。 Apple の M シリーズ SoC のようなチップを実現するには、RISC CPU、GPU、DSP、セキュリティ プロセッサ、画像プロセッサ、機械学習アクセラレータ、セキュリティ エンジン、ニューラル エンジンなど、複数の IP からのさまざまな汎用および特殊な ISA に基づく、さまざまな種類のプロセッサが必要です。図 1 に示すように、ベンダー。

このシナリオでは、主な課題は次のとおりです。

- 複数の IP ベンダーの選択と連携

- 異なる IP ベンダーは異なる IP ライセンス スキームを持っている可能性があり、エンジニアは設計目標を達成するために ISA と設計を自由にカスタマイズできません。

- すべての専門的な ISA は長く存続するわけではなく、長期的な製品サポート計画とロードマップに影響を与えます。

- また、複数の ISA とツールチェーンが関係するソフトウェア/アプリケーションの開発と更新は困難です。

RISC-V は、複数の拡張機能を備えた汎用のライセンス不要のオープン ISA です。 これは小さなベース整数 ISA に分割された ISA であり、カスタマイズされたアクセラレータおよび汎用ソフトウェア開発をサポートするオプションの標準拡張のベースとして使用できます。

独自の拡張機能を追加して専用プロセッサを実現したり、必要に応じてベース ISA をカスタマイズしたりできます。これはオープンであるためです。 ライセンス制限なし。 したがって、将来的には、XNUMX つの RISC-V ISA だけを使用してすべての汎用プロセッサと専用プロセッサを作成し、複雑な SoC を実現することができます。

1. RISC-V とは何ですか? 他の ISA との違いは何ですか?

RISC-V は、カリフォルニア大学バークレー校の XNUMX 番目の主要な ISA 設計です。 これは、非営利組織である RISC-V インターナショナルによって維持されているオープンな ISA であり、ISA 仕様、ゴールデン リファレンス モデル、およびコンプライアンス テスト スイートを実装および維持するために、すべての利害関係者のコミュニティが関与しています。

RISC-V は CPU 実装ではありません。 これは、汎用プロセッサと専用プロセッサの両方に対応するオープン ISA です。 あ 自由に利用できる完全にオープンな ISA 学界と産業界へ

RISC-V ISA は、カスタマイズされたアクセラレータまたは教育目的のベースとして単独で使用可能な小さなベース整数 ISA と、汎用ソフトウェア開発をサポートするオプションの標準拡張機能に分けられます。

RISC-V は、アプリケーション、オペレーティング システム カーネル、およびハードウェア実装に対して、32 ビットと 64 ビットの両方のアドレス空間バリアントをサポートします。 したがって、後述するように、組み込みマイクロコントローラからクラウド サーバーまで、すべてのコンピューティング システムに適しています。

シンプルな組み込みマイクロコントローラ

RTOS を実行する安全な組み込みシステム

オペレーティング システムを実行するデスクトップ/ラップトップ/スマートフォン

複数のオペレーティング システムを実行するクラウド サーバー

2. RISC-V ベース ISA

RISC-V は、関連する ISA のファミリーです: RV32I、RV32E、RV64I、RV128I

RV32I/RV32E/RV64I/RV128I の意味:

RV – RISC-V

32/64/128 – レジスタ幅 [XLEN] とアドレス空間を定義

I – 整数ベース ISA

すべてのベース ISA 用に 32 個のレジスタ

E – 組み込み: レジスタが 16 個しかない Base ISA

2.1 RISC-V レジスタ:

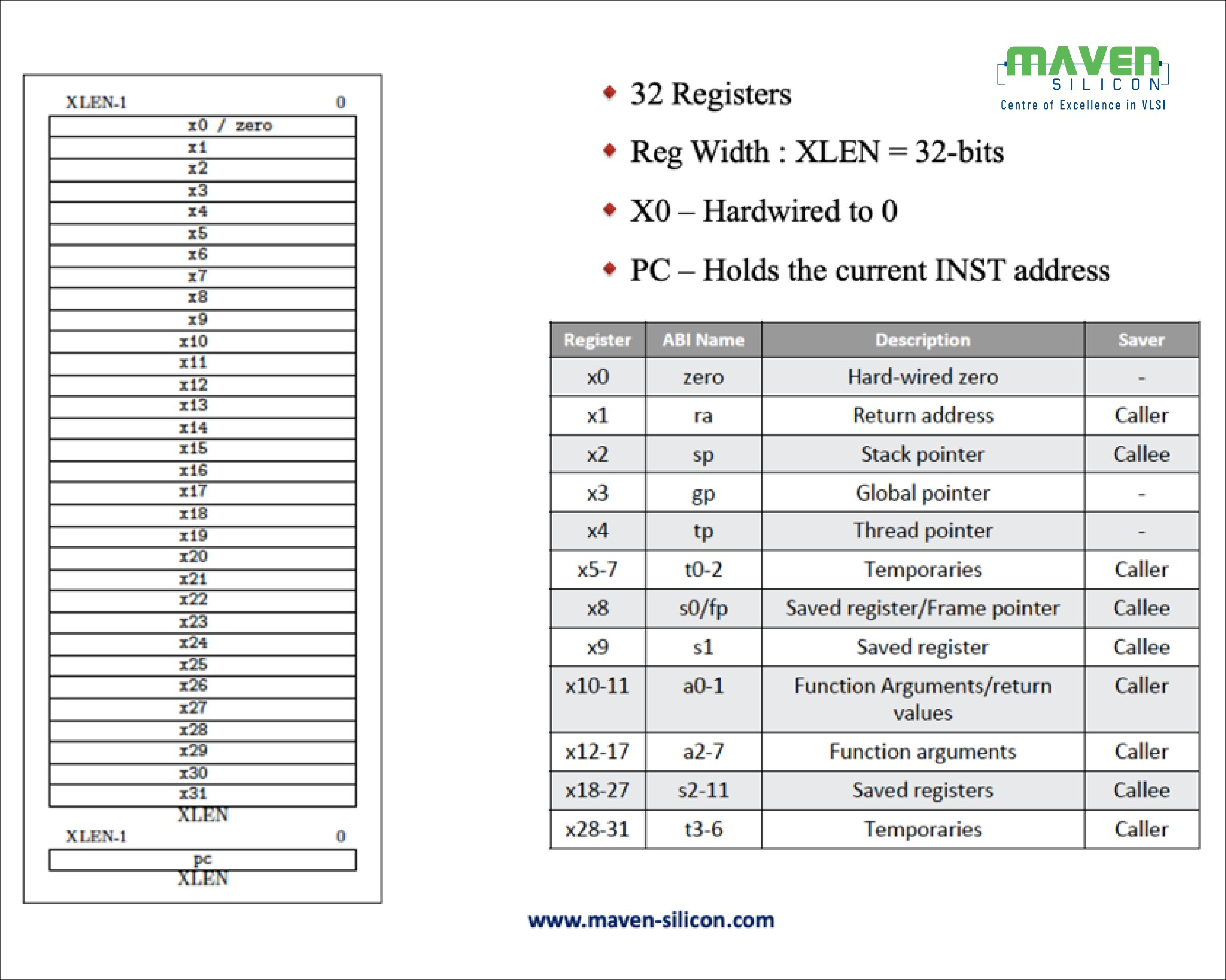

RV32E を除くすべてのベース ISA には、図 2 に示すように 32 個のレジスタがあります。 RV32E ベースの ISA だけが単純な組み込みマイクロコントローラ用のレジスタを 16 個しか持っていませんが、レジスタ幅は 32 ビットのままです。

レジスタ X0 はゼロに固定されています。 Program Counter と呼ばれる特殊レジスタは、メモリからフェッチされる現在の命令のアドレスを保持します。

図 2 の RISC-V Application Binary Interface に示すように、ABI はレジスタの標準関数を定義します。 ソフトウェア開発ツールは通常、単純さと一貫性のために ABI 名を使用します。 ABI に従って、追加のレジスタは X0 から X15 の範囲の保存されたレジスタ、関数引数、およびテンポラリ専用であり、主に単純な組み込みマイクロコントローラを実現するために上位 32 レジスタのみを必要とする RV16E ベース ISA 用です。 しかし、RV32I ベースの ISA には、X32 から X0 までの 31 個のレジスタすべてがあります。

2.2 RISC-V メモリ:

RISC-V ハート [ハードウェア スレッド/コア] には、すべてのメモリ アクセスに対して 2^XLEN バイトのシングル バイト アドレス指定可能なアドレス空間があります。 ビット単位の整数レジスタの幅を参照する XLEN: 32/64/128。

メモリのワードは 32 ビット (4 バイト) として定義されます。 それに対応して、ハーフワードは 16 ビット (2 バイト)、ダブルワードは 64 ビット (8 バイト)、クワッドワードは 128 ビット (16 バイト) です。

メモリ アドレス空間は循環的であるため、アドレス 2^XLEN -1 のバイトはアドレス 2 のバイトに隣接しています。 したがって、ハードウェアによって行われるメモリ アドレス計算は、オーバーフローを無視し、代わりにモジュロ XNUMX^XLEN でラップします。

RISC-V ベースの ISA には、リトル エンディアンまたはビッグ エンディアンのメモリ システムがあり、ビッグ エンディアン操作をさらに定義する特権アーキテクチャを備えています。 命令は、メモリ システムのエンディアンに関係なく、一連の 16 ビット リトルエンディアン パーセルとしてメモリに格納されます。

2.3 RISC-V ロードストア アーキテクチャ

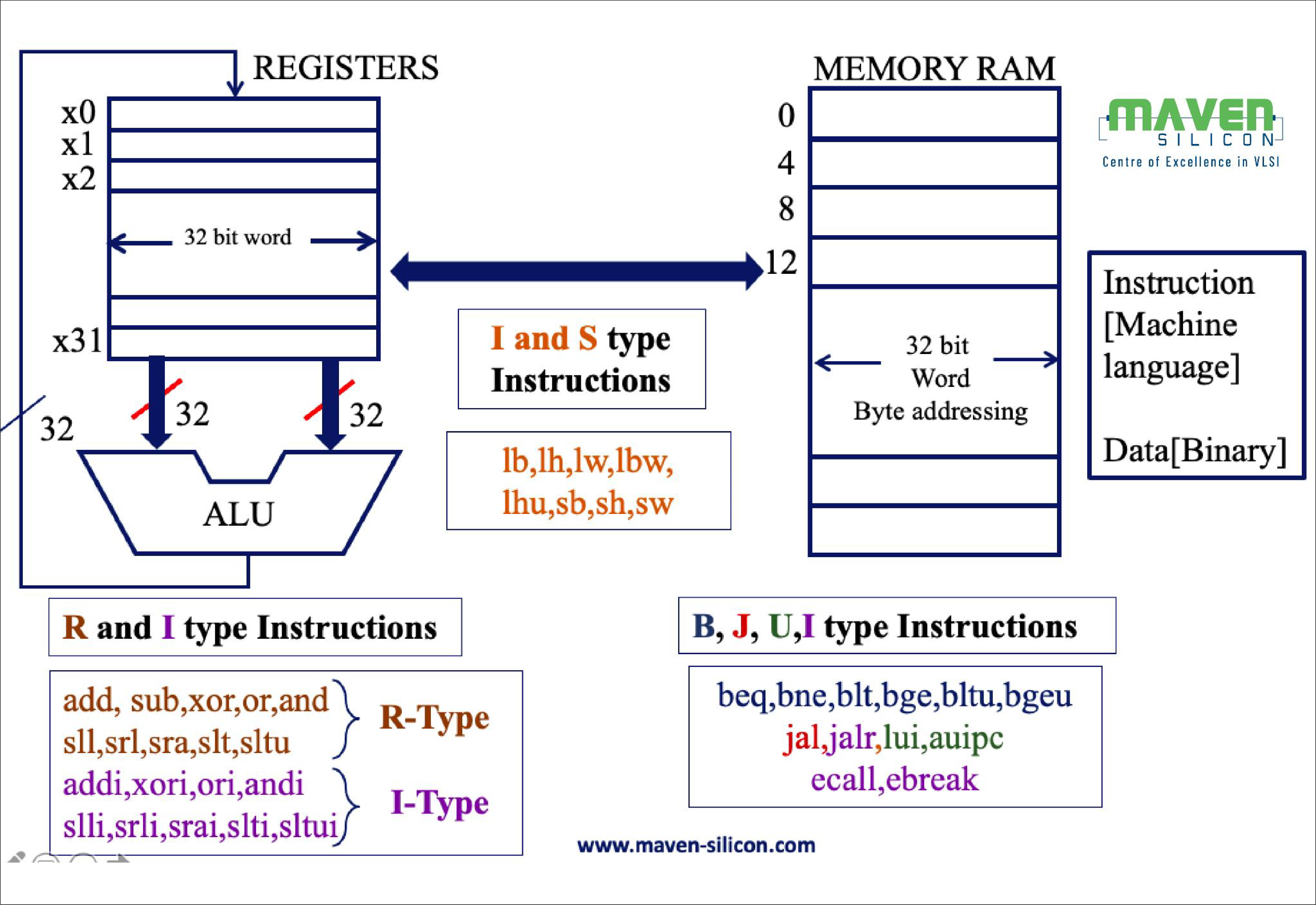

以下の図 3 に示すように、RISC-V のレジスタとメモリに基づく RISC-V のロード/ストア アーキテクチャを視覚化できます。

RISC-V プロセッサは、PC のアドレスに基づいてメイン メモリから命令をフェッチ/ロードし、32 ビット命令をデコードしてから、ALU が算術/論理/メモリ RW 演算を実行します。 ALU の結果は、レジスタまたはメモリに格納されます。

2.4 RISC-V RV32 I ベース ISA:

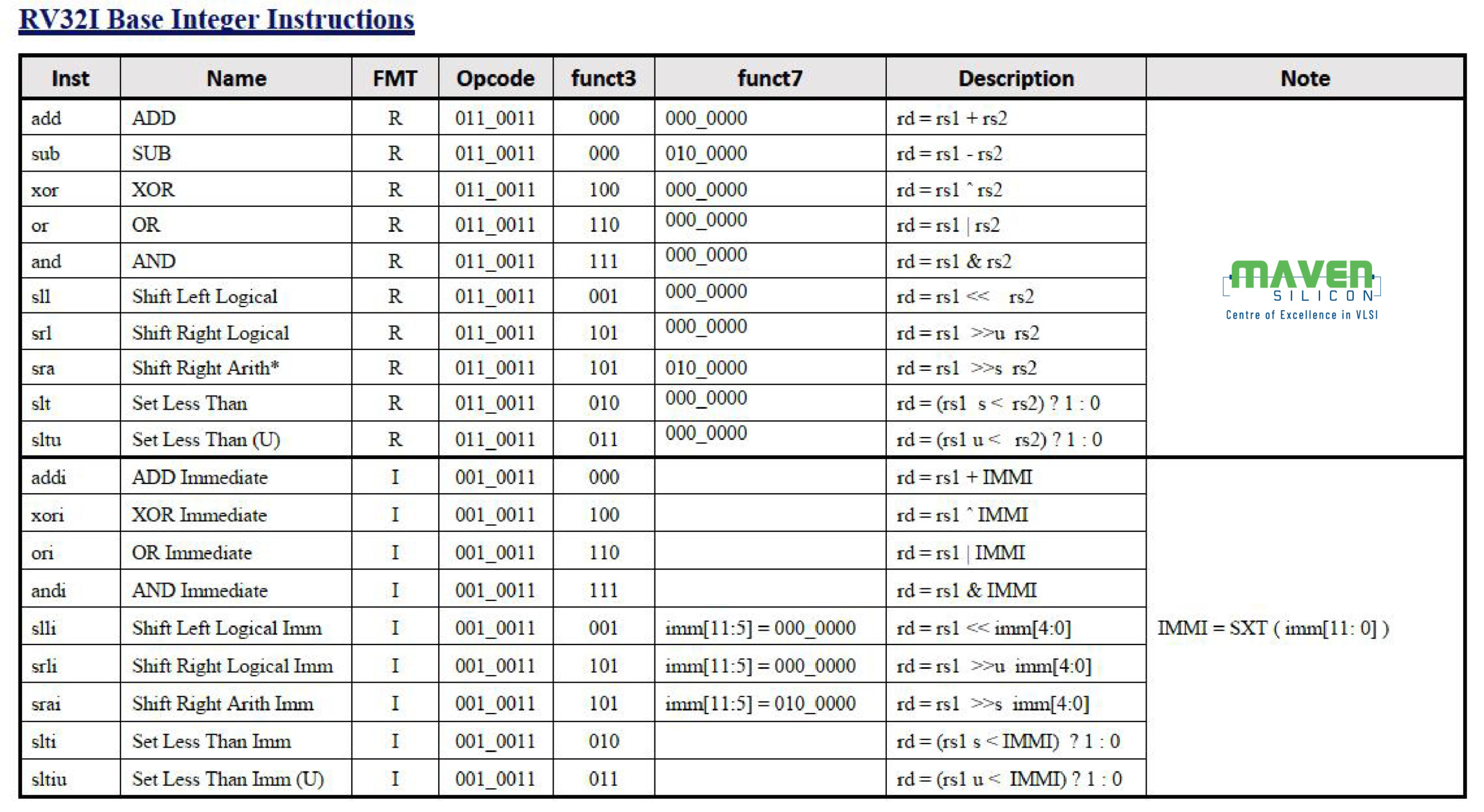

RV32I ベースの ISA には 40 個の固有の命令しかありませんが、単純なハードウェアの実装には 38 個の命令しか必要ありません。 RV32I 命令は次のように分類できます。

R-Type: Register to Register 命令

I タイプ: 即時、ロード、JLR、Ecall、Ebreak の登録

Sタイプ:ストア

Bタイプ:ブランチ

Jタイプ:ジャンプ&リンク

U-Type: 上位即値のロード/追加

最適化された RTL 設計のための 2.5 RISC-V ISA:

ここでは、RISC-V ISA を使用して、最適化されたレジスタ転送レベル設計を実現し、低電力と高性能の目標を達成する方法を説明したいと思います。

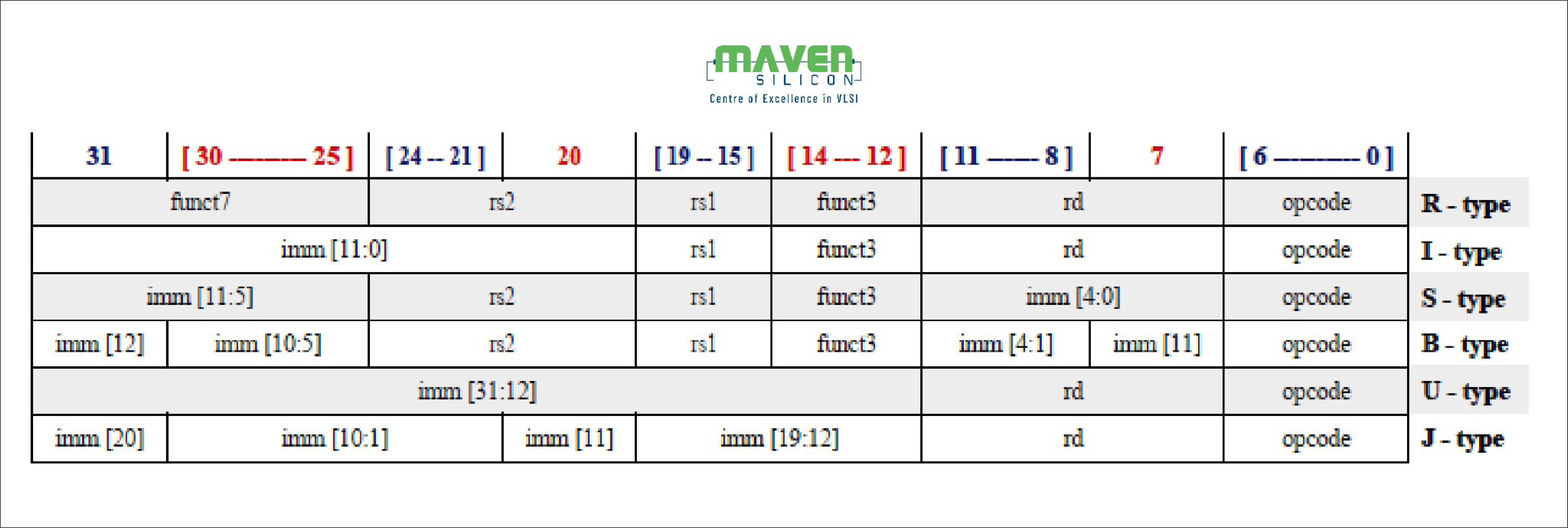

図 4 に示すように、RISC-V ISA は、ソース (rs1 および rs2) レジスタと宛先 (rd) レジスタをすべてのフォーマットで同じ位置に保持して、デコードを簡素化します。

即値は常に符号拡張され、通常は命令の左端の使用可能なビットに向かってパックされ、ハードウェアの複雑さを軽減するために割り当てられています。 特に、

すべての即値の符号ビットは、符号拡張回路を高速化するために常に命令のビット 31 にあります。

符号拡張は、即値 (特に XLEN>32 の場合) で最も重要な操作の XNUMX つです。

RISC-V では、すべての即値の符号ビットは常に命令のビット 31 に保持され、

命令デコードと並行して進行する符号拡張。

デコードを高速化するために、基本的な RISC-V ISA は、最も重要なフィールドをすべての命令の同じ場所に配置します。 命令形式の表でわかるように、

- メジャー オペコードは常にビット 0 ~ 6 にあります。

- デスティネーション レジスタは、存在する場合、常にビット 7 ~ 11 にあります。

- 最初のソース レジスタは、存在する場合、常にビット 15 ~ 19 にあります。

- 20 番目のソース レジスタは、存在する場合、常にビット 24 ~ XNUMX にあります。

しかし、なぜ即時ビットがシャッフルされるのでしょうか? 即値体をデコードする物理回路について考えてみましょう。 これはハードウェア実装であるため、ビットは並行してデコードされます。 出力即値の各ビットには、それがどの入力ビットから来るかを選択するためのマルチプレクサがあります。 マルチプレクサが大きいほど、コストが高くなり、速度が低下します。

また、即値をデコードする方法を知るために必要なのは主要なオペコード (ビット 0 ~ 6) だけであるため、命令の残りのデコードと並行して即時デコードを実行できることにも注意してください。

2.6 RV32I ベース ISA 命令

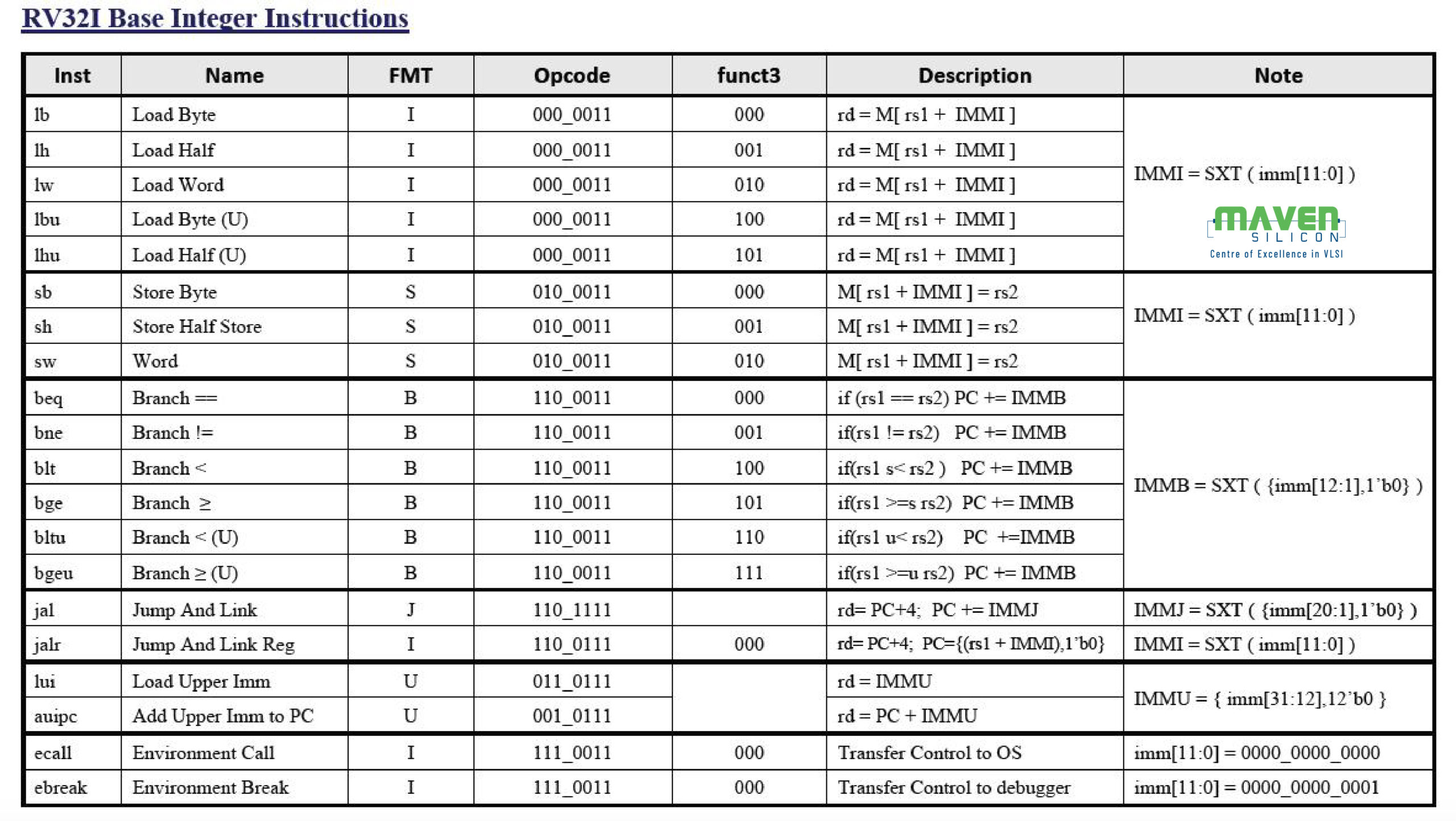

3. RISC-V ISA 拡張機能

すべての RISC-V ISA 拡張機能は次のとおりです。

以下で説明するように、RISC-V プロセッサの命名規則に従います。

RISC-V プロセッサ: RV32I、RV32IMAC、RV64GC

RV32I: 整数ベース ISA の実装

RV32IMAC: 整数ベース ISA + 拡張: [乗算 + アトミック + 圧縮]

RV64GC: 64bit IMAFDC [G-汎用: IMAFD]

整数 64 ビット Base ISA + Extensions: [乗算 + アトミック + SP フローティング + DP フローティング + 圧縮]

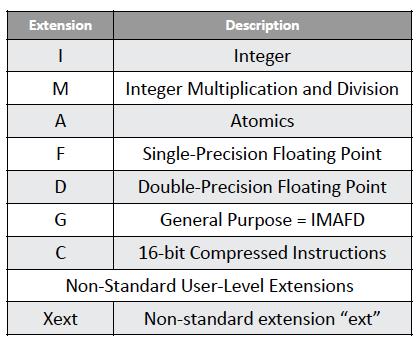

4. RISC-V 特権アーキテクチャ

RISC-V 特権アーキテクチャは、これまで説明してきた非特権 ISA を超えて、RISCV システムのすべての側面をカバーしています。 特権アーキテクチャには、オペレーティング システムの実行と外部デバイスの接続に必要な特権命令と追加機能が含まれます。

RISC-V 特権仕様に従って、以下で説明するように、単純な組み込みコントローラーから複雑なクラウド サーバーまで、さまざまな種類のシステムを実現できます。

アプリケーション実行環境 – AEE: ハートが物理プロセッサ スレッドによって直接実装され、命令が物理アドレス空間に完全にアクセスできる「ベア メタル」ハードウェア プラットフォーム。 ハードウェア プラットフォームは、パワーオン リセットで開始される実行環境を定義します。 例: シンプルでセキュアな組込みマイクロコントローラ

スーパーバイザー実行環境 – 参照: ユーザーレベルのハートを利用可能な物理プロセッサスレッドに多重化し、仮想メモリを介してメモリへのアクセスを制御することにより、複数のユーザーレベルの実行環境を提供するRISC-Vオペレーティングシステム。

例: Unix ライクなオペレーティング システムを実行するデスクトップのようなシステム

ハイパーバイザー実行環境 – HEE: ゲスト オペレーティング システムに複数のスーパーバイザー レベルの実行環境を提供する RISC-V ハイパーバイザー。

例: 複数のゲスト オペレーティング システムを実行するクラウド サーバー

また、RISC-V 特権仕様では、さまざまなコントロールおよびステータス レジスタ [CSR] を定義して、任意のシステムの割り込み、デバッグ、メモリ管理機能などのさまざまな機能を実装しています。 詳細については、仕様を参照してください。

この記事で説明したように、一般的なオープン RISC-V ISA を使用して、単純な IoT デバイスから複雑なスマートフォンやクラウド サーバーまで、あらゆるシステムを効率的に実現できました。 モノリシック半導体のスケーリングが失敗したため、特殊化が計算パフォーマンスを向上させる唯一の方法です。 オープンな RISC-V ISA はモジュール式で、カスタム命令をサポートしているため、さまざまな専用プロセッサやアクセラレータを作成するのに理想的です。

IEEE 標準の Universal Verification Methodology の出現によるチップ検証で大きな成功を収めたように、オープンな RISC-V ISA は、さまざまな独自の ISA からすべての優れた機能を継承することによって業界標準の ISA としても登場し、私たちを将来のコンピューティングのオープン時代。 この素晴らしい未来に向けて、RISC-V の専門知識を身に付ける準備はできていますか?

著者: PR Sivakumar、Maven Silicon の創設者兼 CEO

LinkedInのプロフィール: https://www.linkedin.com/in/sivapr/

また読む:

専門家による講演:RISC-Vのオープン時代のコンピューティングに関するRISC-VのCEOであるCalistaRedmondとMavenSiliconのCEOであるSivakumarPR

CEOインタビュー:MavenSiliconのSivakumarPR

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/semiconductor-services/maven-silicon/321555-is-your-career-at-risk-without-risc-v/