At booth #2430, the Easylogic technical support team will guide you through the GTECH design flow, offer in-depth product demos, engage in discussions about your ECO applications, and provide tailored recommendations.

Common feedback from customers is that the ECO flow is cumbersome and requires extensive inter-tool compatibility knowledge to function correctly. ECO tasks typically begin with identifying the need for change, which requires equivalence checking tools to pinpoint all differences. Formal tools can easily misinterpret certain types of RTL modifications if the environment settings are not specified perfectly. These incorrect mismatches become unnecessary ECO points, leading to unnecessary ECO patches, which increase the difficulty of the ECO task and extend the tool runtime exponentially.

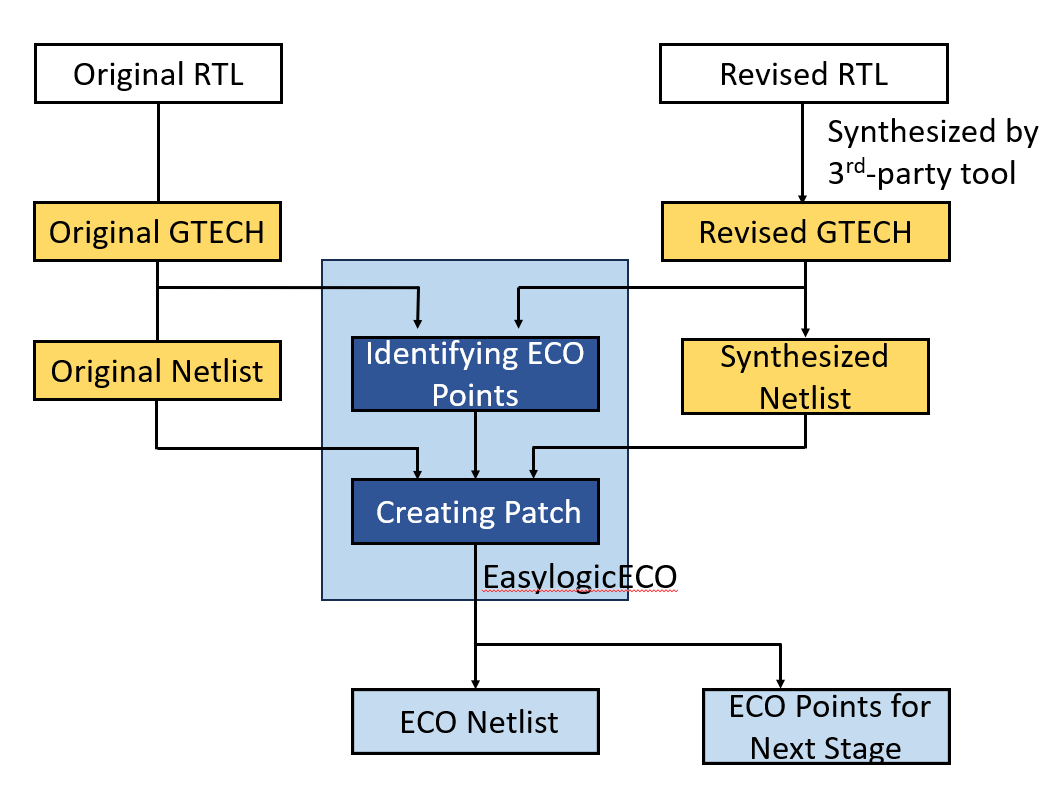

EasylogicECO’s performance goal has always been to create the smallest ECO patch logics with the least amount of user effort. Smaller patch logics help achieve timing convergence and reduce mask costs if a metal ECO is required. The simplicity of the ECO design flow offers users peace of mind, knowing the flow will work without any help of tool flow experts. Based on these two market demands, Easylogic developed an innovative ECO approach. This year at DAC, Easylogic will demonstrate its groundbreaking GTECH-based ECO optimization methodology (US patent pending), designed to elevate the functional ECO solution to the next level.

GTECH netlist, which is the mapped result of the revised RTL design before performing logic optimizations, represents the genuine RTL behavior without the ambiguity of RTL syntax interpretation. Meanwhile, GTECH sufficiently provides the netlist information for tracing the gate-level optimization results downstream, which is critical in identifying the ECO point at the gate-level netlist.

EasylogicECO’s innovation is two-folded: a GTECH reader and a built-in equivalence checking engine, specifically engineered for ECO purpose. The combination not only eliminates false discrepancies created by most commercial formal tools during RTL-to-RTL equivalence checking, but also creates an internal database to enable faster, broader, more precise ECO patch optimizations at the final netlist level, enhancing the robustness of its RTL-based design flow in terms of patch sizes and ease of use.

All the work mentioned above is performed under the hood. By deploying its own application-specific equivalence checking, EasylogicECO obtains the required design information for functional ECO optimization first-hand. The equivalence checking deploys a unique algorithm to automatically filter out unnecessary mismatches. Users just need to specify the proper input files, and EasylogicECO takes care of the rest – no need to set sophisticated conditions for 3rd-party equivalence checking tool anymore.

Also Read:

ECO Demo Update from Easy-Logic

Share this post via:

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiwiki.com/eda/easy-logic/346463-easylogic-at-the-2024-design-automation-conference/