Die zunehmenden Herausforderungen und steigenden Kosten der Logikskalierung sowie die Nachfrage nach immer mehr Funktionen zwingen immer mehr Unternehmen zu fortschrittlicher Verpackung. Und obwohl dies eine Menge neuer Optionen eröffnet, sorgt es auch für große Verwirrung darüber, was für verschiedene Prozesse und Technologien am besten funktioniert.

Im Kern hängt fortschrittliches Packaging von zuverlässigen Verbindungen, klar definierten Signalpfaden und der Minimierung störender Effekte wie Einfügungsverluste, Übersprechen der Verbindungen, Substratverzug und Hotspots im System ab. Diese Parameter können je nach Wahl des Gehäuses erheblich variieren. Dabei kann es sich um 2.5D-Gehäuse, Fan-Out-Chip-on-Substrat-Gehäuse (FOCoS), 3D-ICs oder Brücken handeln, die separat oder in Verbindung mit den anderen Ansätzen verwendet werden können .

Und das ist nur der Anfang. Roadmaps für Halbleiterverpackungen legen immer Wert auf robuste Schnittstellen, aber welche für eine bestimmte Anwendung die richtige ist, ist nicht immer klar, da es viele Möglichkeiten gibt, zu einem Endergebnis zu gelangen. Es gibt auch eine Reihe neuer Prozesse, darunter Wafer-zu-Wafer-Bonding, rückseitige Stromverteilung und Co-Packaging von Optiken in Gehäusen. Silizium-Interposer (Brücken) bieten die Kommunikation mit der höchsten Bandbreite, während organische Interposer deutlich kostengünstiger sind und passive Elemente entlang der Verbindungsroute vom RDL zum C4-Bumping einbetten können.

Neue Materialien und Architekturen

Seit der Erfindung des ersten IC haben Ingenieure die Grundlagen eines Materials im Vergleich zu einem anderen diskutiert. In den Anfängen ging es um Silizium-Halbleiter versus Germanium-Halbleiter, immer mit dem Endziel, kostengünstige Elektronik herzustellen. Die große Menge an Silizium und seine Fähigkeit, ein natives Oxid zu bilden, erleichterten die Integration und sorgten für Zuverlässigkeit, was es zum Substrat der Wahl machte.

Heute erlebt die Herstellbarkeit in fortschrittlichen Verpackungen eine ähnliche Metamorphose wie einst ASICs. In den Bereichen Medizin, Biotechnologie, HPC, Mobilfunk und 5G/6G greifen Ingenieure auf physikalische und chemische Prinzipien zurück, um herauszufinden, wie sich Photonik, Mikroelektronik, Siliziumbrücken mit Umverteilungsschichten und Chipkommunikation mit medizinischer Elektronik am besten kombinieren lassen.

Der Trick besteht darin, Chips mithilfe einer robusten Architektur zu Gehäusen zu entwickeln, die Temperaturbelastungszyklen standhält und einem bestimmten Anwendungsfall standhält.

Gleichzeitig stehen Chiphersteller unter dem Druck, Module auf Systemebene früher zu liefern. Ironischerweise erfordert dies in einigen Fällen Prozesse mit niedrigeren Temperaturen, um Geräte effektiv näher beieinander und an neuen Orten, beispielsweise im menschlichen Körper, einzubetten.

„Es gibt nur eine begrenzte Menge an Metallen, die wir für implantierbare Geräte verwenden können, etwa Gold, Platin und einige Chromstähle. Wir können Aluminiumoxid verwenden, aber nur wenige Polymere sind geeignet, wenn sie organischen Medien ausgesetzt werden“, sagte Dick Otte, CEO von Promex. Bestehende Prozesse können für neue Anwendungen wie implantierbare medizinische Geräte oder Einwegtester zur Erkennung des Glukosespiegels oder eines Krankheitserregers wie eines Covid-Virus entwickelt werden.

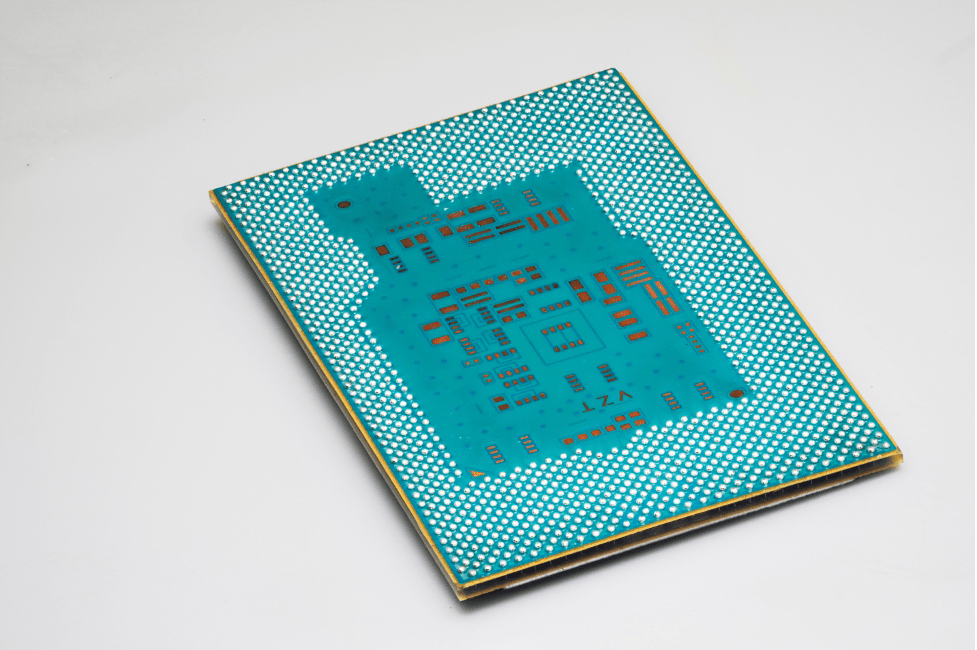

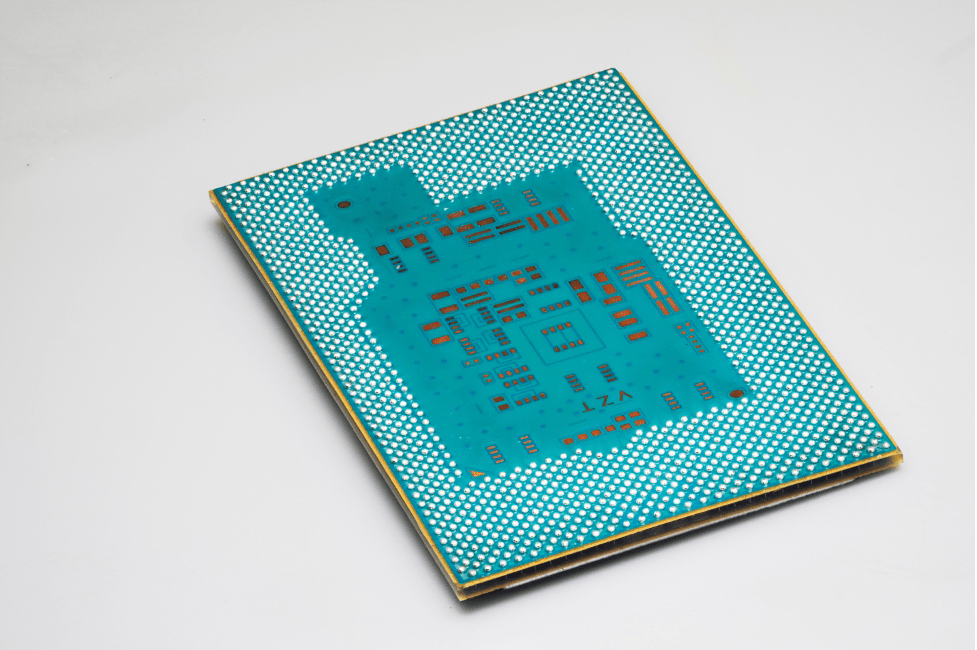

Im Hochleistungsrechnen führen Probleme, die durch Verzug und Spannungsschwankungen aufgrund von Temperaturwechseln entstehen, zu einem umfassenden Wechsel von organischen Substraten zu Glas. Intel hat kürzlich Prototypen von Chips auf Glassubstrat angekündigt, die einen Weg zur weiteren Funktionsskalierung und verbesserten Stromversorgung in Hochleistungssystemen bieten (siehe Abbildung 1).

Abb. 1: BGA-Seite eines zusammengebauten Glassubstrat-Testchips. Quelle: Intel

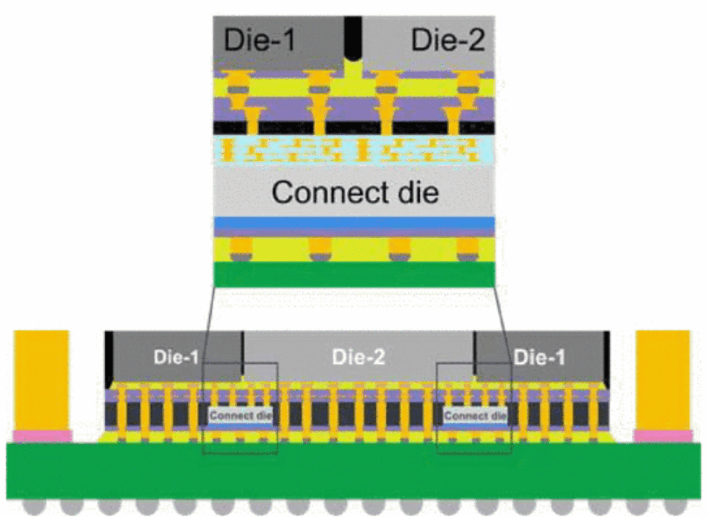

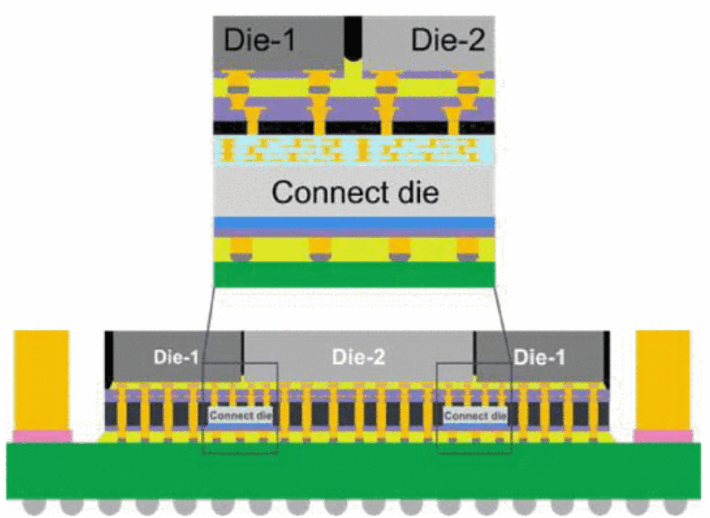

Anstelle starrer Glassubstrate reduzieren Fan-out-Ansätze mit Siliziumbrücken den Bedarf an kostspieligen mehrschichtigen Laminatsubstraten, die in den letzten Jahren knapp waren. Eine Siliziumbrücke kann als die beste Kombination der Side-by-Side-2D-Ansätze mit Fan-out-Chip auf Substrat, FOCoS, angesehen werden (siehe Abbildung 2).

Abb. 2: Bei der Integration einer Siliziumbrücke mit hoher Bandbreite (Leitungen und Zwischenräume von 0.5 µm) hängt die Verformung des Systems von der Chipdicke (450 bis 650 µm), der Formfläche und dem WAK der Epoxidformmasse ab. Quelle: Amkor

Bridge-Methoden bieten weitere Vorteile auf der Leistungsseite. „Bei Brücken-Chip-Verbindungen profitiert der Signalpfad von einem geringen Abstand zwischen den Chips in der Größenordnung von 1 bis 2 Millimetern, sodass sie gut elektrisch kommunizieren können“, sagte Mike Kelly, Vizepräsident für Advanced Packaging and Integration bei Amkor. „Mechanisch und vom Standpunkt der Zuverlässigkeit her handelt es sich um ein komplizierteres System, und wir können gemischte Funktionen wie HF und Logik in einem Paket haben.“

Es wird deutlich, dass Silizium-Interposer-Brücken aus Kostengründen so klein wie möglich sein müssen. Eine Analyse der Amkor-Ingenieure ergab, dass dünnere aktive Chips im FOCoS-Brückenkonstrukt anfälliger für Verformungen sind. Die Arbeit wies auch auf die positiven Effekte der Verwendung von Formmassen mit einem niedrigeren Wärmeausdehnungskoeffizienten (CTE) als Formmasse zweiter Ordnung hin. [1]

Umverteilungsschichten mit breiteren Leitungen und Abständen (bis zu 2 µm L/S) verwalten die zweite Verbindungsgeschwindigkeitsstufe innerhalb dieser Pakete. Insgesamt erfordert der Wärmeableitungspfad aus der Oberseite solch großer Systeme (mehr als das Dreifache der Retikelgröße) eine noch höhere Leitfähigkeit zur Wärmeableitung als bestehende thermische Schnittstellenmaterialien (TIMs). Irgendwann werden wahrscheinlich Metall-TIMs benötigt.

Vereinfacht ausgedrückt, neigen Logikchips, die eng beieinander liegen, dazu, sich zu erwärmen, wie ein großer Logikchip in einem Gehäuse, wenn HBM am Systemrand positioniert ist. Aus diesem Grund fördert ASE seine Brückentechnologie und weist darauf hin, dass der Silizium-Interposer (Kupfer/SiO2) Schichten in der Größenordnung von 1 µm Leitungen und Zwischenräumen, die tendenziell höhere Einfügungsverluste und Übersprechen zwischen Kupferleitungen verursachen als bei FOCoS-Interposern, die breitere Kupfer- und Polyimidabmessungen (3 bis 4 µm) haben. Ein wesentlicher Vorteil neben der hohen Bandbreite und Hochgeschwindigkeitskommunikation in Silizium-Interposern ist die Flexibilität beim Die-Routing für Erdungsleiterbahnen rund um die I/O-Signale, die das Übersprechen reduzieren. [2]

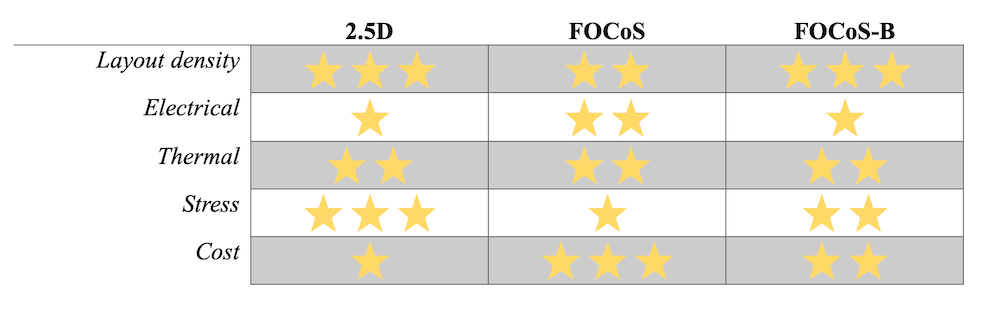

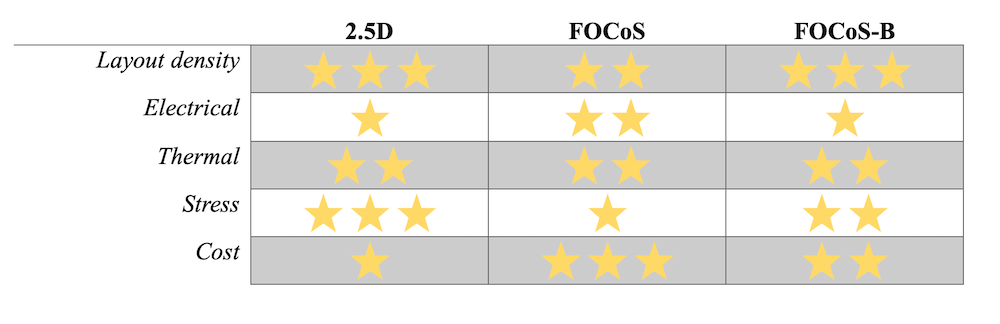

Infolgedessen haben Ingenieure und Gehäusedesigner innerhalb der 2.5D-, FOCoS- und FOCoS-Brückentechnologien die Möglichkeit, Layoutdichte, elektrische/thermische/Belastungsleistung und Kosten abhängig von der spezifischen Anwendung des Moduls abzuwägen (siehe Abbildung 3), wie zusammengefasst von ASE-Ingenieuren. „Es ist zu erwarten, dass die Größe fortschrittlicher Verpackungen immer größer wird und die Verformungs- und Spannungsleistung während des Montageprozesses immer wichtiger wird“, sagten sie.

Abb. 3: Die unterschiedlichen Eigenschaften von 2.5D-, FOCoS- und Bridge-Technologien. Eine Brücke bewältigt Belastungen besser als FOCoS, aber nicht so gut wie 2.5D-Ansätze. Quelle: ASE

Gleichzeitig kommen bald auch gemeinsam verpackte Optiken in Rechenzentren zum Einsatz. Babak Sabi von Intel, Senior Vice President of Assembly Test Technology Development bei Intel, hielt kürzlich bei einer Podiumsdiskussion auf der Semicon West einen Stecker mit optischen Eingängen hoch. „Bei der Verpackung dreht sich alles um Verbindungen, und wir bringen viele Kerne und Speicher zusammen, und die Leute reden über die Integration von Produkten auf Wafer-Ebene“, sagte er. „Hier ist das Glassubstrat äußerst wichtig, da wir auf den Interposer komplett verzichten können.“

Neben einem Fahrplan zur Integration von Glassubstraten für bessere Leistung und großflächige Verzugskontrolle sprach Sabi über die Einführung optischer Verbindungen. „Bis zum Ende dieses Jahrzehnts werden wir optische Signale in vielen verschiedenen Formaten sehen“, sagte er und wies darauf hin, dass Intel und seine Partner an einem „Standard“-Anschluss für optische Schnittstellen zu Chips arbeiten. Er verwendete die Analogie eines Anschlusses, mit dem Verbraucher sehr vertraut sind – USB-C. Für Hyperscale-Netzwerke kann ein optischer Steckverbinder nach Industriestandard die baumelnden Fasern und halbautomatischen Ansätze der heutigen Verbindung mit Silizium-Photonik eliminieren und so eine überlegene Herstellbarkeit und Automatisierung ermöglichen.

Die Notwendigkeit, die Front-End-Waferverarbeitung mit fortschrittlicher Verpackung zu integrieren, treibt auch Veränderungen in der Prozessentwicklung voran. Applied Materials stellte kürzlich seine Roadmap zur gemeinsamen Entwicklung von Hybrid-Bonding- und fortschrittlichen Die-Placement-Tools verschiedener Anbieter mit der neuesten vakuumbasierten Mehrkammerplattform von Applied vor. Die Notwendigkeit, beispielsweise Prozesse wie CMP mit Hybridbonding und fortschrittlichen Platzierungstools zu integrieren, führt zu Partnerschaften zwischen Applied, EV Group und BESI, und dies geschieht auch bei anderen Zulieferern und Forschungs- und Entwicklungszentren auf der ganzen Welt.

Wie dünn können Wafer und Geräte sein?

All diese Entwicklungen erfordern dünnere Siliziumwafer, die wiederum unter anderem schlankere Mobiltelefone, Uhren und implantierbare Geräte ermöglichen.

Das macht es auch schwieriger, mit ihnen zu arbeiten, und sie sind anfälliger für Prozessschwankungen und Fehler. Für die 3D-Integration auf Geräteebene müssen die Wafer jedoch ausgedünnt werden, und sie erfordern neue Arten von Verbindungen, wie zum Beispiel Hybrid-Bonding, eine Technologie, die Sony mit CMOS-Bildsensoren entwickelt hat. Im Allgemeinen werden Wafer von etwa 600 auf 50 µm und darunter verdünnt.

Der Fortschritt von millimetergroßen Geräten hin zu kleineren microLEDs oder microOLEDs, die auf den Rand von Brillen passen, und Einweg-Biotech-Testern erfordert auch neue Sichtweisen auf die Montage. Und während es so aussieht, als ob Silizium-Interposer sicher im Bereich der Fabriken bleiben werden, arbeiten die OSATs, Material- und Ausrüstungslieferanten zusammen, um neue oder wesentlich geänderte Prozesse bereitzustellen.

„In der Biotechnologie ist eine Menge komplexer Chemie im Spiel, weil sie eine Art molekulare Interaktion nutzen – die die Elektronik, die Chemie oder MEMS erkennen und zuordnen wollen – und so zeigt, ob ein Krankheitserreger vorhanden ist oder nicht“, sagte Otte von Promex. „Deshalb haben wir den Montageprozess geändert, um eine Beschädigung dieser Teile zu vermeiden, indem wir beispielsweise einen Aushärtungsprozess bei Raumtemperatur entwickelt haben.“

Otte erklärte, dass Biotech-Geräte, da sie mit dem Patienten interagieren und dann Signale an die Außenwelt senden, keine Standard-Halbleiterprozesse wie 220 °C-Massenaufschmelzen, Einwirkung von UV-Licht oder Ultraschallbewegung in entionisiertem Wasser durchlaufen können. Die Entwicklung nach Spezifikationen in der Biotechnologie oder Medizinelektronik kann zwei oder mehr Jahre dauern, bis die Spezifikationen erfüllt werden, und Module erfordern typischerweise mechanische Strukturen (Mikrofluidik), die keinem Wasser ausgesetzt werden können. Solche neuen Anforderungen werden weiterhin neue Prozesse vorantreiben

Backside Power, Hybrid-Bonding und neue Materialien

Auch andere Änderungen sind im Gange. Grundsätzlich kommt es bei der Verwendung auf Physik, Chemie, Geräteleistung und Kosten an, aber dazu gehören auch viele Optionen, die auf eine bestimmte Anwendung oder einen bestimmten Anwendungsfall zugeschnitten werden können.

Die rückseitige Stromversorgung wird zuerst bei den leistungsstärksten Chips angezeigt. Bei diesem Ansatz erfolgt die Stromversorgung der Transistoren auf der Rückseite des Wafers, was breitere Verbindungen erfordert, während auf der Vorderseite der Geräte nur Signalleitungen geführt werden, wodurch CD für die Anwendung optimiert wird. BPD kann die Zuverlässigkeit verbessern und gleichzeitig den Weg für die Integration einfacher Geräte auf der Rückseite ebnen.

BPD und Hybridbonden sind heute zwei der heißesten Themen im Halbleiterbereich. Jeder umfasst verschiedene Ansätze, und diese Ansätze weisen unterschiedliche Komplexitätsebenen auf. Das Gleiche gilt für Träger aus Siliziumwafern oder Glas, die jeweils Vor- und Nachteile haben. Glas ist beispielsweise sehr flach und wird typischerweise in Trägeranwendungen wiederverwendet.

Ein weiterer relativ neuer Prozess ist das Träger-Debonding, um die Verarbeitung dünner Wafer zu ermöglichen. In einer aktuellen Arbeit enthüllten imec und Brewer Science die Details eines Prozesses zum Lösen von Glasträgern, der für ultradünne Wafer (50 µm bis 20 µm) optimiert wurde. [3] Auf 300-mm-Glaswafern kombinierten die Ingenieure drei Chemikalien, darunter einen Kantenentferner, ein temporäres Verbindungsmaterial und eine Trennschicht, die für die saubere Trennung dünner 300-mm-Siliziumwafer von einem Träger mithilfe eines mechanischen (Klingen-)Lösemechanismus optimiert wurden.

Der Prozess wurde optimiert, um die Kompatibilität mit Wafer-Rückseitenoxiden und der Dual-Damascene-Verarbeitung zu gewährleisten und gleichzeitig einen unbeabsichtigten Wafer-Haftungsverlust oder eine Kontamination zu verhindern und gleichzeitig die Spezifikationen für die Wafer-Dickenvariation (TTV) einzuhalten. Das Ermöglichen der Freigabe dünner Wafer ist nur einer von vielen Prozessen, die wichtig sind, damit Ansätze zur rückseitigen Stromverteilung funktionieren.

Zusammenfassung

As OSATs Wenn Sie Erfahrungen mit der Integration neuer Brückentechnologien sammeln, kann der Ansatz Leistungs- und Kostenvorteile bieten, die zwischen FOCoS- und 2.5D-Integrationsansätzen liegen – und so die Optionen erweitern, die Designern zur Verfügung stehen. Der Einsatz dieser hochdichten Verpackungsansätze ist jedoch immer noch auf Chiphersteller mit eigenem Wafer-to-Package-Integrationsgrad beschränkt.

Unterdessen entwickeln Ingenieure kreative Lösungen für den Zusammenbau biotechnologischer und medizinischer Elektronik.

Unternehmen arbeiten zusammen, um die Welten der Waferfertigung sowie der Montage und Verpackung besser miteinander zu verbinden. Das Kleben und Lösen von Wafern und Glasträgern wird wahrscheinlich eine zunehmende Rolle spielen, da Chiphersteller weiterhin Schichten in dreidimensionalen Geräten kombinieren.

Bibliographie

- H. Jang et al., „Reliability Performance of S-Connect Module (Bridge Technology) for Heterogeneous Integration Packaging“, 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 2023, S. 1027-1031 , doi: 10.1109/ECTC51909.2023.00175.

- C.-C. Wang et al., „Creative Design and Structure Applied to Chiplets Packaging“, 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 2023, S. 1353-1358, doi: 10.1109/ECTC51909.2023.00231.

- K. Kennes et al., „Prozessherausforderungen bei der CVD-Oxidabscheidung auf der Rückseite von 20 μm dünnen 300-mm-Wafern, die vorübergehend mit Glasträgern verbunden sind“, 2023 IEEE 73. Electronic Components and Technology Conference (ECTC), Orlando, FL, USA , 2023, S. 1584-1589, doi: 10.1109/ECTC51909.2023.00269.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiengineering.com/building-better-bridges-in-advanced-packaging/