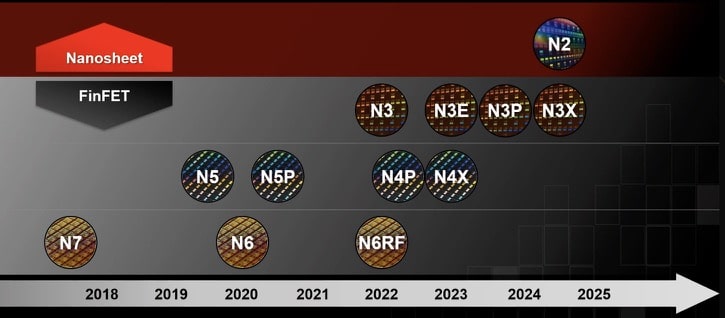

Vào ngày 10 tháng 26, tôi đã xem bài thuyết trình của LC Lu, TSMC Fellow & VP, khi anh ấy nói về việc kích hoạt đổi mới hệ thống với hàng chục slide chỉ trong 2025 phút. TSMC là xưởng đúc chất bán dẫn số một trên thế giới và các sự kiện Nền tảng Đổi mới Mở (OIP) của họ rất phổ biến và được nhiều người tham dự vì công nghệ xử lý và IP được cung cấp khá hấp dẫn đối với nhiều phân khúc thiết kế chất bán dẫn. Lộ trình công nghệ của TSMC cho thấy dòng thời gian của cả kế hoạch FinFET và Nanosheet cho đến năm XNUMX.

Bắt đầu với N3 có một cái gì đó mới được gọi là VâyFlex đã sử dụng Công nghệ thiết kế đồng tối ưu hóa (DTCO), hứa hẹn cải thiện Công suất, Hiệu suất và Diện tích (PPA) cho các phân khúc như tiết kiệm năng lượng và hiệu suất cao. Với cách tiếp cận FinFlex, một nhà thiết kế có thể chọn từ ba cấu hình bóng bán dẫn, dựa trên mục tiêu thiết kế của họ:

- Khối vây 3-2, cho hiệu suất cao

- Vây 2-2, cho hiệu suất hiệu quả

- Vây 2-1, cho công suất thấp nhất, mật độ tốt nhất

Lịch sử của các lựa chọn khối vây được sử dụng trong các nút quy trình N16 đến N3 được hiển thị bên dưới:

Các nhà cung cấp EDA Synopsys, Cadence, Siemens EDA và ANSYS đã cập nhật các công cụ của họ để hỗ trợ FinFlex và trong một SoC duy nhất, bạn thậm chí có thể kết hợp các lựa chọn khối vây. Cùng với việc định thời các đường dẫn quan trọng, bạn có thể sử dụng các ô có vây cao, trong khi các ô đường dẫn không quan trọng có thể là các ô có vây thấp. Như một ví dụ về lợi ích mở rộng quy trình, Lu đã cho thấy CPU ARM Cortex-A72 được triển khai trong N7 với 2 vây, N5 với 2 vây và cuối cùng là N3E với 2-1 vây:

Các ô IP cho N3E đến từ một số nhà cung cấp: TSMC, Synopsys, Silicon Creations, Analog Bits, eMemory, Cadence, Alphawave, GUC, Credo. Có ba trạng thái sẵn sàng của IP: sẵn sàng báo cáo silicon, sẵn sàng cho bộ công cụ thiết kế tiền silicon và đang phát triển.

IP tương tự

Tại TSMC, IP analog của họ đang sử dụng bố cục thông thường có cấu trúc hơn, tạo ra năng suất cao hơn và cho phép các công cụ EDA tự động hóa luồng analog để cải thiện năng suất. TSMC Analog Cell có mật độ poly và oxit đồng nhất, giúp tăng năng suất. Luồng di chuyển tương tự của chúng, định cỡ bóng bán dẫn tự động và Vị trí và Tuyến đường được điều khiển phù hợp cho phép tự động hóa luồng thiết kế bằng các công cụ Cadence và Synopsys.

Các ô tương tự có thể được di chuyển qua các bước: Di chuyển theo sơ đồ, tối ưu hóa mạch, sắp xếp tự động và định tuyến tự động. Ví dụ: việc di chuyển một ô VCO từ N4 sang N3E bằng cách sử dụng quy trình di chuyển tương tự mất 20 ngày, so với cách tiếp cận thủ công cần 50 ngày, nhanh hơn khoảng 2.5 lần.

Vải 3D

TSMC có ba loại bao bì cần xem xét:

Có tám lựa chọn đóng gói trong 3DFabric:

Một ví dụ gần đây sử dụng cách đóng gói SoIC là Bộ xử lý AMD EPYC, CPU trung tâm dữ liệu, cho thấy mật độ kết nối được cải thiện gấp 200 lần so với cách đóng gói 2D, cải thiện mật độ gấp 15 lần so với xếp chồng 3D truyền thống, tạo ra hiệu suất CPU tốt hơn 50-80%.

Độ phức tạp của thiết kế vi mạch 3D được giải quyết thông qua 3Dblox, một phương pháp sử dụng ngôn ngữ chung cho khả năng tương tác của công cụ EDA, bao gồm kiến trúc vật lý và kết nối logic. Bốn nhà cung cấp EDA hàng đầu (Synopsys, Cadence, Siemens, Ansys) đã sẵn sàng các công cụ của họ cho phương pháp tiếp cận 3Dblox bằng cách hoàn thành một loạt năm trường hợp thử nghiệm: CoWoS-S, InFO-3D, SoIC, CoWoS-L 1, CoWoS-L 2 .

TSMC đã tạo ra một liên minh 3DFabric bằng cách cộng tác với các nhà cung cấp trong các lĩnh vực: IP, EDA, Liên minh Trung tâm Thiết kế (DCA), Đám mây, Liên minh Chuỗi Giá trị (VCA), Bộ nhớ, OSAT, Chất nền, Thử nghiệm. Để tích hợp bộ nhớ, TSMC hợp tác với Micron, Samsung Memory và SK hynix, để cho phép tích hợp CoWoS và HBM. Các nhà cung cấp thử nghiệm EDA bao gồm: Cadence, Siemens EDA và Synopsys. Các nhà cung cấp dịch vụ kiểm tra IC bao gồm: Advantest và Teradyne.

Tổng kết

Các công ty thiết kế chất bán dẫn như AMD, AWS và NVIDIA đang sử dụng Liên minh 3DFabric và con số đó sẽ chỉ tăng theo thời gian khi việc thúc đẩy sử dụng bao bì 2D, 2.5D và 3D thu hút nhiều ý tưởng sản phẩm hơn. TSMC có một đội ngũ kỹ sư đẳng cấp thế giới làm việc trên DTCO, với đủ sự cạnh tranh quốc tế để giúp họ liên tục đổi mới cho hoạt động kinh doanh mới. Các phân khúc thị trường cho kỹ thuật số, analog và ô tô sẽ được hưởng lợi từ các lựa chọn lộ trình công nghệ TSMC đã công bố trong FinFlex. Thiết kế chip 3D được hỗ trợ bởi tinh thần đồng đội tập hợp trong Liên minh 3DFabric.

Blog liên quan

Chia sẻ bài đăng này qua:

- Coinsmart. Sàn giao dịch Bitcoin và tiền điện tử tốt nhất Châu Âu.Bấm vào đây

- Platoblockchain. Web3 Metaverse Intelligence. Khuếch đại kiến thức. Truy cập Tại đây.

- nguồn: https://semiwiki.com/semiconductor-manufacturers/tsmc/320968-tsmc-oip-enabling-system-innovation/