Det diskuteras mycket om att undanröja hinder för innovation nuförtiden. Halvledarsystem är kärnan i att låsa upp många former av teknisk innovation, om vi bara kunde ta itu med frågor som att bromsa Moores lag, minska strömförbrukningen, förbättra säkerhet och tillförlitlighet och så vidare. Men det finns en annan ganska betydande barriär som är ämnet för detta inlägg. Det är den dramatiska skillnaden mellan processor- och minnesprestanda. Medan system med CPU:er och GPU:er levererar otroliga prestandanivåer, släpar minnena som hanterar kritisk data för dessa system avsevärt. Detta är minnesväggsproblemet, och jag skulle vilja undersöka hur Arteris släpper lös innovation genom att bryta ner minnesvägg.

Vad är Memory Wall?

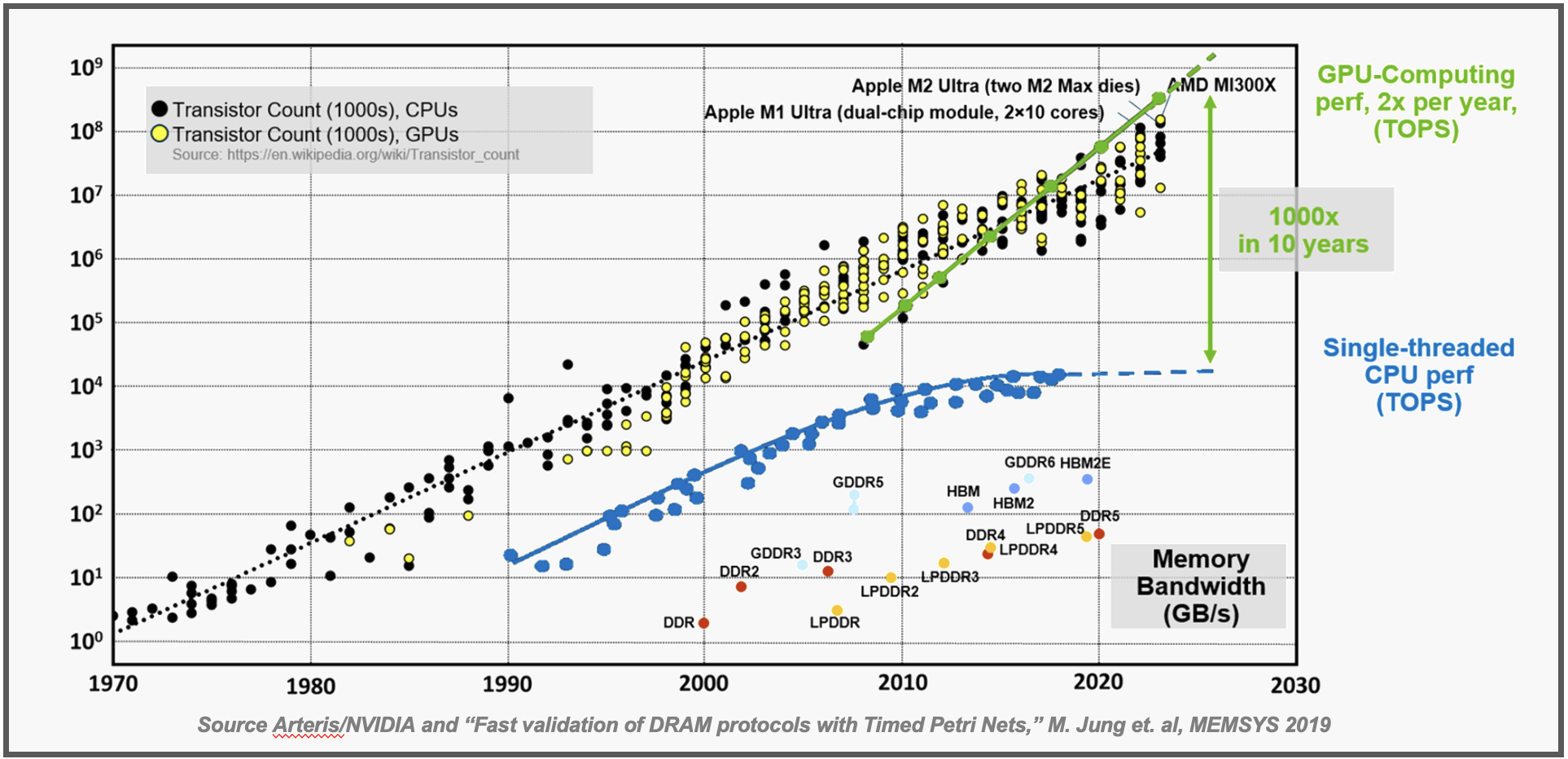

Grafiken överst i det här inlägget illustrerar minnesväggsproblemet. Du kan se den stadiga ökningen av prestanda för entrådade CPU: er avbildad av den blå linjen. Den gröna linjen visar den exponentiella ökningen av prestanda som läggs till av kluster av GPU:er. Prestandaökningen för GPU:er jämfört med processorer beräknas vara 100X på 10 år – en häpnadsväckande statistik. Som en sidoanteckning kan du se att transistorn räknas för både CPU: er och GPU:er kluster runt en liknande rak linje. GPU-prestanda levereras genom att göra färre uppgifter mycket snabbare i motsats till att kasta fler transistorer på problemet.

Många system idag är en kombination av ett antal CPU:er som utför breda hanteringsuppgifter med ett stort antal GPU:er som gör specifika uppgifter, ofta relaterade till AI. Kombinationen ger den fantastiska genomströmning vi ser i många produkter. Det finns en mörk sida av denna harmoniska arkitektur som avbildas längst ner i diagrammet. Här ser vi prestandadata för de olika minnesteknologierna som levererar all information för dessa system att bearbeta. Som du kan se är den levererade prestandan avsevärt lägre än de CPU:er och GPU:er som är beroende av dessa minnessystem.

Detta är problemet med minnesväggen. Låt oss utforska det unika sättet som Arteris löser detta problem.

The Arteris Approach – En mycket konfigurerbar Cache Coherent NoC

Ett väl accepterat tillvägagångssätt för att hantera långsammare minnesåtkomsthastighet är att förhämta nödvändig data och lagra den i en lokal cache. Att komma åt data på detta sätt är mycket snabbare – några CPU-cykler jämfört med över 100 CPU-cykler. Det är ett bra tillvägagångssätt, men det kan vara skrämmande att implementera all mjukvara och hårdvara som krävs för att komma åt minnet från cachen och säkerställa att rätt data finns på rätt plats vid rätt tidpunkt och konsekvent över alla cacher. System som effektivt levererar denna lösning kallas cache sammanhängande, och att uppnå detta mål är inte lätt. En koherensimplementering endast för programvara kan till exempel konsumera så mycket som ~25 % av alla CPU-cykler i systemet och är mycket svår att felsöka. SoC-designers väljer ofta cachekoherenta NoC-hårdvarulösningar istället, som är transparenta för programvaran som körs på systemet.

Nyligen fick jag tillfälle att prata med Andy Nightingale, vice VD för produktledning och marknadsföring på Arteris. Andy gjorde ett bra jobb med att förklara utmaningarna med att implementera cachekoherenta system och den unika lösning Arteris har utvecklat för att klara dessa utmaningar.

Det visar sig att utvecklingen av en pålitlig och energieffektiv cache-koherent arkitektur berör många hård- och mjukvaruaspekter av systemdesign. Det kan vara ganska svårt att få allt att fungera pålitligt, effektivt och nå de nödvändiga PPA-målen. Andy uppskattade att allt detta arbete kunde kräva 50 ingenjörsår per projekt. Det är mycket tid och kostnader.

Den goda nyheten är att Arteris har betydande kompetens inom detta område och företaget har skapat en komplett cache-koherent arkitektur i en av sina nätverk-på-chip-produkter (NoC). Andy beskrev Ncore, en komplett cachekoherent NoC som erbjuds av Arteris. Hantering av minnesåtkomst passar bra i den övergripande nätverk-på-chip-arkitekturen som Arteris är känd för. Ncore hanterar den cachekoherenta delen av SoC transparent för mjukvara – vilket gör att systemdesignern kan fokusera på utmaningarna på högre nivå som är förknippade med att få processorn och alla dessa GPU:er att utföra uppgiften.

Andy körde ner en lista över Ncore-funktioner som var betydande:

- Produktiv: Anslut flera bearbetningselement, inklusive Arm och RISC-V, för maximal teknisk produktivitet och acceleration från tid till marknaden, vilket sparar 50+ årsverk per projekt.

- Konfigurerbar: Skalbar från heterogena till mesh-topologier, stöder CHI-E, CHI-B och ACE koherenta, såväl som ACE-Lite IO koherenta gränssnitt. Ncore gör det också möjligt för AXI icke-koherenta agenter att fungera som IO-koherenta agenter.

- Ekosystemintegration: Förvaliderad med de senaste Arm v9 fordonskärnorna, vilket levererar på ett tidigare tillkännagivet partnerskap med Arm.

- Säker: Stödjer ASIL B till ASIL D-kraven för fordonssäkerhetstillämpningar och är ISO26262-certifierad.

- Effektiv: Mindre formyta, lägre effekt och högre prestanda genom design, jämfört med andra kommersiella alternativ.

- Marknader: Lämplig för SoC-lösningar för fordon, industri, företagsdatorer, konsumenter och IoT.

Andy beskrev några av fördelarna som uppnåtts med en SoC-design för konsumenter. Dessa inkluderade strömlinjeformad golvplanering tack vare den mycket distribuerade arkitekturen, vilket främjar ett effektivt resursutnyttjande. Arteris högpresterande sammankoppling med ett tyg med hög bandbredd och låg latens säkerställde sömlös dataöverföring och höjde systemets övergripande prestanda.

Genom att gräva lite djupare ger Ncore också insyn i realtid i sammankopplingsstrukturen med spårning på transaktionsnivå, prestandaövervakning och feldetektering och korrigering. Alla dessa funktioner underlättar enkel felsökning och överlägsen produktkvalitet. Det omfattande ekosystemstödet och kompatibiliteten med industristandardgränssnitt som AMBA, underlättar också enklare integration med tredjepartskomponenter och EDA-verktyg.

Detta var en mycket användbar diskussion. Det verkar som att Arteris dramatiskt har minskat omkostnaderna för implementering av cachekoherenta arkitekturer.

Att lära sig mer

Jag nämnde några detaljer om arbetet som Arteris gör med Arm. Tro inte att det är den enda partnern företaget arbetar med. Arteris har kallats för systemets IPs Schweiz. Företaget har också ett betydande arbete med RISC-V-communityt som detaljerat i SemiWiki-inlägget här.

Arteris tillkännagav nyligen expansion av sin Ncore-produkt. Du kan läsa hur Arteris utökar Ncore cache coherent interconnect IP för att accelerera ledande elektronikdesigner här. I releasen presenterar Leonid Smolyansky, Ph.D. SVP SoC Architecture, Security & Safety på Mobileye erbjöd dessa kommentarer:

"Vi har arbetat med Arteris nätverk-på-chip-teknik sedan 2010 och använder den i vår avancerade autonoma körning och förarassistansteknologier. Vi är glada över att Arteris har tagit med sin betydande ingenjörsförmåga för att hjälpa till att lösa problemen med feltolerans och pålitlig SoC-design.”

Det finns också en kort (lite över en minut) video som förklarar de utmaningar som Ncore tar itu med. Jag tyckte att videon var ganska informativ.

Om du behöver förbättrad prestanda för din nästa design bör du definitivt ta en närmare titt på de cachekoherenta lösningarna som erbjuds av Arteris. Du kan läs mer om Ncore här. Och det är så Arteris släpper lös innovation genom att bryta ner minnesväggen.

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoData.Network Vertical Generative Ai. Styrka dig själv. Tillgång här.

- PlatoAiStream. Web3 Intelligence. Kunskap förstärkt. Tillgång här.

- Platoesg. Kol, CleanTech, Energi, Miljö, Sol, Avfallshantering. Tillgång här.

- PlatoHealth. Biotech och kliniska prövningar Intelligence. Tillgång här.

- Källa: https://semiwiki.com/ip/arteris/342991-arteris-is-unleashing-innovation-by-breaking-down-the-memory-wall/