Notícias de hackers invadindo sistemas estão se tornando comuns atualmente. Embora muitas das violações relatadas até o momento possam ter ocorrido devido a falhas de segurança no software, também existem vulnerabilidades no hardware. Como resultado, o tópico de segurança está recebendo maior atenção dentro da indústria de semicondutores em relação ao sistema em chip (SoC) e interfaces de dados de alta velocidade. O objetivo é garantir que os dados que se movem por essas interfaces sejam protegidos contra acesso ou manipulação por agentes não autorizados.

Um tipo de interface que está proliferando rapidamente está relacionado às memórias. As interfaces de alta largura de banda, como DDR, continuam aumentando as velocidades de transferência a cada nova geração. É imperativo proteger as interfaces de memória dinâmica de acesso aleatório (DRAM) fora do chip, que são vulneráveis a certos tipos de ataques. Com sistemas cada vez mais complexos, proteger os dados deve ser parte integrante do projeto de hardware.

Vulnerabilidades específicas de DRAM

Vulnerabilidades específicas de DRAM incluem Row hammer, RAMBleed e ataques de inicialização a frio. Os ataques Row Hammer são executados pela leitura repetida de dados em uma linha de memória em alta velocidade. Essa atividade faz com que os bits nas linhas adjacentes sejam invertidos, permitindo que o invasor obtenha acesso de leitura e gravação a toda a memória física. O RAMBleed usa os mesmos princípios do Row Hammer, mas lê as informações em vez de modificá-las para extrair informações da DRAM, ameaçando assim a confidencialidade dos dados armazenados na memória. Com ataques de inicialização a frio, os invasores podem redefinir um sistema, acessar dados de memória física pré-inicialização para recuperar chaves de criptografia e causar danos. As consequências desses ataques podem ser graves, incluindo roubo de identidade, fraude, perdas financeiras e despesas de responsabilidade para limpar os danos. Os ataques podem comprometer o sistema geral e seus dados, resultando também em danos significativos à reputação.

Protegendo contra as vulnerabilidades acima

A criptografia evita ataques de martelo de linha, tornando mais difícil para um invasor obter acesso a locais de memória física. Os dados criptografados são mais difíceis de manipular, pois não estão em sua forma original, o que torna mais difícil para o invasor criar um ataque de martelo de linha. Além disso, a autenticação pode ser usada para proteger a integridade dos dados, o que torna mais difícil para um invasor alterar o conteúdo dos locais da memória. A autenticação também pode ser usada para garantir acesso controlado a locais de memória específicos, o que pode ajudar na prevenção de acesso não autorizado.

Para proteger as interfaces de memória por design, os projetistas podem recorrer a soluções de criptografia de memória de alto desempenho e baixa latência, como a criptografia baseada em AES-XTS que pode ser aumentada com algoritmos de hashing criptográfico, para tratar da confidencialidade e integridade dos dados. A criptografia cobre todos os bits, tornando quase impossível criar padrões de martelo Row. Atualizar chaves e criptografia de memória também pode proteger contra RAMBleed e ataques de inicialização a frio.

Desafios

A implementação da criptografia de memória tem um custo, incluindo sobrecarga que afeta energia, desempenho, área (PPA) e latência. Os projetistas devem considerar as compensações e garantir que a segurança seja integrada ao projeto desde o início. É fundamental que as chaves sejam geradas e gerenciadas em uma área confiável/segura do SoC e distribuídas por meio de canais dedicados ao módulo de criptografia. A configuração de controle e a proteção contra leitura de chaves também devem fazer parte da arquitetura geral de segurança.

Estratégia de solução ideal

As interfaces DDR e LPDDR se beneficiariam da segurança de criptografia de memória em linha (IME), assim como as interfaces PCI Express® (PCIe®) e Compute Express Link (CXL) se beneficiariam da integridade e criptografia de dados (IDE). A solução IME deve acoplar firmemente a criptografia/descriptografia dentro do controlador DDR ou LPDDR, permitindo a máxima eficiência da memória e a menor latência geral. A solução também deve permitir a adaptação contínua de uma ameaça de segurança em constante evolução.

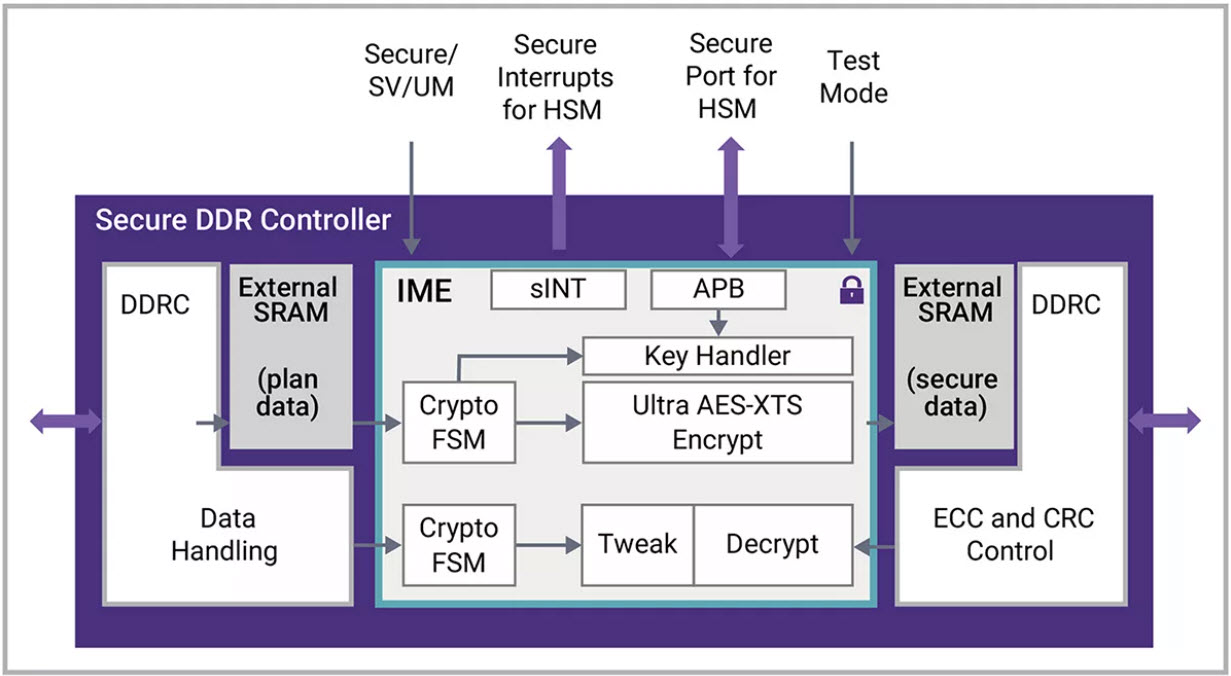

Figura: Controlador DDR5 seguro com criptografia de memória em linha (IME)

Módulo de segurança IME para DDR/LPDDR

O Synopsys IME Security Module fornece confidencialidade de dados para memória fora do chip em interfaces DDR/LPDDR, suportando canais de gravação e leitura com criptografia AES-XTS. Ele se integra perfeitamente aos controladores Synopsys DDR/LPDDR, reduzindo o risco e acelerando a integração do SoC com latência ultrabaixa de apenas dois ciclos. O módulo é escalável, pronto para certificação FIPS 140-3 e oferece suporte a diferentes larguras de caminho de dados, tamanhos de chave e modos de criptografia. Ele também oferece controle de chave eficiente, zeroização de SRAM e desvio do modo de missão. Com sua solução autônoma ou integrada, o IME Security Module fornece PPA e latência ideais para projetos de SoC seguros e compatíveis.

Para mais detalhes, consulte Página Synopsys IME Security Module.

Resumo

Incorporar segurança aos SoCs é um requisito fundamental para atender aos requisitos de privacidade e proteção de dados dos usuários de sistemas eletrônicos. Proteger as interfaces de alta velocidade é fundamental para atender a esse requisito. Os mecanismos implantados precisam ser altamente eficientes com latência ideal. Autenticação e gerenciamento de chaves no plano de controle e integridade e criptografia de dados no plano de dados são componentes essenciais de uma solução de segurança completa. A Synopsys fornece soluções completas para proteger SoCs, seus dados e comunicações.

Leia também:

Análise de rede de fornecimento de energia no design de DRAM

Intel Keynote em Formal um Mind-Stretcher

Sistemas Multi-Die Chave para a Próxima Onda de Inovações de Sistemas

Compartilhe esta postagem via:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- Platoblockchain. Inteligência Metaverso Web3. Conhecimento Ampliado. Acesse aqui.

- Fonte: https://semiwiki.com/eda/synopsys/326542-securing-memory-interfaces/