Minha carreira de design de IC começou com o design de DRAM em 1978, então fiquei de olho nos desenvolvimentos nessa área de design de memória para observar os desafios de design, atualizações de processo e inovações ao longo do caminho. A Synopsys hospedou um simpósio de tecnologia de memória em novembro de 2022, e tive a oportunidade de assistir a uma apresentação dos engenheiros da SK hynix, Tae-Jun Lee e Bong-Gil Kang. Os chips DRAM atingiram alta capacidade e taxas de dados rápidas de 9.6 gigabits por segundo, como o recente LPDDDR5T anúncio em 25 de janeiro. As taxas de dados podem ser limitadas pela integridade da rede de fornecimento de energia (PDN), mas analisar uma DRAM de chip completo com PDN reduzirá demais os tempos de simulação.

A largura de banda de memória de pico por canais x64 mostrou um crescimento constante em várias gerações:

- DDR1, 3.2 GB/s com alimentação de 2.5 V

- DDR2, 6.4 GB/s com alimentação de 1.8 V

- DDR3, 12.8 GB/s com alimentação de 1.5 V

- DDR4, 25.6 GB/s com alimentação de 1.2 V

- DDR5, 51.2 GB/s com alimentação de 1.1 V

Um grande desafio para atingir essas metas de temporização agressivas é controlar os problemas parasitas de queda de IR causados durante o layout de IC da matriz DRAM, e mostrado abaixo é um gráfico de queda de IR onde a cor vermelha é uma área de maior queda de tensão, que por sua vez retarda o desempenho da memória.

Os parasitas extraídos para um IC são salvos em um formato de arquivo SPF, e adicionar esses parasitas para o PDN a uma netlist SPICE faz com que o simulador de circuito desacelere por um fator de 64X, enquanto o número de elementos RC parasitas adicionados pelo PDN é 3.7 vezes mais do que apenas parasitas de sinal.

Na SK hynix, eles criaram uma abordagem pragmática para reduzir os tempos de execução da simulação ao usar o PrimeSim™ Pro simulador de circuito em netlists SPF incluindo o PDN usando três técnicas:

- Particionamento da netlist entre Power e outros Signals

- Redução de elementos RC no PDN

- Controlando a tolerância de eventos de simulação

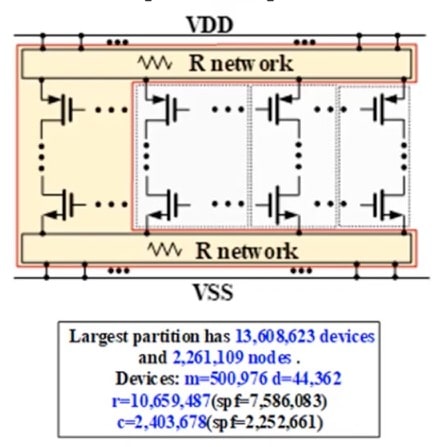

O PrimeSim Pro usa o particionamento para dividir a netlist com base na conectividade e, por padrão, o PDN e outros sinais se combinam para formar partições muito grandes, o que, por sua vez, diminui muito os tempos de simulação. Aqui está a aparência da maior partição com as configurações padrão do simulador:

Uma opção no PrimeSim Pro (primesim_pwrblock) foi usado para reduzir o tamanho da maior partição, separando o PDN de outros sinais.

O PDN extraído no formato SPF tinha muitos elementos RC, o que reduzia os tempos de execução da simulação do circuito, então uma opção chamada primesim_postl_rcred foi usado para reduzir a rede RC, preservando ao mesmo tempo a precisão. A opção de redução de RC foi capaz de diminuir o número de elementos RC em até 73.9%.

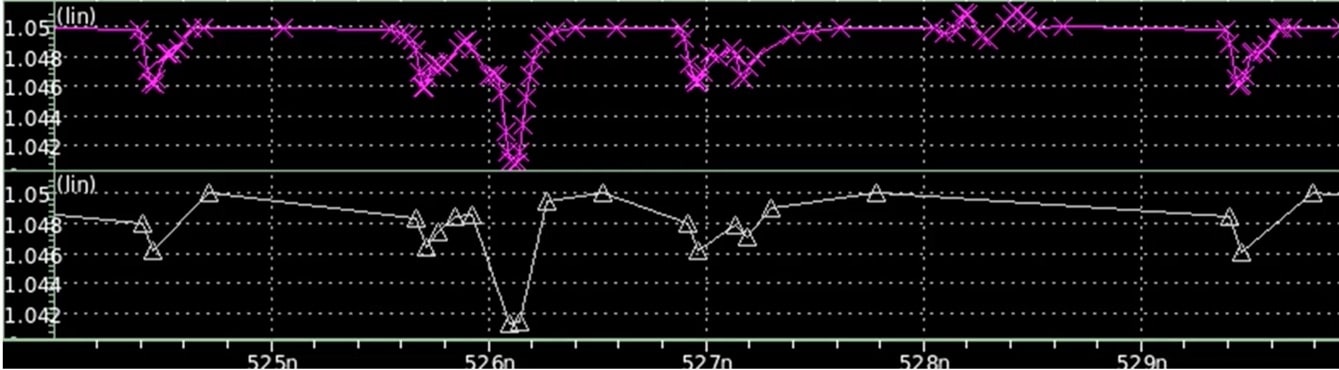

Os simuladores de circuito como o PrimSim Pro usam matemática de matriz para resolver a corrente e as tensões nas partições netlist, portanto, o tempo de execução está diretamente relacionado ao tamanho da matriz e com que frequência uma mudança de tensão requer recálculo. A opção de simulador primesim_evtgrid_for_pdn foi usado e reduz o número de vezes que uma matriz precisa ser resolvida sempre que houver pequenas variações de tensão no PDN. O gráfico abaixo mostrado em roxo tem um X em cada ponto no tempo em que a resolução de matrizes no PDN foi necessária por padrão, então mostrados em branco são triângulos em cada ponto no tempo em que a resolução de matrizes é usada com a opção de simulador. Os triângulos brancos acontecem com muito menos frequência do que os X roxos, permitindo velocidades de simulação mais rápidas.

Uma opção final do simulador FineSim Pro usada para reduzir tempos de execução foi primesim_pdn_event_control=a:b, e funciona aplicando uma fonte de energia ideal para a:b, resultando em menos cálculo de matriz para o PDN.

As melhorias no tempo de execução da simulação usando todas as opções do FineSim Pro combinadas foram um aumento de velocidade de 5.2 vezes.

Resumo

Os engenheiros da SK hynix têm usado os simuladores de circuito FineSim e PrimeSim para análise em seus projetos de chip de memória. O uso de quatro opções no PrimeSim Pro forneceu melhorias de velocidade suficientes para permitir a análise PDN de chip completo com parasitas SPF incluídos. Espero que a Synopsys continue inovando e melhorando sua família de simuladores de circuitos para enfrentar os crescentes desafios do chip de memória e outros estilos de design de IC.

Blogs relacionados

Compartilhe esta postagem via:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- Platoblockchain. Inteligência Metaverso Web3. Conhecimento Ampliado. Acesse aqui.

- Fonte: https://semiwiki.com/eda/324168-power-delivery-network-analysis-in-dram-design/