In het verleden probeerden analisten, consultants en vele andere experts de kosten te schatten van een nieuwe chip, geïmplementeerd in de nieuwste procestechnologie. Ze kwamen tot de conclusie dat met het 3nm-knooppunt slechts een paar bedrijven zich deze zouden kunnen veroorloven – en tegen de tijd dat ze in het Angstrom-bereik zouden komen, zou waarschijnlijk niemand dat meer kunnen doen.

Er is de afgelopen paar procesknooppunten veel veranderd. Steeds meer startups bouwen met succes chips met geavanceerde knooppunten voor veel minder geld dan de hoog geciteerde cijfers. Achter de cijfers schuilen enkele brede veranderingen in het chipontwerp en de productie. Onder hen:

- Veel chips met geavanceerde knooppunten zijn ofwel sterk gerepliceerde arrays van meervoudig geaccumuleerde verwerkingselementen die worden gebruikt voor AI/ML. Deze zijn relatief eenvoudig vergeleken met het integreren van verschillende componenten op een enkele chip, waar ze moeten worden gekarakteriseerd op thermische problemen, geluid en verschillende gebruiksscenario's en toepassingen.

- Geavanceerde verpakkingen, die mainstream zijn geworden sinds die vroege schattingen werden gemaakt, stellen chipmakers in staat chips te bundelen of te bundelen chips ontwikkeld op verschillende procesknooppunten, in plaats van te proberen analoge functies naar 5 nm en verder te pushen, wat zowel duur als niet voordelig is.

- In het verleden zorgde de overstap naar het nieuwste knooppunt voor marktleiderschap op het gebied van prestaties en kracht. Dat is niet langer het geval. Verbeteringen op volwassen knooppunten en architectonische veranderingen waarbij hardware en software betrokken zijn, zorgen ervoor dat veel chipmakers de migratie naar de nieuwste knooppunten kunnen uitstellen totdat die processen volwassen genoeg zijn om kosteneffectief te zijn.

Een van de grote problemen met de vroege schattingen is dat het extrapolaties waren van de beste gegevens die destijds beschikbaar waren. De belangrijkste bron was de International Technology Roadmap for Semiconductors, die in 2016 werd uitgefaseerd. In de daaropvolgende jaren zijn de fundamenten van chipontwerp en -productie dramatisch veranderd.

Velen gingen er bijvoorbeeld van uit dat alle nieuwe chips een dradenkruis zouden vullen en dat de omvang en complexiteit van ontwerpen zouden blijven groeien. In sommige gevallen is de complexiteit toegenomen – tot ver voorbij het punt waarop alle nieuwste features op één dradenkruis passen – maar veel van die nieuwe features zijn ontwikkeld met behulp van een mix van de nieuwste procesgeometrieën en gevestigde procesknooppunten. In andere gevallen nam het aantal verwerkingselementen in een pakket toe, maar nam de complexiteit juist af.

Software is een ander bepalend element. Niet alle software hoeft vanaf nul te worden ontwikkeld. Bovendien is er een overvloedig aanbod van reeds bestaande tools en ecosystemen voor Arm-, NVIDIA- en in toenemende mate RISC-V-ontwerpen. En bijna alle grote EDA-bedrijven investeren zwaar in AI/ML om het ontwerpproces zowel te verkorten als te verbeteren, vooral als het gaat om het debuggen van software en het effectiever inzetten van expertise binnen een bedrijf door middel van versterkend leren.

De getallen

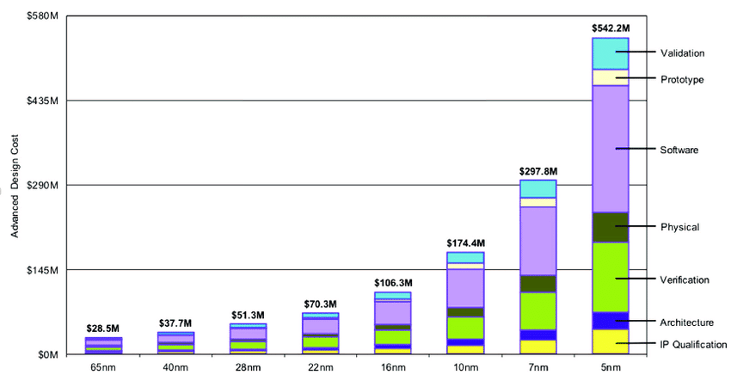

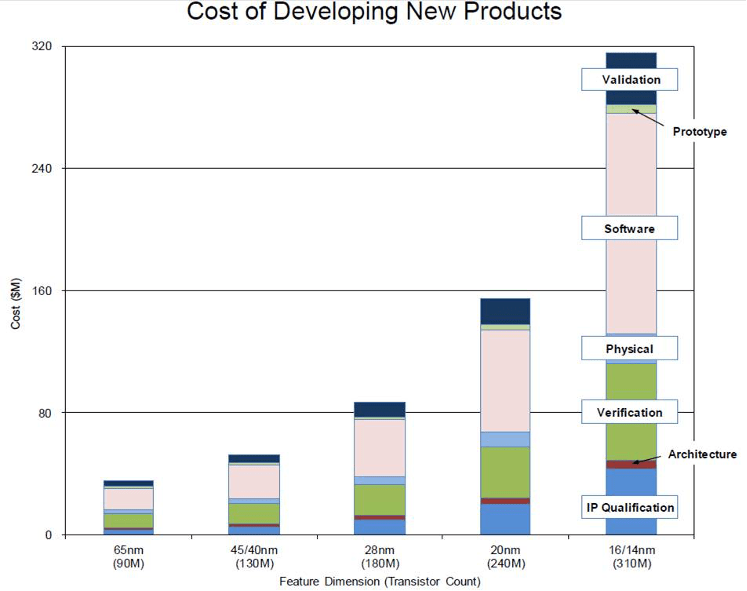

In 2018, de laatste keer dat iemand een dergelijke schatting maakte, publiceerde IBS de grafiek in figuur 1. Dit bracht de kosten van een 5nm-chip op 542.2 miljoen dollar. Als dat waar zou zijn, zouden er vandaag de dag duidelijk maar twee of drie chips geproduceerd worden, en waarschijnlijk zou niemand verder kijken dan 3nm.

Fig. 1: Kosten voor de productie van een nieuwe chip. Bron: IBS 2018

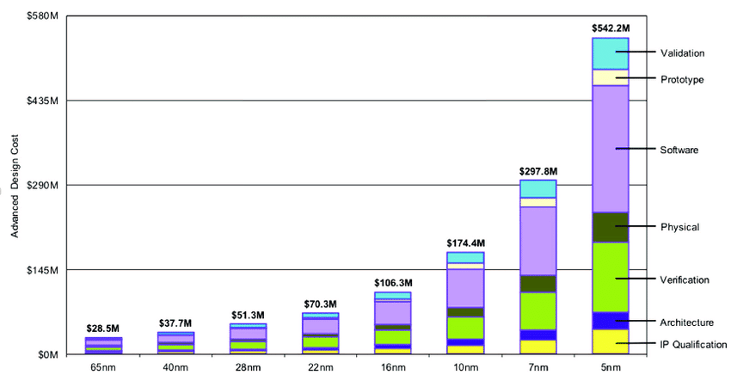

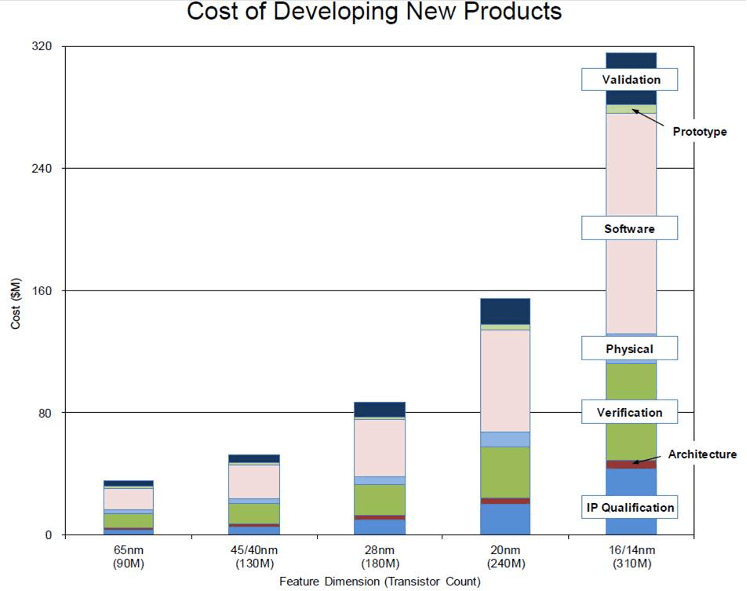

Als we een paar jaar teruggaan en dit vergelijken met de grafiek die IBS in 2014 produceerde (zie figuur 2), kunnen we zien hoe die schattingen in de loop van de tijd veranderen.

Fig. 2: Kosten voor de productie van een nieuwe chip. Bron: IBS 2014

Merk op dat de geschatte kosten van 16nm/14nm van ongeveer $310 miljoen naar $106 miljoen zijn gegaan. En verder terug in de tijd ging 28nm van ongeveer $85 miljoen naar $51 miljoen. Of dit een overschrijding van de geschatte kosten is, of dat dit een zeer scherpe daling van de kosten weerspiegelt zodra een nieuw knooppunt volwassener is geworden, is een kwestie van discussie. Maar als de laatste cijfers met een vergelijkbaar bedrag worden verdisconteerd, zou dat de kosten van een 5nm-chip ergens in de buurt van $280 miljoen brengen, terwijl een 7nm-chip ongeveer $160 miljoen zou bedragen.

“Denk aan Qualcomm of NVIDIA”, zegt Isadore Katz, senior directeur marketing en bedrijfsontwikkeling bij Siemens Digital Industries-software. “Als het werkelijk 542 miljoen dollar zou kosten om een nieuwe chip te bouwen, zouden zij en nog een paar anderen de enigen kunnen zijn die het zich daadwerkelijk kunnen veroorloven om het te gaan doen. Maar ze gaan geen chip bouwen op 5nm. Ze gaan één architectuur nemen, enkele innovaties in die architectuur aanbrengen als onderdeel van de overgang naar het nieuwe procesknooppunt, en dan gaan ze een familie van onderdelen ontwikkelen die op dat procesknooppunt werken.

Er zijn maar weinig bedrijven die hun werkelijke kosten publiceren, maar je kunt kijken naar de durfkapitaalfinanciering die bedrijven hebben ontvangen en de ruwe kosten vinden door te kijken naar hoeveel geld ze hadden verspild toen hun eerste chip werd uitgebracht. “Innovium werd gebouwd met $150 miljoen voor hun initiële chip, en daarna ontvingen ze nog een ronde van $100 miljoen, waarmee meerdere generaties werden gefinancierd”, zegt Nick Ilyadis, senior director productplanning voor Achronix. “Sinds de oprichting in 2014 ontving Innovium in totaal 402 miljoen dollar aan financiering over 10 rondes, en had het nog steeds 145 miljoen dollar in kas toen het in 2021 aan Marvell werd verkocht voor 1 miljard dollar. Hun derde generatie chips werd vervaardigd met behulp van een 7nm-proces.”

Een aanzienlijk deel van de kosten bestaat uit een boete voor de first mover. “De kosten die gepaard gaan met grote digitale chips zijn geëxplodeerd”, zegt Marc Swinnen, directeur productmarketing bij Ansys. “Dat is waar die grote krantenkoppen vandaan komen. Als je kijkt naar wat Apple nodig heeft om een nieuwe chip te maken, dan zijn dat 18 maanden, honderden ontwerpers, licenties, een geheel nieuwe maskerset, geavanceerde processen. Dat is het moment waarop de kosten oplopen. Maar als je een oudere node kunt gebruiken, zijn die kosten nu veel lager.”

Er kunnen ook verschillende kosten in deze cijfers verborgen zijn. “Er zijn enorme investeringen nodig om de nieuwe transistorfunctionaliteit opnieuw te karakteriseren, om de capaciteiten voor het maken van maskers op hun plaats te krijgen, om de productieproblemen te begrijpen, om de extractiemodellen te creëren”, zegt Katz van Siemens. “Maar we profiteren van de lessen die zijn geleerd op eerdere knooppunten en zodra we die bouwstenen klaar hebben, het BSIM-CMG-model, het extractiemodel, de chipvariaties en metallisatie, kunnen we profiteren van de geparametriseerde, of procesonafhankelijke technologie die we op de bovenste lagen hebben.”

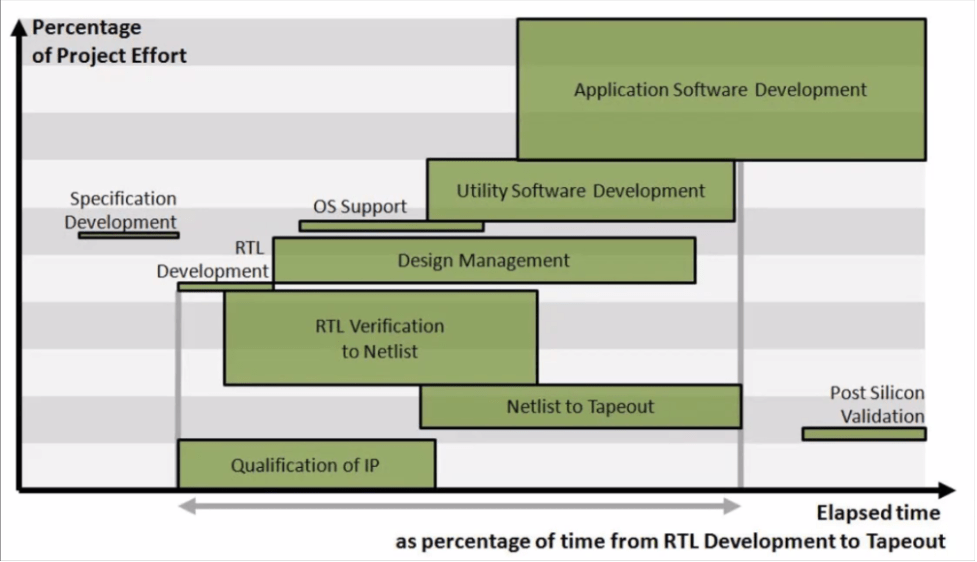

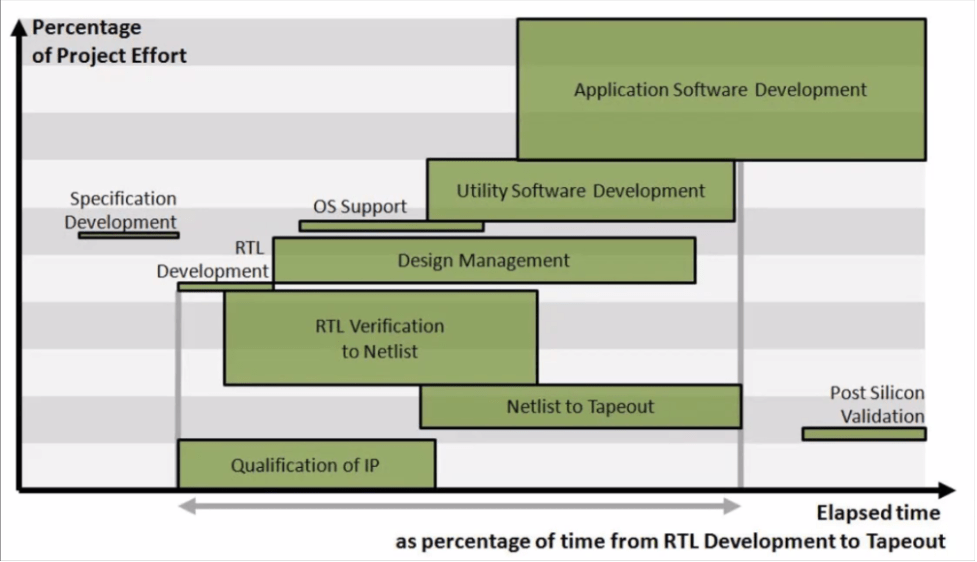

De cijfers hebben anderen nieuwsgierig gemaakt. “Dit is een diagram (zie figuur 3) dat ik twaalf jaar geleden heb gemaakt”, zegt Frank Schirrmeister, vice-president oplossingen en bedrijfsontwikkeling bij slagader. “Ik had vier of vijf sets gegevens ontvangen van IBS, maar kon de cijfers niet publiceren, dus in de grafiek die ik maakte, werden de uitgavencategorieën gemiddeld. Dit toont de belangrijkste stappen in de chipontwikkeling. Het toont een tijdlijn van RTL-ontwikkeling tot tape-out langs de x-as. En dan staat het percentage van de totale projectinspanning op de y-as.”

Fig. 3: Tijd en moeite om een chip te maken. Bron: Frank Schirrmeister

Op basis van figuur 3 kunt u vervolgens overwegen of deze in de loop van de tijd veranderen, of schalen met de grootte of het productieknooppunt. Er wordt bijvoorbeeld vaak beweerd dat de kosten van verificatie kwadratisch stijgen met de omvang, ook al is historisch gebleken dat dit niet waar is. “Verificatiekosten stijgen omdat hoe groter het ontwerp is, hoe meer tijd het kost om te simuleren en hoe meer testgevallen je moet genereren”, zegt Ilyadis. “Er zijn basistests die je kunt gebruiken van vorige generaties, en die blijf je uitvoeren. Dan zijn er de nieuwe tests die verband houden met de extra functionaliteit die wordt toegevoegd. Dat vereist meer servers, grotere servers, meer schijven. Het rimpelt door de infrastructuur als extra kosten.”

Is infrastructuur inbegrepen in de gepubliceerde kosten? "De duivel zit in de details van het begrijpen van wat er in die cijfers zit", zegt Schirrmeister van Arteris. “Zit daar alle software in? Hoeveel nieuwe RTL-ontwikkeling zit daar in? Hoeveel verificatie? Moet u een emulator kopen? Als je kijkt naar de kosten voor maskers, komt dat op zijn minst in de orde van grootte van deze chips.”

Sommige kosten dalen in de loop van de tijd. "Als je de kosten van IP in ogenschouw neemt, moet je het ofwel ontwikkelen, waarbij gebruik wordt gemaakt van interne technische middelen, ofwel in licentie geven, wat betekent dat je de leverancier betaalt", zegt Ilyadis. “Normaal gesproken worden licenties geleverd met ondersteuning en onderhoud – dat zijn de gelduitgaven. Dan zijn er nog de gereedschapskosten. Elke generatie vereist een nieuwe set tools, omdat de routing complexer wordt of er extra zaken zijn waarmee rekening moet worden gehouden. Er is het personeelsbestand van het team dat de chip ontwikkelt. Bovendien moet je testopstellingen bouwen, of zelfs een product dat je chip demonstreert. Nu gaan we buiten de chip zelf, maar het zijn allemaal zaken die verband houden met de daadwerkelijke chipontwikkeling en wat je nodig hebt om deze op de markt te brengen. Dan is er nog dat geschenk dat blijft geven: software. De meeste van deze chips hebben een vorm van programmeerbaarheid. Daarnaast is er de productie, inclusief de testers, testopstellingen en inbrandarmaturen voor het uitvoeren van versnelde levensduurtests.”

Zelfs IP-kosten kunnen een belangrijke variabele zijn, vooral als je kijkt naar de tijdsbesparing die wordt behaald door het inkopen van IP, of de indirecte kosten die gepaard gaan met de ontwikkeling van IP. “De stijging van de kosten en complexiteit van SoC-ontwerpen legt meer druk op de computerinfrastructuur”, zegt Brian Jeff, senior directeur productmanagement bij Arm's Infrastructuurbranche. “Dit stimuleert een trend naar op maat gemaakt silicium om gespecialiseerde verwerking voor specifieke workloads te bieden en efficiëntiebesparingen op grote schaal te realiseren. Door IP te ontwikkelen met een aanpasbare basis, kan de IP-provider veel van de algemene integratie-, verificatie- en validatietaken op zich nemen die partners ontwerp na ontwerp moesten herhalen. Dit geeft partners de vrijheid om hun middelen te concentreren op de functies die hen zullen helpen zich te differentiëren en een volledig chipontwerp aan te passen aan hun werklast. In één voorbeeld heeft een partner de kosten van de SoC-ontwikkeling van hun hoogwaardige infrastructuur met 80 engineeringjaren verlaagd.”

Veel van de kosten zijn oplopend. “We leren niet alles opnieuw tussen procesknooppunten”, zegt Katz. “We onthouden de dingen die we moeten doen. We hebben veel geïnvesteerd in de parametrisering of in de representatie van ontwerpartefacten vanaf de top, de testbench, de manier waarop we het IP beschrijven, en de manier waarop we de aangepaste logica en versnellers verwoorden, helemaal tot aan de manier waarop we het indelen. de cellen. We begrijpen waar we aanpassingen moeten maken en hebben draaiknoppen en knoppen waarmee we daarvoor kunnen corrigeren. Niemand begint vanaf nul tussen knooppunten. Zelfs als we de manier veranderen waarop de transistoroppervlakken werken, of we de manier reorganiseren waarop het personalisatiemetaal van het eerste niveau gaat werken, moeten we extra tijd besteden aan het karakteriseren daarvan. We moeten extra tijd besteden aan het begrijpen hoe we dat kunnen extraheren, en misschien moeten we kleine en bescheiden aanpassingen maken aan onze celontwerpen om dit mogelijk te maken. Maar de basistopologie is er.”

Goed ontwikkelde IP zal herbruikbaar zijn voor meerdere generaties chips. Bedrijven als Intel, AMD, Marvell, Broadcom, NVIDIA en Qualcomm ontwikkelen een groot deel van hun IP in eigen beheer. Een deel hiervan heeft de vorm van chiplets, die volledig kunnen worden gekarakteriseerd en hergebruikt in vooraf bepaalde architecturen. De afweging daar is expertise in huis, maar er zijn ook minder verrassingen in het veld en geen licentiekosten.

Kosten van EDA

Elk knooppunt creëert een aantal nieuwe problemen en uitdagingen, en dat vereist vaak aanzienlijke investeringen van EDA-leveranciers in nieuwe tools of het creëren van stromen. Wanneer het knooppunt nieuw is, zijn veel van deze instrumenten primitief en worden oplossingen samengevoegd met alle mogelijke technologieën die op het probleem kunnen worden toegepast.

Na verloop van tijd leert de industrie wat werkt en wat niet werkt, en de stromen verbeteren en worden uiteindelijk geautomatiseerd. “Veel uitdagingen worden met brute kracht overwonnen”, zegt Swinnen van Ansys. “Ze gebruikten de beschikbare hulpmiddelen en met voldoende mensen en lieten het werken. Dat vereiste een nauwe samenwerking met de leveranciers. Het is geen stroom die je zou kunnen geven aan reguliere reguliere chipontwerpers. Na verloop van tijd leren wij van hen, en zij leren van ons. De gereedschappen worden beter, meer geautomatiseerd, de ruwe randen zijn gladgestreken, de handmatige tussenstappen zijn verminderd. Dat maakt de productiviteit veel hoger.”

Wat vandaag werkt, zal in de toekomst misschien niet werken. “Er is een portfolio met dingen waarvoor je plannen moet maken”, zegt Katz. “Ik ben betrokken geweest bij timing, procesvariatie en grondstuiteren. Wanneer u uw spanningsdrempels verlaagt tot onder 1V, worden veel van deze dingen problemen. Dat was nog onbekend toen we met 14nm begonnen. Tegenwoordig wordt het begrepen. Mensen begrijpen wat er mis kan gaan in de timing of de lay-out van het ontwerp. Ze begrijpen de factoren waar je op moet letten met betrekking tot de bijdrage van de metalen aan vertraging en timing, en ze zijn zich ook steeds meer bewust geworden van enkele van de fysieke bijwerkingen, gevoeligheid voor storingsgeluiden, gevoeligheid voor lekkage. Deze dragen allemaal bij aan het draaiboek. En het draaiboek leidt je door alle valkuilen van de afgelopen 10 of 15 jaar. Hoe ga je die aan? Hoe automatiseer je die? Of hoe ontwerp je die?’

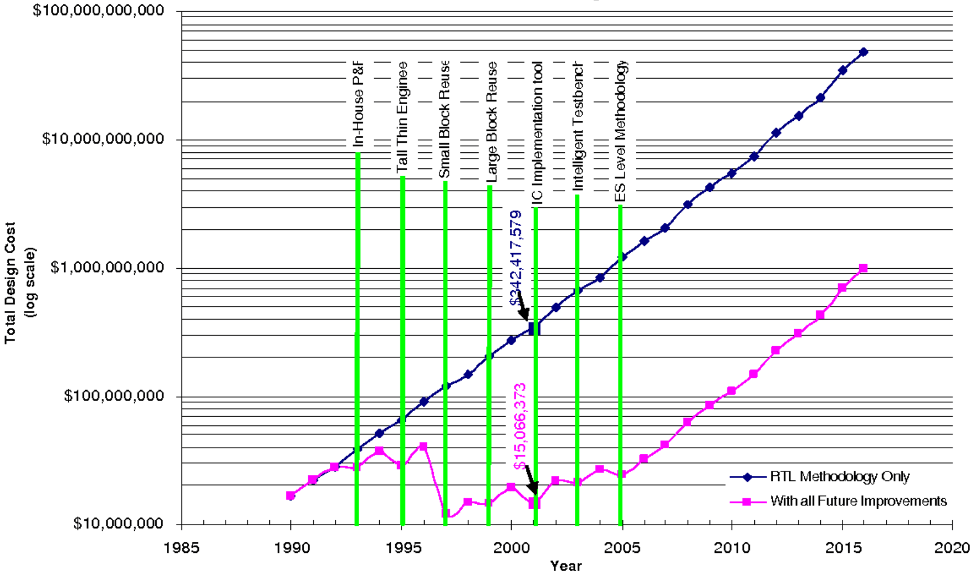

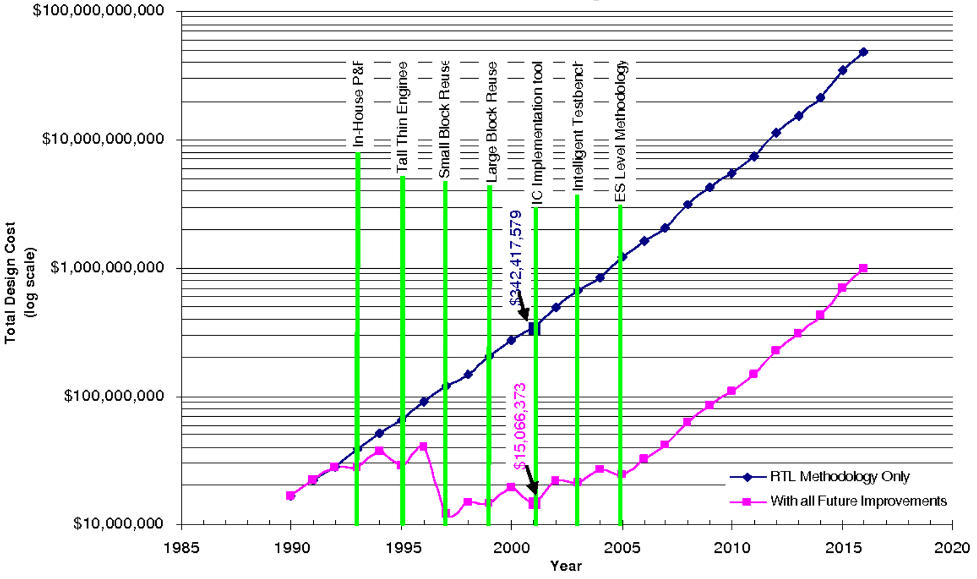

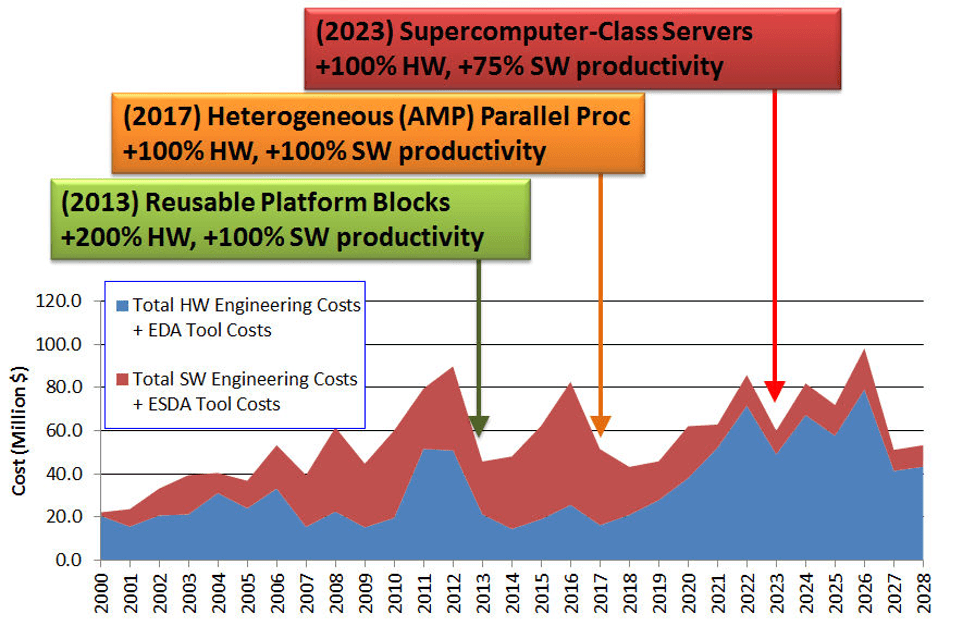

Een ander oud diagram dat de moeite waard is om opnieuw te bekijken, wordt weergegeven in figuur 4. Andrew Kahng en Gary Smith voerden in 2001 een analyse uit van de ontwerpkosten om te laten zien hoe nieuwe EDA-ontwikkelingen de productiviteit beïnvloedden. Dit werd in 2002 door de ITRS gepubliceerd.

Fig. 4: Een nieuw ontwerpkostenmodel voor de ITRS van 2001. Bron: Proceedings International Symposium on Quality Electronic Design 2002

Hoewel dit technologieën van de toekomst laat zien die nooit tot stand zijn gekomen, zoals ESL, hebben andere technologieën dat wel gedaan. Uit latere publicaties van de ITRS blijkt dat de ontwikkelingskosten enigszins statisch blijven, met slechts een kleine toename van de kosten in de loop van de tijd. Figuur 5 (hieronder) is hun grafiek uit 2013.

Fig. 5: EDA-impact op IC-ontwerpkosten. Bron: Andrew Kahng, 2013

De ontwikkelingskosten stijgen inderdaad, vooral voor nieuwe knooppunten. “De tools worden steeds geavanceerder en moeten meegroeien met de ontwerpgrootte”, zegt Ilyadis. “Doorgaans kunnen deze bijgewerkte tools van generatie op generatie 25% kosten met zich meebrengen, en dat is waar de gereedschapsbedrijven geld aan verdienen. Ze moeten zich ontwikkelen, ze moeten werk in hun tools stoppen om ze compatibel te maken met de volgende generatie IP en welke nieuwe uitdagingen zich ook voordoen, dus gaan ze die ontwikkelingskosten aan jou doorberekenen als hogere licentiekosten.

Maar dat is niet het geval voor reguliere ontwikkelaars. “In de economie van het ontwerpen van halfgeleiders zijn de kosten van de EDA-tools nooit een doorslaggevende overweging”, zegt Swinnen. “Het is een kostenelement waar iemand zich zorgen over moet maken, maar in de algemene economie van chipontwerp is EDA nooit de doorslaggevende factor. Het is productie. Waar EDA wel invloed heeft op de kosten van het ontwerp, zit meer in de productiviteit.”

Wat we zien zijn de snel stijgende infrastructuurkosten die verband houden met EDA-instrumenten. “Nu AI wordt geïntroduceerd in toolsuites, is het gemakkelijk om de ontwerpruimte verder te verkennen”, zegt Schirrmeister. “Elk datapunt in hun grafieken betekent extra capaciteit en cycli die in de cloud worden uitgevoerd. Om de beste implementatie te krijgen, besteedt u nu meer rekeninspanning. Wat vroeger mensen waren, vermenigvuldigd met tijd en wat infrastructuurkosten, wordt nu een herverdeling van kosten, waarbij de computerkosten zelf een veel grotere rol spelen in de totale kostenvergelijking.”

Conclusie

Geen enkele chip die ooit is ontwikkeld, heeft zoveel gekost als wat in de gepubliceerde cijfers wordt weergegeven, simpelweg omdat er geen chip is die echt begint met een blanco vel papier. Alles in deze industrie is gebaseerd op het hergebruik van intellectueel eigendom, een deel ervan vastgelegd in IP-blokken, een deel ervan in BSIM-modellen, een deel ervan in de hoofden van de ingenieurs die een nieuw bedrijf starten. Hetzelfde, zo niet meer, kan gezegd worden over de software-industrie die altijd voortbouwt op enorme codebibliotheken.

Maar deze cijfers liggen in de juiste orde van grootte voor toonaangevende ontwerpen. Het is belangrijk om inzicht te krijgen in de totale kosten die met de ontwikkeling gepaard gaan, en ons niet alleen te concentreren op het verkrijgen van siliciumtapeout.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiengineering.com/what-will-that-chip-cost/