Chiplets krijgen hernieuwde aandacht op de automarkt, waar de toenemende elektrificatie en hevige concurrentie bedrijven dwingen hun ontwerp- en productieschema's te versnellen.

Elektrificatie heeft het vuur aangestoken onder enkele van de grootste en bekendste autofabrikanten, die moeite hebben om concurrerend te blijven ondanks zeer korte marktvensters en voortdurend veranderende eisen. Anders dan in het verleden, toen autofabrikanten doorgaans ontwerpcycli van vijf tot zeven jaar hanteerden, kan de nieuwste technologie in voertuigen tegenwoordig als verouderd worden beschouwd. En als ze het niet bij kunnen houden, is er een hele nieuwe lichting startups die goedkope voertuigen produceren met de mogelijkheid om functies net zo snel bij te werken of te wijzigen als een software-update.

Maar software heeft beperkingen op het gebied van snelheid, veiligheid en betrouwbaarheid, en het kunnen aanpassen van de hardware is waar veel autofabrikanten nu hun best voor doen. Dit is waar chiplets in passen, en de focus ligt nu op het opbouwen van voldoende interoperabiliteit tussen grote ecosystemen om hiervan een plug-and-play-markt te maken. De belangrijkste factoren om de interoperabiliteit van auto-chiplets mogelijk te maken, zijn onder meer standaardisatie, interconnect-technologieën, communicatieprotocollen, energie- en thermisch beheer, beveiliging, testen en samenwerking met ecosystemen.

Net als bij niet-automobieltoepassingen op bestuursniveau, zijn veel ontwerpinspanningen gericht op een die-to-die-benadering, wat een aantal nieuwe ontwerpoverwegingen en afwegingen tot gevolg heeft. Op chipniveau worden de verbindingen tussen verschillende processors, chips, geheugen en I/O steeds complexer als gevolg van de hogere eisen aan de ontwerpprestaties, wat een golf van standaardactiviteiten tot gevolg heeft. Er zijn verschillende soorten verbindingen en interfaces voorgesteld om verschillende doeleinden te dienen, terwijl ze in opkomst zijn chipje Technologieën voor specifieke functies – processors, geheugens en I/O’s, om er maar een paar te noemen – veranderen de benadering van chipontwerp.

“Er is een besef bij auto-OEM’s dat ze, om hun eigen lot te beheersen, hun eigen SoC’s zullen moeten beheersen”, zegt David Fritz, vice-president van virtuele en hybride systemen bij Siemens EDA. “Ze begrijpen echter niet hoe ver EDA is gekomen sinds ze in 1982 op de universiteit zaten. Ze geloven ook dat ze naar het nieuwste procesknooppunt moeten gaan, waar een maskerset 100 miljoen dollar gaat kosten. Dat kunnen ze zich niet veroorloven. Ze hebben ook geen toegang tot talent omdat de talentenpool vrij klein is. Met dat alles bij elkaar komt het besef van de OEM's dat ze, om hun lot te beheersen, een technologie nodig hebben die door anderen is ontwikkeld, maar die kan worden gecombineerd, hoe dan ook nodig om een uniek, gedifferentieerd product te hebben waarvan ze zeker zijn dat het toekomstbestendig is voor ten minste een paar mensen. modeljaren. Dan wordt het economisch levensvatbaar. Het enige dat daarbij past zijn chiplets.”

Chiplets kunnen worden geoptimaliseerd voor specifieke functies, waardoor autofabrikanten kunnen voldoen aan de eisen op het gebied van betrouwbaarheid, veiligheid en beveiliging met technologie die zich in meerdere voertuigontwerpen heeft bewezen. Bovendien kunnen ze de time-to-market verkorten en uiteindelijk de kosten van verschillende kenmerken en functies verlagen.

De vraag naar chips is de afgelopen tien jaar toegenomen. Volgens Allied Market Research zal de mondiale vraag naar auto-chips groeien van 49.8 miljard dollar in 2021 naar 121.3 miljard dollar in 2031. Die groei zal nog meer innovatie en investeringen in auto-chips aantrekken, en naar verwachting zullen chiplets daar een grote begunstigde van zijn.

Maar het zal enige tijd duren voordat de markt voor chiplets volwassen is geworden, en deze zal waarschijnlijk in fasen worden uitgerold. In eerste instantie zal een leverancier verschillende smaken eigen matrijzen leveren. Vervolgens zullen partners samenwerken om chiplets te leveren om elkaar te ondersteunen, zoals al is gebeurd met sommige leveranciers. De laatste fase zal bestaan uit universeel interoperabele chiplets, zoals ondersteund door UCIe of een ander interconnectieschema.

Het zal het moeilijkst zijn om de laatste fase te bereiken, en er zullen aanzienlijke veranderingen nodig zijn. Om interoperabiliteit te garanderen moeten delen van het auto-ecosysteem en de toeleveringsketen die groot genoeg zijn, samenkomen, inclusief hardware- en softwareontwikkelaars, gieterijen, OSAT's en leveranciers van materiaal en apparatuur.

Het momentum neemt toe

Het positieve is dat dit allemaal niet helemaal opnieuw begint. Op bordniveau hebben modules en subsystemen altijd gebruik gemaakt van ingebouwde chip-naar-chip-interfaces, en dat zullen ze ook blijven doen. Verschillende chip- en IP-providers, waaronder Cadence, Diode, Microchip, NXP, Renesas, Rambus, Infineon, Arm en Synopsys, leveren kant-en-klare interfacechips of IP om het interface-silicium te creëren.

Het Universal Chiplet Interconnect Express (UCIe)-consortium is de drijvende kracht achter de die-to-die, open interconnect-standaard. De groep heeft in augustus 1.1 de nieuwste UCIe 2023-specificatie uitgebracht. Tot de bestuursleden behoren onder meer Alibaba, AMD, Arm, ASE, Google Cloud, Intel, Meta, Microsoft, NVIDIA, Qualcomm en Samsung. Partners uit de industrie tonen brede steun. AIB en Bunch of Wires (BoW) zijn ook voorgesteld. Bovendien heeft Arm zojuist zijn eigen Chiplet-systeemarchitectuur uitgebracht, samen met een bijgewerkte AMBA-specificatie om protocollen voor chiplets te standaardiseren.

“Chiplets zijn er al, gedreven door noodzaak”, zegt Arif Khan, senior productmarketinggroepdirecteur voor design IP bij Cadence. “De groeiende processor- en SoC-groottes bereiken de richtkruislimiet en de schaalnadelen. De incrementele winsten uit de vooruitgang op het gebied van de procestechnologie zijn lager dan de stijgende kosten per transistor en ontwerp. De vooruitgang op het gebied van verpakkingstechnologie (2.5D/3D) en interfacestandaardisatie op een die-to-die-niveau, zoals UCIe, zullen de ontwikkeling van chiplets vergemakkelijken.”

Bijna alle chiplets die tegenwoordig worden gebruikt, zijn in eigen huis ontwikkeld door grote chipmakers zoals Intel, AMD en Marvell, omdat ze de kenmerken en het gedrag van die chiplets nauwlettend kunnen controleren. Maar er wordt op elk niveau gewerkt aan het openstellen van deze markt voor meer spelers. Wanneer dat gebeurt, kunnen kleinere bedrijven beginnen te profiteren van wat de spraakmakende pioniers tot nu toe hebben bereikt, en rond die ontwikkelingen gaan innoveren.

“Velen van ons geloven dat het waarschijnlijk jaren zal duren voordat de droom van een kant-en-klare, interoperabele chipletportfolio werkelijkheid zal worden”, zegt Guillaume Boillet, senior director strategische marketing bij Arteris, eraan toevoegend dat interoperabiliteit zal voortkomen uit groepen partners die pakken het risico van onvolledige specificaties aan.

Dit vergroot ook de aantrekkelijkheid van FPGA's en eFPGA's, die een niveau van maatwerk en updates voor hardware in het veld kunnen bieden. “Chiplets bestaan echt”, zegt Geoff Tate, CEO van Flex Logix. “Op dit moment kan een bedrijf dat twee of meer chiplets bouwt veel economischer opereren dan een bedrijf dat een chip van bijna dradenkruisformaat bouwt met vrijwel geen opbrengst. Chiplet-standaardisatie lijkt nog ver weg. Zelfs UCIe is nog geen vaste standaard. Niet iedereen is het eens over UCIe, bare die-tests, en wie de eigenaar is van het probleem als het geïntegreerde pakket niet werkt, enz. We hebben wel een aantal klanten die eFPGA gebruiken of evalueren voor interfaces waar standaarden in beweging zijn, zoals UCIe. Ze kunnen nu silicium implementeren en de eFPGA gebruiken om later aan standaardwijzigingen te voldoen.”

Er zijn ook andere inspanningen die chiplets ondersteunen, zij het om enigszins andere redenen – met name de stijgende kosten van het schalen van apparaten en de noodzaak om meer functies in chips op te nemen, die op de meest geavanceerde knooppunten beperkt zijn in het dradenkruis. Maar deze inspanningen maken ook de weg vrij voor chiplets in de automobielsector, en er bestaat sterke steun van de industrie om dit allemaal te laten werken. Onder de sponsoring van SEMI, ASME en drie IEEE Societies kijkt de nieuwe Heterogene Integration Roadmap (HIR) bijvoorbeeld naar verschillende micro-elektronische ontwerp-, materialen- en verpakkingsvraagstukken om een routekaart voor de halfgeleiderindustrie te bedenken. Hun huidige focus omvat 2.5D, 3D-IC's, verpakkingen op waferniveau, geïntegreerde fotonica, MEMS en sensoren, en system-in-package (SiP), ruimtevaart, automobielindustrie en meer.

Op de recente Heterogeneous Integration Global Summit 2023 hebben vertegenwoordigers van AMD, Applied Materials, ASE, Lam Research, MediaTek, Micron, Onto Innovation, TSMC, en anderen toonden sterke steun voor chiplets. Een andere groep die chiplets ondersteunt, is de Chiplet-ontwerpuitwisseling (CDX) werkgroep, die deel uitmaakt van de Open domeinspecifieke architectuur (ODSA) en de Open Compute Project Foundation (OCP). Het Chiplet Design Exchange (CDX)-charter richt zich op de verschillende kenmerken van chiplet- en chiplet-integratie, inclusief elektrische, mechanische en thermische ontwerpuitwisselingsstandaarden van de 2.5D gestapelde en 3D Integrated Circuits (3D-IC's). Tot zijn vertegenwoordigers behoren Ansys, Applied Materials, Arm, Ayar Labs, Broadcom, Cadence, Intel, Macom, Marvell, Microsemi, NXP, Siemens EDA, Synopsys en anderen.

"De dingen die autobedrijven willen op het gebied van wat elke chiplet doet op het gebied van functionaliteit, bevinden zich nog steeds in een roerige fase", merkte Fritz van Siemens op. “Het ene uiterste heeft deze problemen, het andere uiterste heeft deze problemen. Dit is de goede plek. Dit is wat nodig is. En dit zijn het soort bedrijven die dat soort werk kunnen doen, en dan zou je ze kunnen samenbrengen. Dan is dit interoperabiliteitsgedoe geen probleem. De OEM kan het te complex maken door te zeggen: 'Ik moet met dat hele spectrum aan mogelijkheden omgaan.' Het alternatief is dat ze zouden kunnen zeggen: 'Het is net een snelle PCIe. Als ik van de een naar de ander wil communiceren, weet ik al hoe ik dat moet doen. Ik heb stuurprogramma's waarop mijn besturingssysteem draait. Dat zou heel veel problemen oplossen, en ik denk dat het daar ook zal eindigen.”

Eén pad naar de ontwikkeling van universele chiplets?

In de toekomst zullen chiplets een centraal punt vormen voor zowel de auto- als de chipindustrie, en dat zal alles omvatten, van chiplet-IP tot geheugenverbindingen en aanpassingsopties en -beperkingen.

Renesas Electronics kondigde bijvoorbeeld in november 2023 plannen aan voor zijn volgende generatie SoC's en MCU's. Het bedrijf richt zich op alle belangrijke toepassingen in het digitale domein van de auto-industrie, inclusief geavanceerde informatie over de vijfde generatie R-Car SoC voor krachtige toepassingen met geavanceerde in-package chiplet-integratietechnologie, die bedoeld zijn om auto-ingenieurs meer flexibiliteit te bieden bij het aanpassen hun ontwerpen.

Renesas merkte op dat als er meer AI-prestaties nodig zijn in Advanced Driver Assistance Systems (ADAS), ingenieurs de mogelijkheid zullen hebben om AI-versnellers in één chip te integreren. Het bedrijf zegt dat deze routekaart het resultaat is van jarenlange samenwerking en discussies met Tier 1- en OEM-klanten, die hebben gepleit voor een manier om de ontwikkeling te versnellen zonder concessies te doen aan de kwaliteit, inclusief het ontwerpen en verifiëren van de software nog voordat de hardware beschikbaar is.

“Vanwege de steeds toenemende behoefte aan meer compute-on-demand en de toenemende behoefte aan hogere niveaus van autonomie in de auto’s van morgen, zien we uitdagingen in het opschalen van monolithische oplossingen en het voorzien in de prestatiebehoeften van de markt in de komende jaren”, aldus Vasanth Waran, senior directeur voor SoC Business & Strategies bij Renesas. “Chiplets zorgt ervoor dat de computeroplossingen verder kunnen worden geschaald dan de behoeften van de markt.”

Renesas kondigde plannen aan om een chiplet-gebaseerde productfamilie specifiek gericht op de automarkt vanaf 2025.

Standaardinterfaces maken SoC-aanpassing mogelijk

Het is niet helemaal duidelijk hoeveel overlap er zal zijn tussen standaardprocessors, waar tegenwoordig de meeste chiplets worden gebruikt, en chiplets die zijn ontwikkeld voor automobieltoepassingen. Maar de onderliggende technologieën en ontwikkelingen zullen zeker op elkaar voortbouwen naarmate deze technologie zich naar nieuwe markten verplaatst.

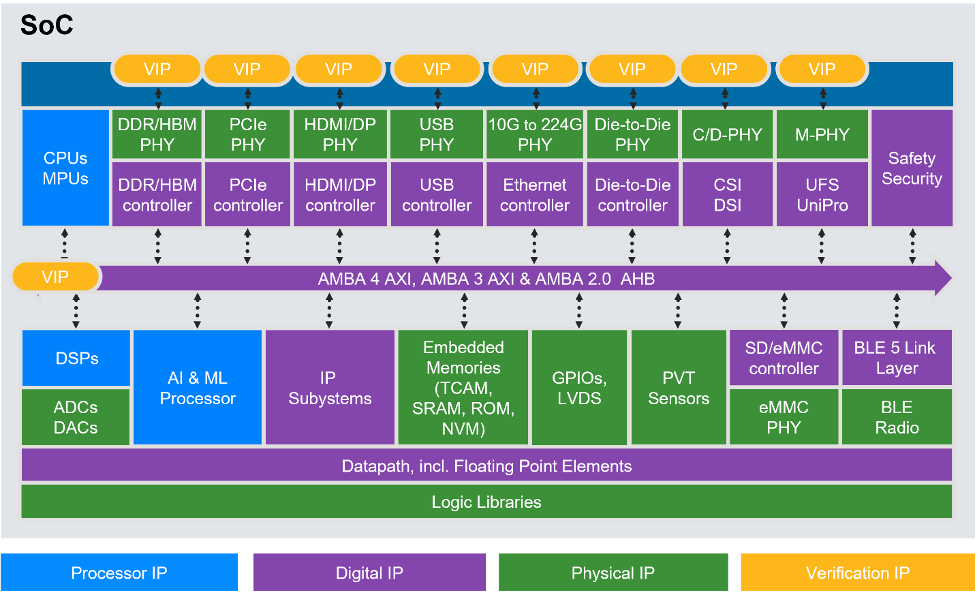

“Of het nu gaat om een AI-accelerator of een ADAS-autotoepassing, klanten hebben standaard interface-IP-blokken nodig”, zegt David Ridgeway, senior productmanager, IP-accelerated solutions group bij Synopsys. “Het is belangrijk om volledig geverifieerde IP-subsystemen te bieden rond hun IP-aanpassingsvereisten ter ondersteuning van de subsysteemcomponenten die worden gebruikt in de SoC's van klanten. Als ik maatwerk zeg, realiseer je je misschien niet hoe aanpasbaar IP in de loop van de afgelopen 10 tot 20 jaar is geworden, zowel aan de PHY-kant als aan de controllerkant. PCI Express is bijvoorbeeld overgegaan van PCIe Gen 3 naar Gen 4, naar Gen 5 en nu Gen 6. De controller kan worden geconfigureerd om meerdere bifurcatiemodi met kleinere linkbreedtes te ondersteunen, waaronder één x16, twee x8 of vier x4. Ons subsysteem-IP-team werkt samen met klanten om ervoor te zorgen dat aan alle aanpassingsvereisten wordt voldaan. Voor AI-toepassingen is signaal- en stroomintegriteit uiterst belangrijk om aan hun prestatie-eisen te voldoen. Bijna al onze klanten proberen de grenzen te verleggen om de hoogst mogelijke geheugenbandbreedtesnelheden te bereiken, zodat hun TPU veel meer transacties per seconde kan verwerken. Wanneer de toepassingen cloud computing of kunstmatige intelligentie zijn, willen klanten de snelst mogelijke respons.”

Figuur 1: IP-blokken inclusief processor, digitaal, PHY en verificatie helpen ontwikkelaars de volledige SoC te implementeren. Bron: Synopsys

Het optimaliseren van PPA dient het uiteindelijke doel van het verhogen van de efficiëntie, en dit maakt chiplets bijzonder aantrekkelijk in automobieltoepassingen. Wanneer UCIe volwassen wordt, wordt verwacht dat de algehele prestaties exponentieel zullen verbeteren. UCIe kan bijvoorbeeld een kustlijnbandbreedte leveren van 28 tot 224 GB/s/mm in een standaardpakket, en 165 tot 1317 GB/s/mm in een geavanceerd pakket. Dit vertegenwoordigt een prestatieverbetering van 20 tot 100 keer. Het terugbrengen van de latentie van 20 ns naar 2 ns betekent een tienvoudige verbetering. Ongeveer 10 keer grotere energie-efficiëntie, bij 10 pJ/b (standaardpakket) en 0.5 pJ/b (geavanceerd pakket), is een ander pluspunt. De sleutel is het verkorten van de interfaceafstand waar mogelijk.

Om chipletontwerpen te optimaliseren, geeft het UCIe Consortium enkele suggesties:

- Zorgvuldige planningsoverweging van architecturale snijlijnen (dwz chipletgrenzen), optimalisatie voor vermogen, latentie, siliciumoppervlak en IP-hergebruik. Het aanpassen van één chiplet die een geavanceerd procesknooppunt nodig heeft, terwijl het hergebruiken van andere chiplets op oudere knooppunten, kan bijvoorbeeld van invloed zijn op de kosten en tijd.

- Er moeten thermische en mechanische verpakkingsbeperkingen worden gepland voor thermische enveloppen van pakketten, hotspots, chipletplaatsingen en I/O-routing en breakouts.

- Procesknooppunten moeten zorgvuldig worden geselecteerd, vooral in de context van het bijbehorende stroomafgifteschema.

- Er moet van tevoren een teststrategie voor chiplets en verpakte/geassembleerde onderdelen worden ontwikkeld om ervoor te zorgen dat siliciumproblemen worden opgemerkt tijdens de testfase op chipletniveau, in plaats van nadat ze tot een pakket zijn geassembleerd.

Conclusie

Het idee om die-to-die-interfaces te standaardiseren slaat snel aan, maar de weg ernaartoe zal tijd, moeite en veel samenwerking vergen tussen bedrijven die zelden met elkaar praten. Voor het bouwen van een voertuig is één autofabrikant nodig. Voor het bouwen van een voertuig met chiplets is een heel ecosysteem nodig waarin de ontwikkelaars, gieterijen, OSAT's en materiaal- en apparatuurleveranciers samenwerken.

OEM's uit de automobielsector zijn experts in het samenstellen van systemen en het vinden van innovatieve manieren om kosten te besparen. Maar het valt nog te bezien hoe snel en effectief ze een ecosysteem van interoperabele chiplets kunnen bouwen en benutten om ontwerpcycli te verkleinen, maatwerk te verbeteren en zich aan te passen aan een wereld waarin de toonaangevende technologie verouderd kan zijn tegen de tijd dat deze volledig is ontworpen en getest. en beschikbaar voor consumenten.

— Ann Mutschler heeft bijgedragen aan dit rapport.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/