Voor het SEMI International Strategy Symposium 2024 werd ik door leden van het organisatiecomité uitgedaagd om te kijken waar de logica over tien jaar zal zijn vanuit een technologisch, economisch en duurzaamheidsperspectief. Hieronder volgt een bespreking van mijn presentatie.

Om logica te begrijpen, denk ik dat het nuttig is om te begrijpen waaruit geavanceerde logische apparaten bestaan. TechInsights produceert gedetailleerde footprintanalyserapporten, en ik heb rapporten gemaakt voor tien apparaten uit de 7nm- en 5nm-klasse, waaronder Intel- en AMD-microprocessors, Apple A-serie en M-serie processors, een NVIDIA GPU en andere apparaten. Figuur 1 illustreert waaruit het matrijsgebied bestaat.

Uit figuur 1 blijkt dat logica iets minder dan de helft van het chipoppervlak uitmaakt, geheugen iets minder dan een derde van de chip en I/O, analoog en andere de rest. Ik vind het interessant dat de feitelijk gemeten SRAM-geheugengebieden een stuk kleiner zijn dan het percentage waar ik mensen doorgaans over hoor praten voor System On a Chip (SOC)-producten. De grafiek rechtsonder laat zien dat er één uitschieter is, maar verder zijn de waarden strak geclusterd.

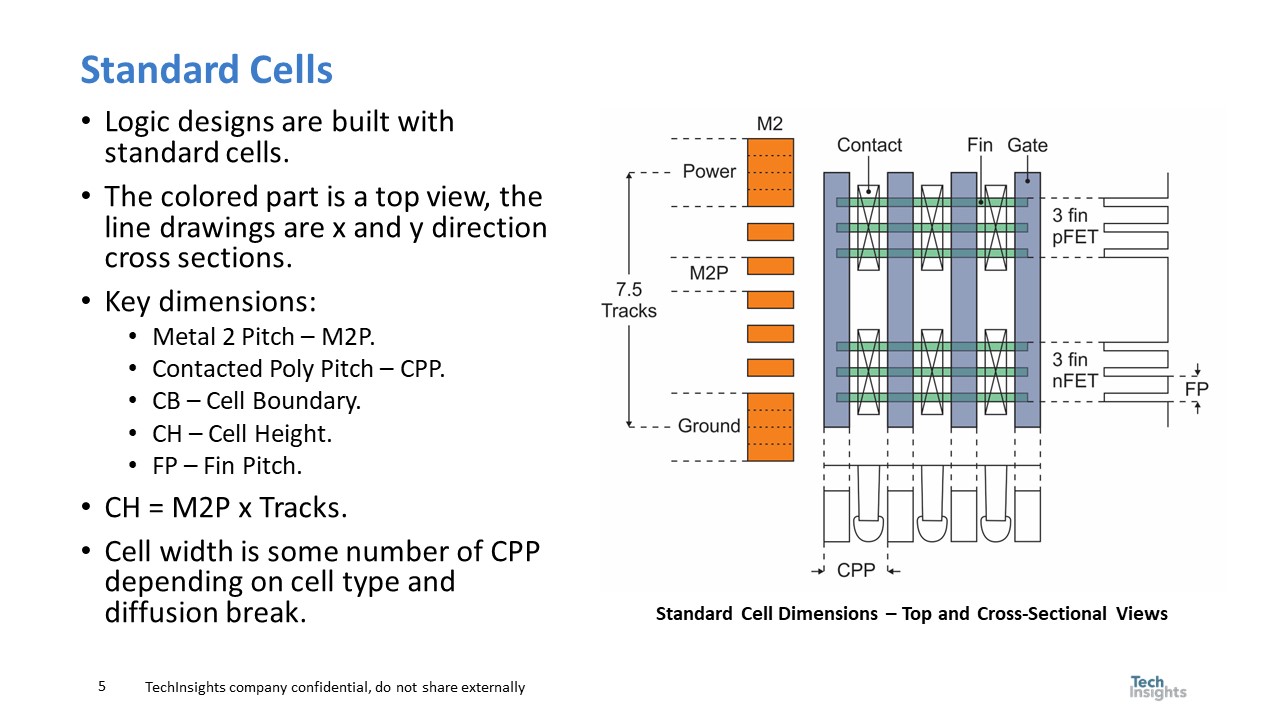

Enkelvoudige logica beslaat bijna de helft van het dobbelstenengebied, het is logisch om te beginnen met het logische deel van het ontwerp. Logische ontwerpen worden gemaakt met standaardcellen en figuur 2 is een bovenaanzicht van een standaardcel.

De hoogte van een standaardcel wordt doorgaans gekarakteriseerd als de Metal 2 Pitch (M2P) vermenigvuldigd met het aantal sporen, maar als je naar de rechterkant van de figuur kijkt, zie je een dwarsdoorsnede van de apparaatstructuur die ook moet overeenkomen met de celhoogte en wordt beperkt door apparaatfysica. Hetzelfde is het geval voor de celbreedte die afhangt van de Contacted Poly Pitch (CPP) en als je naar de onderkant van de figuur kijkt, zie je een dwarsdoorsnede van de apparaatstructuur die opnieuw wordt beperkt door de natuurkunde.

Figuur 3 presenteert het resultaat van een analyse om de praktische grenzen van de schaling van celbreedte en celhoogte te bepalen. Ik heb een presentatie waarin de schaalbeperkingen gedetailleerd worden beschreven en in die presentatie zijn er tientallen dia's tussen figuur 2 en figuur 3, maar met een beperkte tijd kon ik alleen de conclusie laten zien.

De schaal van de celbreedte is afhankelijk van CPP, en de linkerkant van de afbeelding illustreert hoe CPP is opgebouwd uit poortlengte (Lg), contactbreedte (Wc) en twee contact-tot-poort afstandsdiktes (Tsp). Lg wordt beperkt door lekkage en de minimale Lg met aanvaardbare lekkage hangt af van het apparaattype. Planaire apparaten met een enkele poort die het oppervlak van een kanaal met een onbeperkte dikte regelt, zijn beperkt tot ongeveer 30 nm. FinFET's en horizontale Nanosheets (HNS) beperken de kanaaldikte (~5nm) en hebben respectievelijk 3 en 4 poorten. Ten slotte introduceren 2D-materialen een kanaaldikte van <1 nm, niet-siliciummaterialen en kunnen ze Lg tot ~5 nm produceren. Zowel Wc als Tsp hebben een beperkt vermogen om te schalen als gevolg van parasitaire factoren. Het komt erop neer dat een 2D-apparaat waarschijnlijk een CPP van ~30 nm kan produceren, vergeleken met de huidige CPP's die ~50 nm zijn.

De schaal van de celhoogte wordt aan de rechterkant van de figuur geïllustreerd. HNS biedt stapels van enkele nanosheets in plaats van meerdere vinnen. Vervolgens elimineert de evolutie naar gestapelde apparaten met een CFET de horizontale np-afstand en worden de nFet en pFET gestapeld. Celhoogten die momenteel 150 nm tot 200 nm bedragen, kunnen worden teruggebracht tot ~50 nm.

De combinatie van CPP en celhoogteschaling kan transistordichtheden produceren van ~1,500 miljoen transistors per vierkante millimeter (MTx/mm).2) versus de huidige <300MTx/mm2. Opgemerkt moet worden dat 2D-materialen waarschijnlijk een technologie uit midden tot eind 2030 zijn, dus 1,500 MTx/mm2 valt buiten de hier besproken timing.

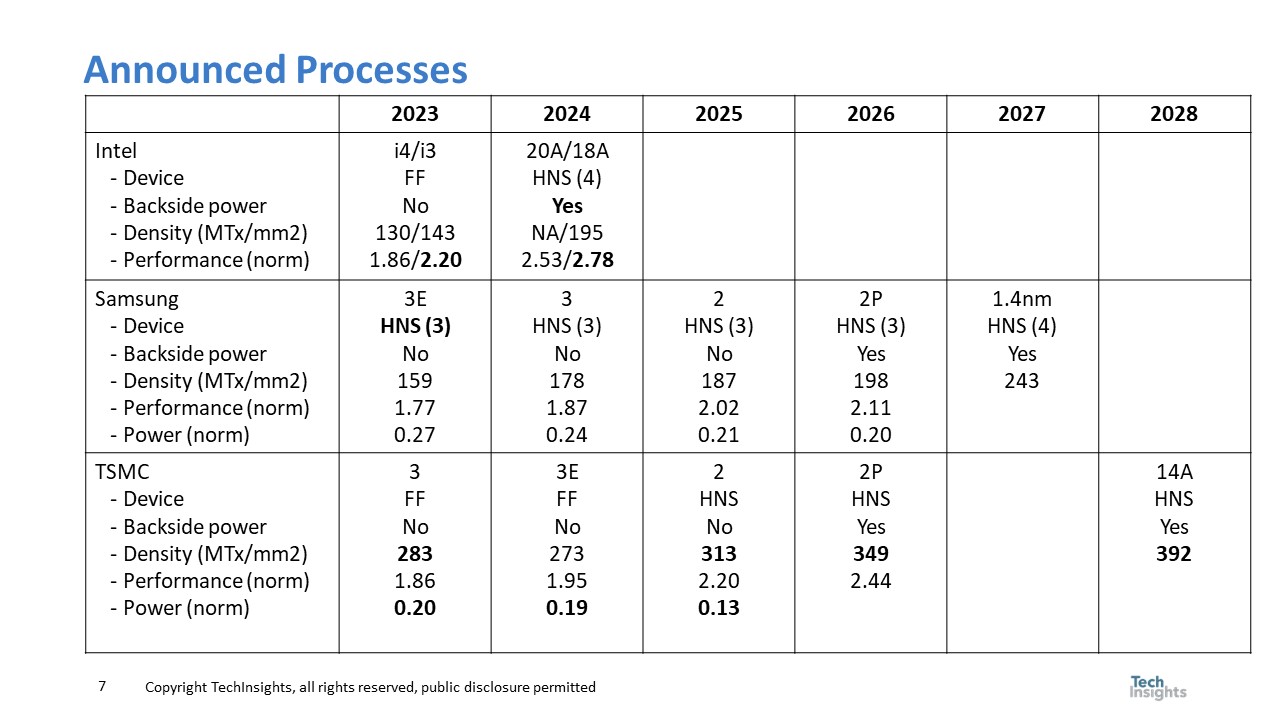

Figuur 4 geeft een samenvatting van aangekondigde processen van Intel, Samsung en TSMC.

Per bedrijf en jaartal wordt het apparaattype, of er al dan niet backside-stroom wordt gebruikt, dichtheid, vermogen en prestatie weergegeven indien beschikbaar. Kracht en prestaties zijn relatieve maatstaven en kracht is niet beschikbaar voor Intel.

In figuur 4 zijn toonaangevende prestatie- en technologische innovaties vetgedrukt weergegeven. Samsung is de eerste die HNS in 2023 in productie neemt, terwijl Intel HNS pas in 2024 en TSMC pas in 2025 zal introduceren. Intel is de eerste die in 2024 backside power in productie introduceert en Samsung en TSMC zullen dit pas in 2026 introduceren.

Mijn analyse concludeert dat Intel de prestatieleider is met i3 en handhaaft die status voor de geïllustreerde periode, TSMC heeft de machtsleider (Intel-gegevens niet beschikbaar) en dichtheidsleiderschap.

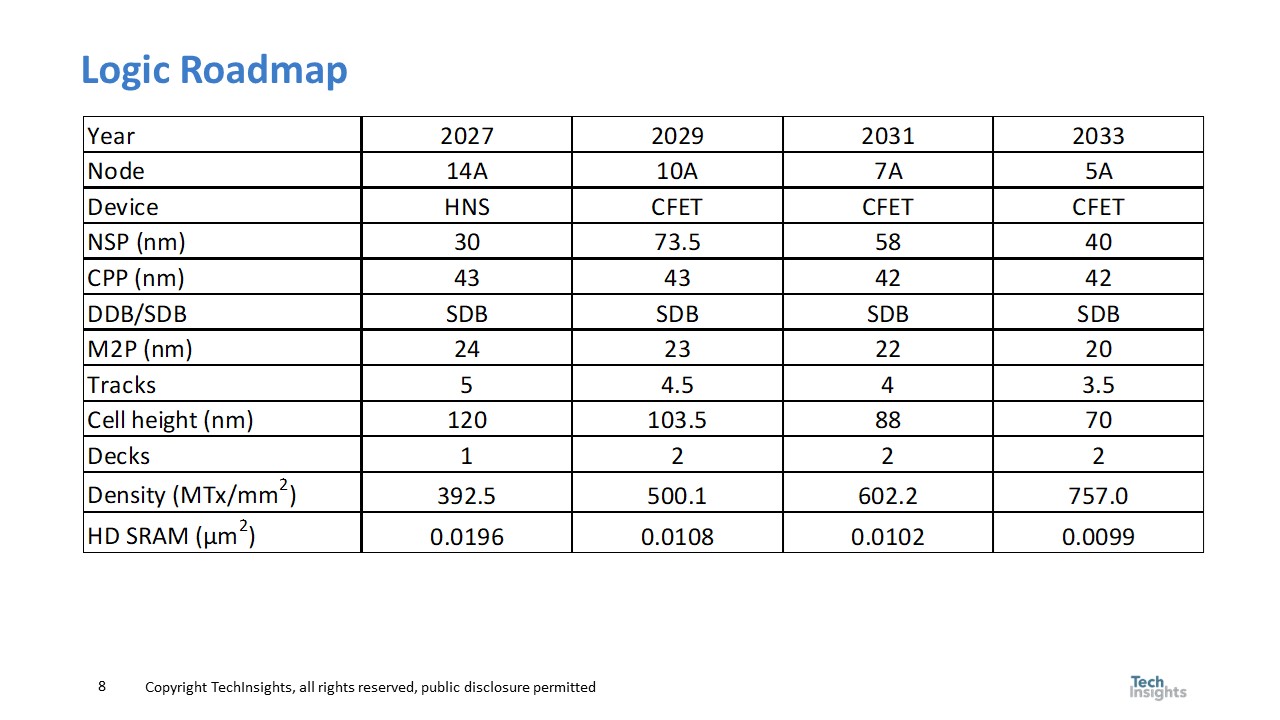

Figuur 5 presenteert onze logische routekaarten en bevat de verwachte SRAM-celgroottes (hierover later meer).

Op basis van figuur 5 verwachten we dat CFET's rond 2029 zullen worden geïntroduceerd, wat een boost zal geven aan de logische dichtheid en ook de SRAM-celgrootte bijna zal halveren (de schaalvergroting van de SRAM-celgrootte is vrijwel gestopt aan de voorrand). We verwachten dat de logische dichtheid ~757MTx/mm zal bereiken2 door 2034.

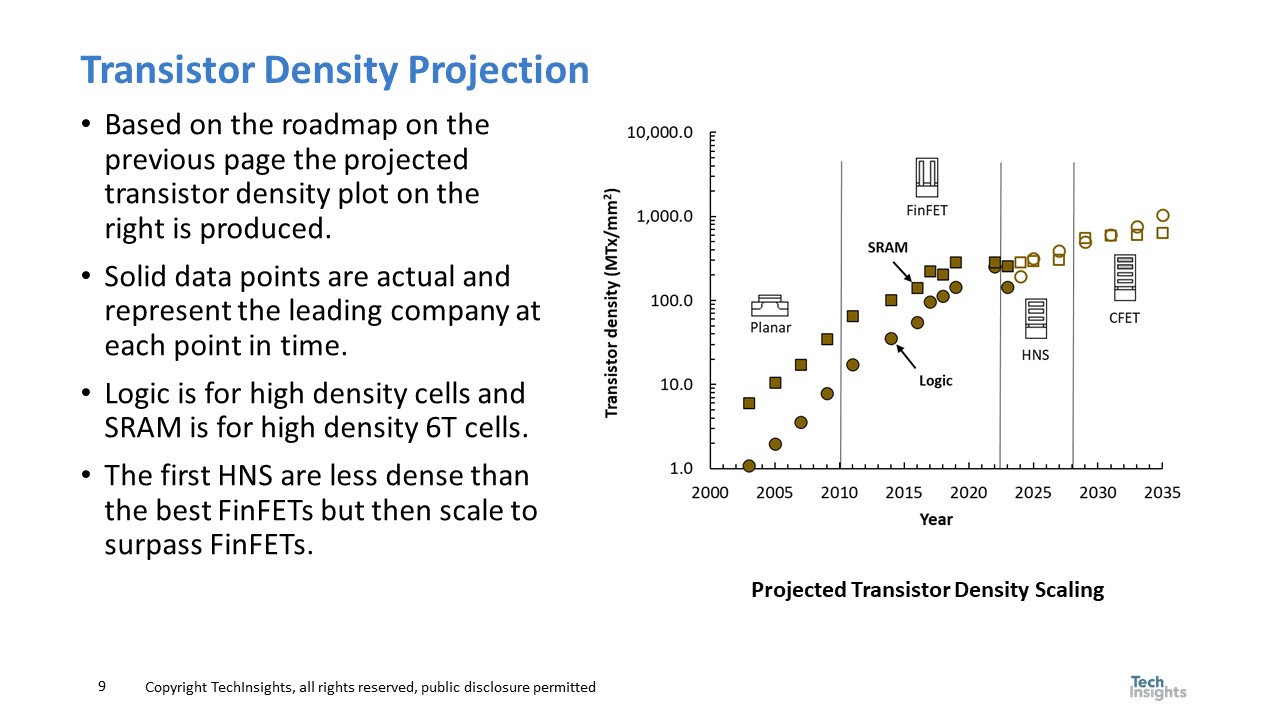

Zowel de logische transistordichtheidsprojecties als de SRAM-transistordichtheidsprojecties worden geïllustreerd in figuur 6.

Zowel de logische als de SRAM-transistordichtheidsschaling vertraagt, maar SRAM in grotere mate en logica heeft nu een vergelijkbare transistordichtheid als SRAM.

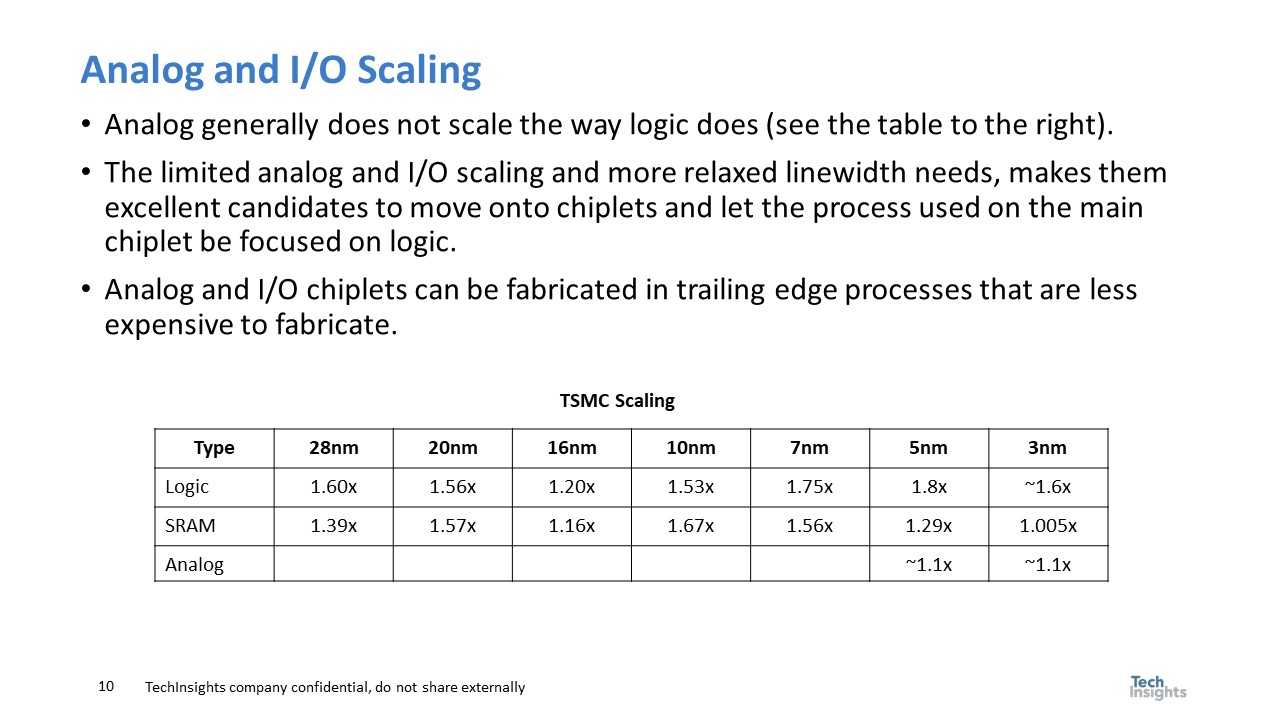

Dia 7 vat TSMC-gegevens samen over analoge schaling in vergelijking met Logic en SRAM. Analoge en I/O-schaling zijn beide langzamer dan logische schaling.

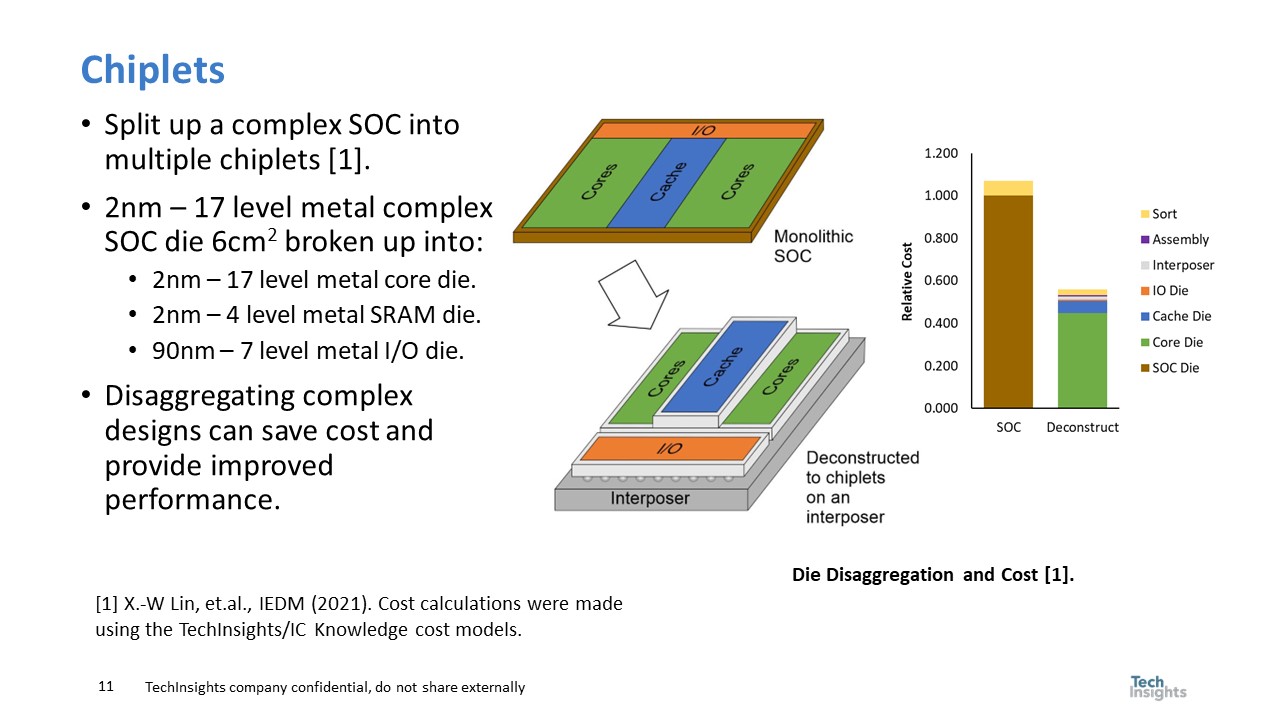

Een mogelijke oplossing voor langzamere SRAM en analoge en I/O-schaling zijn chiplets. Chiplets kunnen ervoor zorgen dat goedkopere en meer geoptimaliseerde processen kunnen worden gebruikt om SRAM en I/O te maken.

De figuur aan de rechterkant van figuur 8 komt uit een artikel uit 2021 dat ik samen met Synopsys heb geschreven. Onze conclusie was dat het opsplitsen van een grote SOC in chiplets de kosten zou kunnen halveren, zelfs als rekening wordt gehouden met de hogere verpakkings-/assemblagekosten.

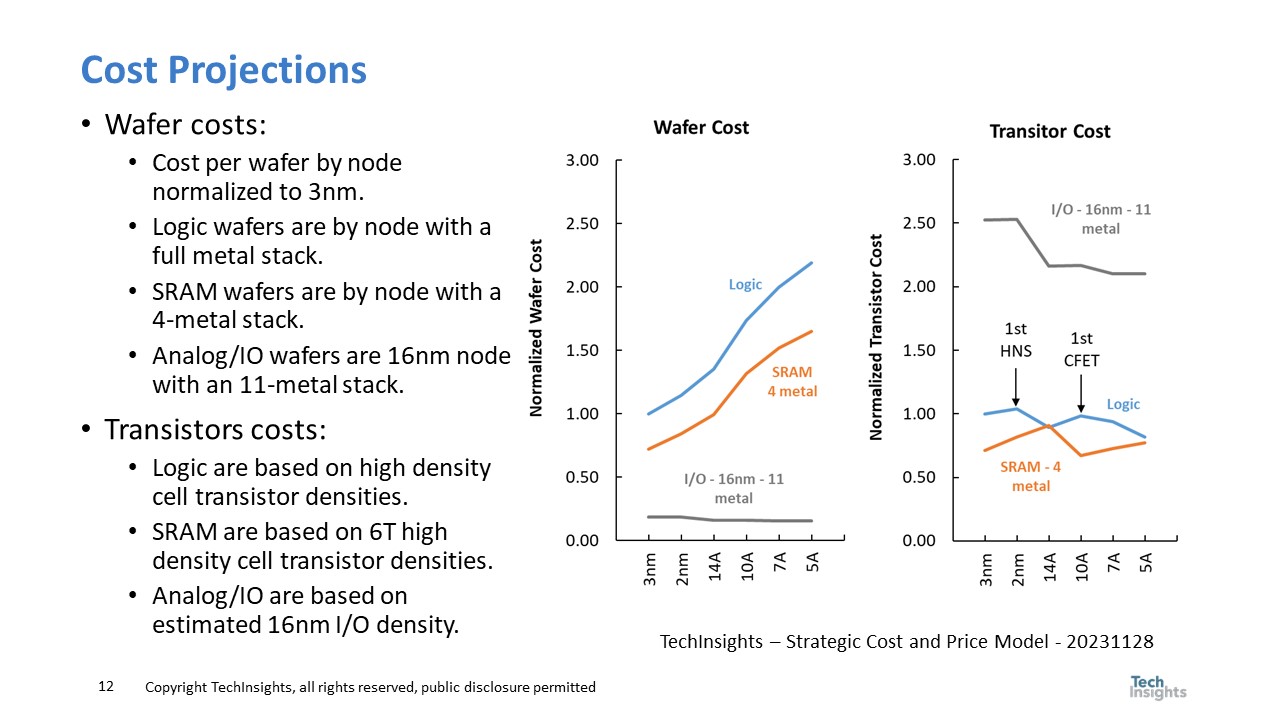

Figuur 9 toont genormaliseerde wafer- en transistorkosten voor logica, SRAM en I/O (let op: het cijfer is bijgewerkt ten opzichte van de oorspronkelijke presentatie).

In de rechterfiguur worden de genormaliseerde waferkosten weergegeven. De kosten voor logische wafers gelden voor een volledige metaalstapel die toeneemt in aantal metaallagen. De SRAM-wafels zijn dezelfde knooppunten, maar beperkt tot 4 metaallagen vanwege de meer regelmatige lay-out van SRAM. De I/O-waferkosten zijn gebaseerd op een 16 nm – 11 metaalproces. Ik heb 16 nm geselecteerd om een FinFET-knooppunt tegen minimale kosten te krijgen om adequate I/O-prestaties te garanderen.

De figuur rechts toont de waferkosten omgezet in transistorkosten. Interessant genoeg zijn de I/O-transistors zo groot dat ze zelfs op een goedkope 16 nm-wafer de hoogste kosten hebben (de I/O-transistorgrootte is gebaseerd op TechInsights-metingen van daadwerkelijke I/O-transistoren). De kosten van logische transistors stijgen bij 2 nm, het eerste TSMC HNS-bladknooppunt waar de krimp bescheiden is. We verwachten dat de krimp bij 14A groter zal zijn als een HNS-knooppunt van de tweede generatie (dit is vergelijkbaar met wat TSMC deed met hun eerste FinFET-knooppunt). Opnieuw verhogen de kosten van het eerste CFET-knooppunt ook de transistorkosten voor één knooppunt. De kosten van SRAM-transistors stijgen als gevolg van beperkte krimp, met uitzondering van een eenmalige CFET-krimp. De kern van deze analyse is dat de reductie van de transistorkosten bescheiden zal zijn, hoewel Chiplets een eenmalig voordeel kunnen opleveren.

Als we verder gaan met duurzaamheid, legt figuur 10 de verschillende ‘scopes’ uit die deel uitmaken van de COXNUMX-voetafdruk.

Scope 1 is de directe locatie-emissie als gevolg van proceschemicaliën en verbranding (elektrisch kan ook scope 1 zijn als deze ter plaatse wordt opgewekt), Scope 2 is te wijten aan de CO3-voetafdruk van gekochte elektriciteit. Scope XNUMX is niet meegenomen in deze analyse, maar heeft te maken met de COXNUMX-voetafdruk van gekochte materialen, het gebruik van het vervaardigde product en zaken als voertuigen die worden bestuurd door werknemers van een bedrijf.

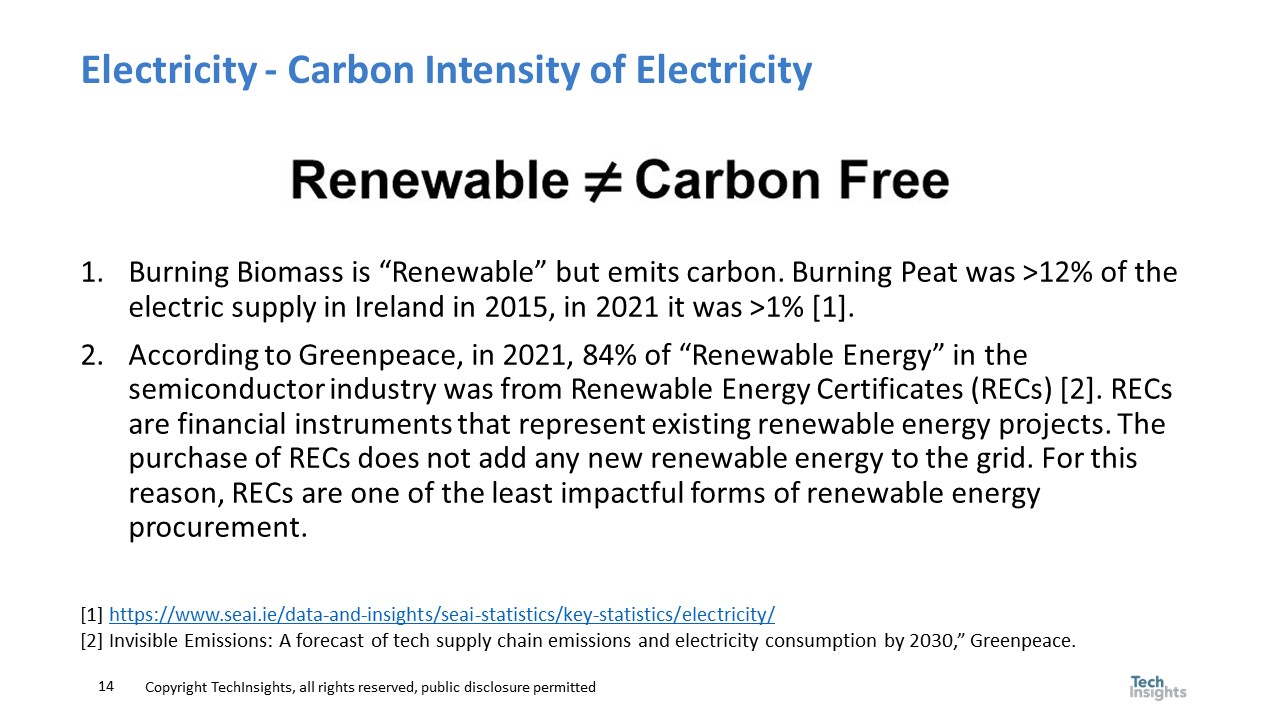

Veel bedrijven in de halfgeleiderindustrie beweren dat ze geen CO11-uitstoot veroorzaken als gevolg van elektriciteit, omdat de elektriciteit allemaal hernieuwbaar is. Figuur XNUMX vergelijkt hernieuwbaar met koolstofvrij.

Het belangrijkste probleem is dat 84% van de hernieuwbare energie in de halfgeleiderindustrie in 2021 door Greenpeace werd vastgesteld als hernieuwbare energiecertificaten waarbij een bedrijf de rechten koopt om reducties te claimen die iemand anders al heeft gedaan. Dit is niet hetzelfde als het installeren van koolstofarme elektrische bronnen of het betalen van anderen om koolstofarme elektriciteit te leveren, en het verlaagt feitelijk niet de mondiale koolstofvoetafdruk.

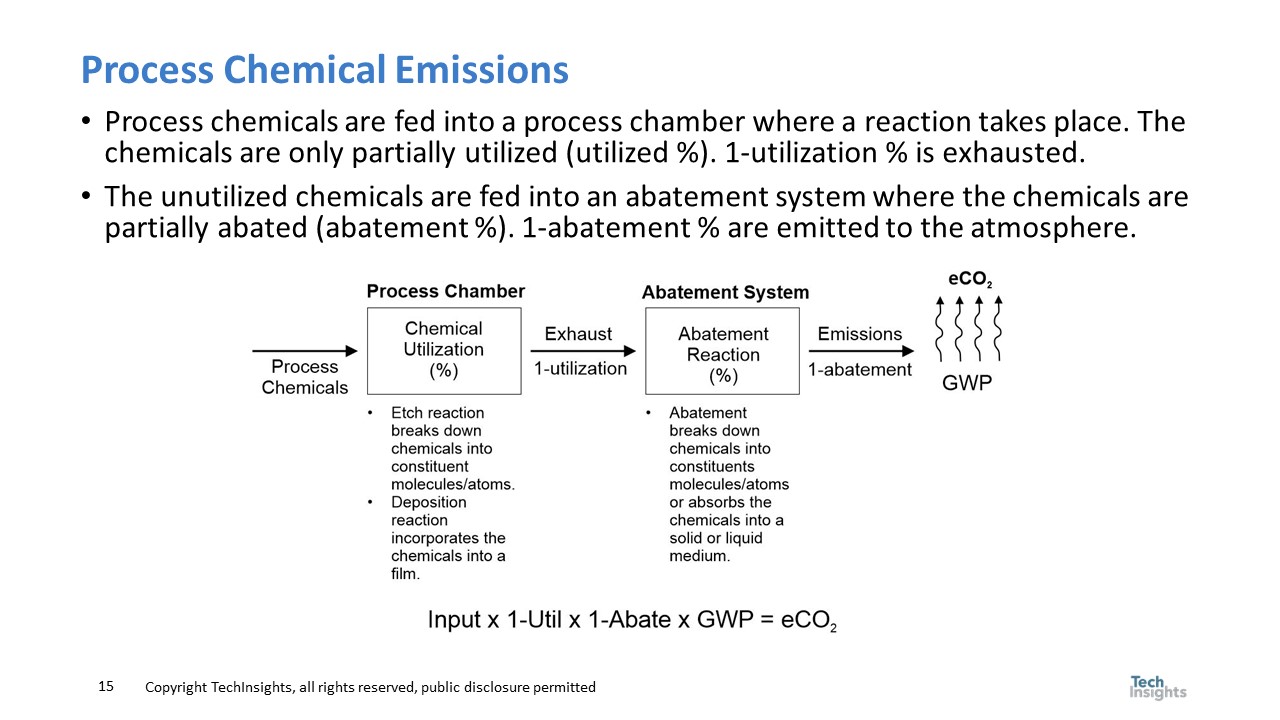

Figuur 12 illustreert hoe proceschemische emissies plaatsvinden en worden gekarakteriseerd.

Proceschemicaliën komen een proceskamer binnen waar een percentage van de chemicaliën wordt gebruikt in een ets- of afzettingsreactie die de chemicaliën afbreekt of in een afgezette film opneemt. 1-gebruik is de hoeveelheid chemische stof die uit de uitlaat van het gereedschap ontsnapt. De uitlaatgassen van het gereedschap kunnen dan naar een bestrijdingskamer gaan, waar een percentage van de chemicaliën verder wordt afgebroken en de emissies naar de atmosfeer als gevolg van de bestrijding zijn 1-reductie. Tenslotte wordt een Global Warming Potential (GWP) toegepast om de koolstofequivalentie van de uitstoot te berekenen. GWP houdt rekening met hoe lang de chemische stof in de atmosfeer blijft bestaan en hoeveel warmte de chemische stof terugkaatst in vergelijking met koolstofdioxide. Kooldioxide heeft een GWP van 1, halfgeleiderproceschemicaliën zoals SF6 en NF3 hebben GWP-waarden van respectievelijk 24,300 en 17,400 (volgens IPCC AR6).

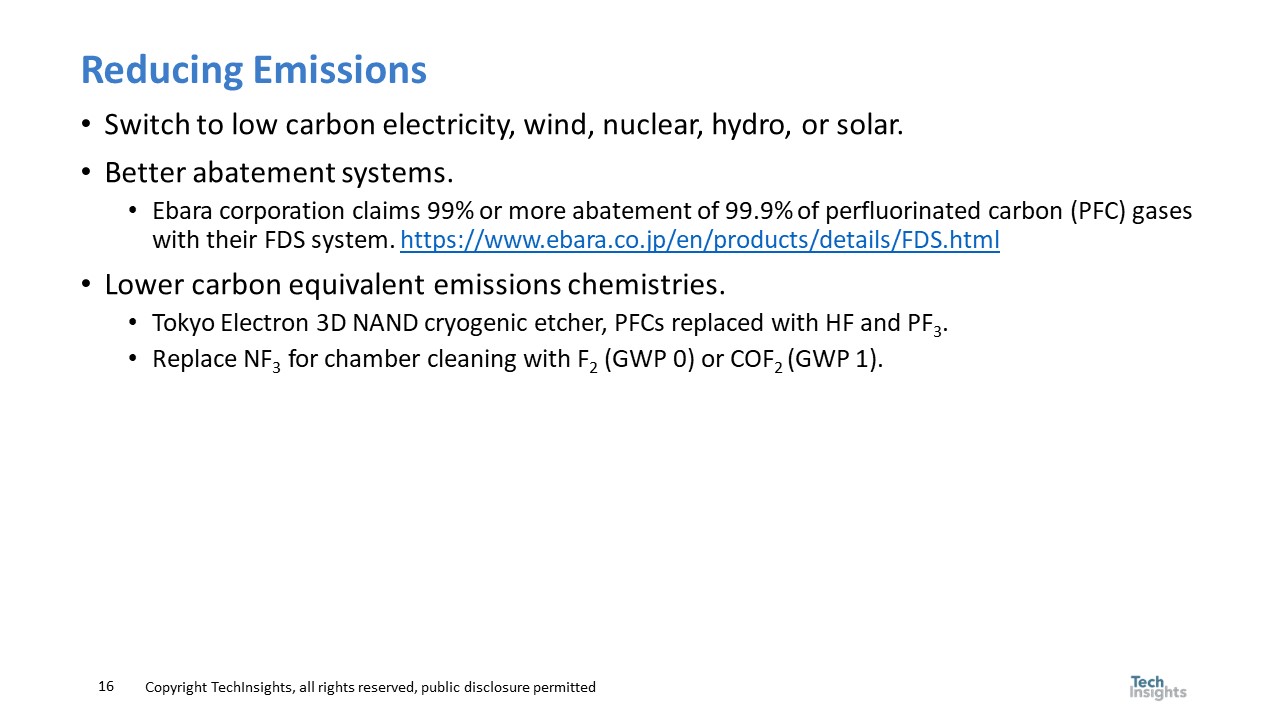

Figuur 13 presenteert enkele opties om de emissies te verminderen.

Elektriciteitsbronnen zoals steenkool produceren 820 gram CO2 equivalente uitstoot per kilowattuur (gCO2e/kWh), terwijl zonne-, waterkracht-, wind- en kernenergie respectievelijk 48, 24, 12 en 12 gCO2e/kWh produceren.

Efficiëntere bestrijdingssystemen kunnen procesgassen effectiever afbreken. De efficiëntie van het Fab-reductiesysteem varieert van 0% voor sommige gerapporteerde Amerikaanse locaties (geen reductie) tot ~90%. We schatten dat het wereldwijde gemiddelde van 300 mm-fabrieken ~70% bedraagt en dat voor de meeste 200 mm- en kleinere wafelfabrieken geen korting geldt. Er zijn systemen beschikbaar met een rendement tot 99%.

Chemie met lagere emissies kan ook worden gebruikt. Tokyo Electron heeft een nieuwe etstool voor 3D NAND aangekondigd die gassen met nul GWP gebruikt. Gassen zoals SF6 en NF3 worden voornamelijk gebruikt om fluor (F) in kamers te brengen voor reiniging, ter vervanging van F2 (GWP 0) of COF2 (GWP 1) kan deze emissiebron grotendeels elimineren.

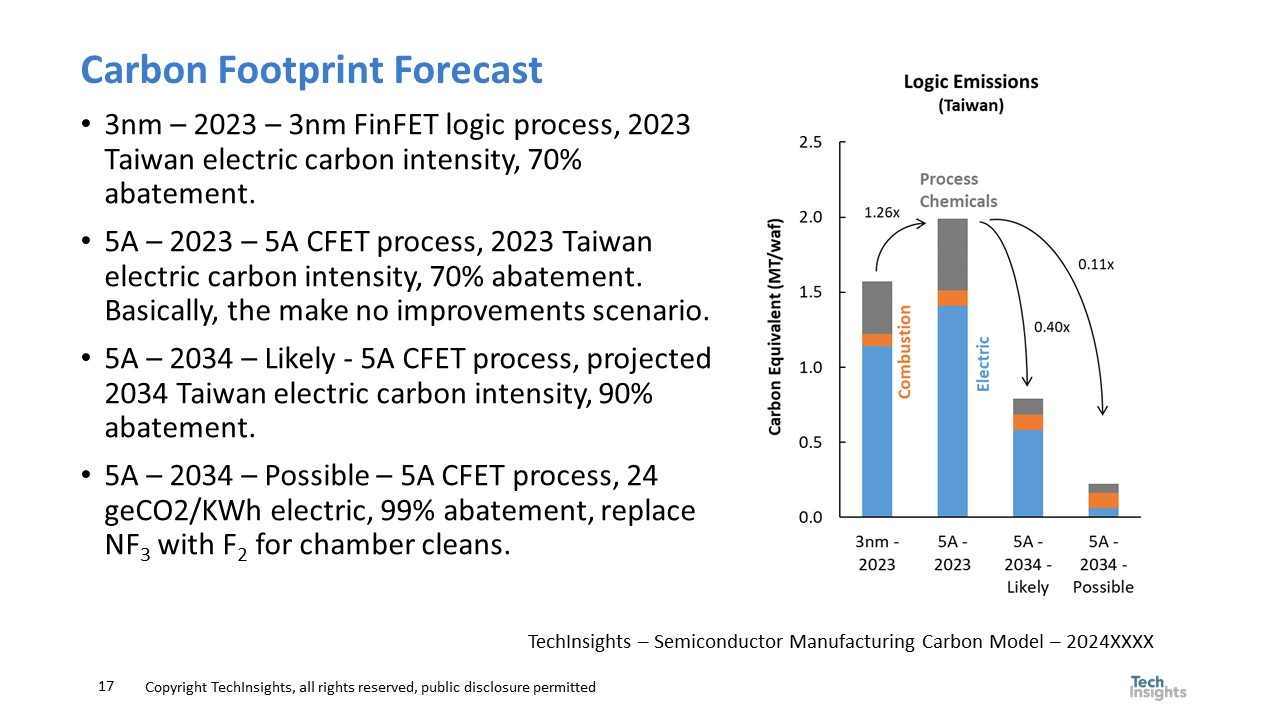

Figuur 14 illustreert een voorspelling van de COXNUMX-voetafdruk voor logica.

In de figuur is de eerste balk aan de linkerkant een 3nm-proces dat in 2023 in Taiwan wordt uitgevoerd, waarbij wordt uitgegaan van de CO70-voetafdruk van Taiwan op elektriciteitsgebied en een reductie van 5%. De tweede balk is een 2023A-proces en de uitstoot die zou ontstaan als dezelfde koolstofintensiteit voor elektriciteit in 70 en een reductie van 1.26% zouden worden gebruikt. De toename van de procescomplexiteit zou de totale voetafdruk met 2034x vergroten. Vooruitkijkend naar 90 wordt verwacht dat de elektriciteitsvoorziening in Taiwan aanzienlijk koolstofarm zal worden. Ook zou een reductie van 5% gebruikelijk moeten zijn, en de derde balk laat zien hoe een 2034A-proces er onder deze omstandigheden uit zou zien. Hoewel dit neerkomt op een reductie van de uitstoot met meer dan de helft, zou de groei van het aantal wafers dat door de industrie in 99 wordt beheerd deze verbetering waarschijnlijk overweldigen. De laatste balk aan de rechterkant is wat mogelijk is met voldoende investeringen, het is gebaseerd op koolstofarme elektriciteit, reductie van XNUMX% en het gebruik van F2 voor kamerreiniging.

Figuur 15 presenteert onze conclusies:

Transistordichtheid en wafer- en chipkostenschattingen werden gegenereerd met behulp van het TechInsights Strategic Cost and Price Model, een routekaart voor de sector die kosten- en prijsschattingen produceert, evenals gedetailleerde apparatuur- en materiaalvereisten. De schattingen van de broeikasgasemissies zijn gemaakt met behulp van het TechInsights Semiconductor Manufacturing Carbon Model. Neem voor meer informatie contact op met sales@techinsights.com

Ik wil graag mijn collega's van de Reverse Engineering Business Unit van TechInsights bedanken; hun digitale plattegrond en procesrapporten waren zeer nuttig bij het maken van deze presentatie. Ook Alexandra Noguera van TechInsights voor het extraheren van I/O-transistorgroottegegevens voor dit werk.

Lees ook:

IEDM 2023 – Modellering van de koolstofemissies van Wafer Fab van 300 mm

SMIC N+2 in Huawei Mate Pro 60

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/semiconductor-manufacturers/342094-iss-2024-logic-2034-technology-economics-and-sustainability/