Ik ben verheugd om mijn technische inzichten in RISC-V in dit artikel te delen om de volgende generatie chipontwerpers te inspireren en voor te bereiden op de toekomst van het open tijdperk van computers. Als je begrijpt hoe we complexe elektronische apparaten zoals desktops en smartphones bouwen met behulp van processors, zou je meer geïnteresseerd zijn in het leren en verkennen van de instructieset-architecturen.

Meestal geven we de voorkeur aan Complex Instruction Set Computer, CISC voor desktops/laptops, en Reduced Instruction Set Computer, RISC voor smartphones. De OEM's zoals Dell en Apple gebruiken x86 CISC-processor voor hun laptops. Laat me hier de benadering van het laptopontwerp uitleggen. Het moederbord heeft een multicore CISC-processor als hoofdcomponent, die is verbonden met GPU's, RAM, opslaggeheugen en andere subsystemen en I/O-interfaces. Het besturingssysteem voert meerdere applicaties parallel uit op de multicore-processor en beheert de geheugentoewijzing en I/O-bewerkingen.

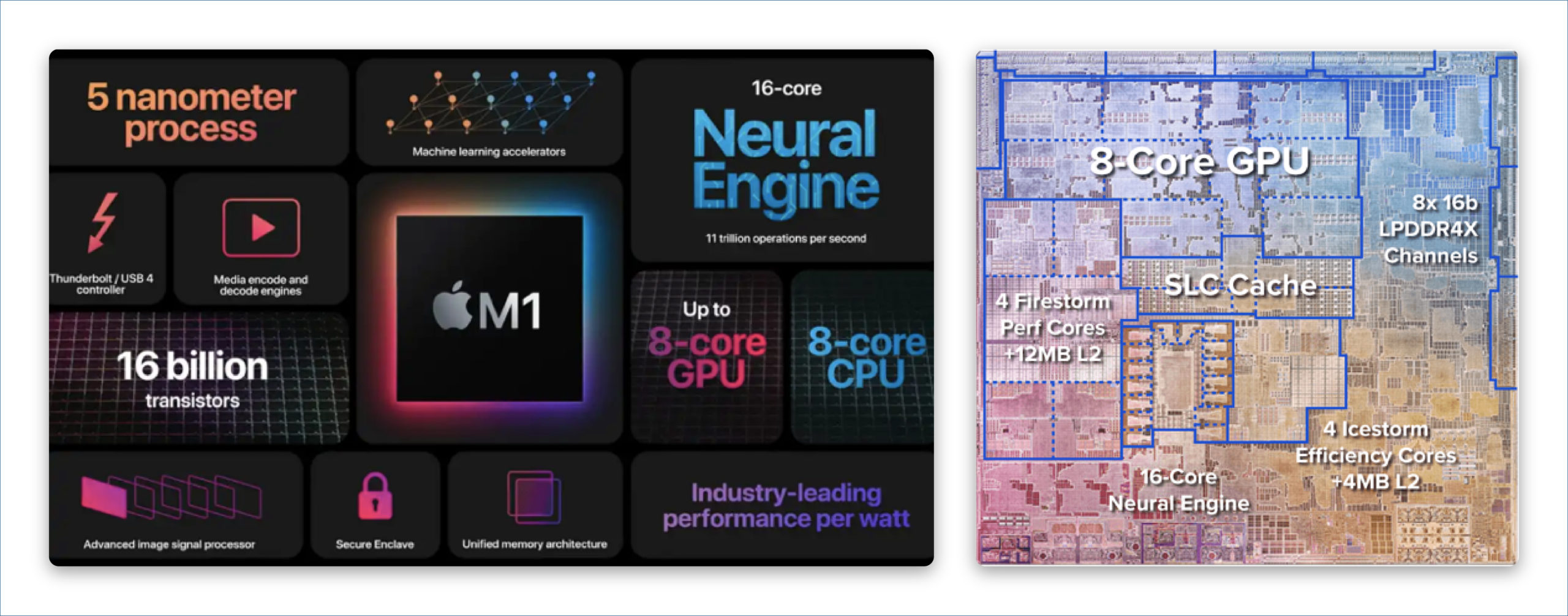

Zo kunnen we elk elektronisch systeem realiseren met behulp van een processor. We geven echter de voorkeur aan System-On-a-Chip met een RISC-processor voor smartphones, omdat dit ons helpt de grootte en het stroomverbruik van het moederbord te verminderen. Bijna het hele systeem met multi-core RISC CPU's, GPU's, DSP's, draadloze en interface-subsystemen, SRAM's, Flash-geheugens en IP's is geïmplementeerd op een SoC. De OEM Apple volgt de SoC-ontwerpbenadering van deze smartphone zelfs voor hun MAC-boeken als OEM-trendsetter. Alle nieuwste MAC-boeken gebruiken hun SoC's uit de M-serie die de RISC-processor van ARM gebruiken.

Het is dus duidelijk dat de gepatenteerde ISA's Intel's x86- of ARM's RISC-processors de keuze zijn geweest van OEM's zoals Apple, Dell, Samsung en anderen, maar nu waarom hebben we een open ISA zoals RISC-V nodig naast al deze beproefde propriëtaire ISA's.

In de huidige situatie gebruikt iedereen SoC's voor hun laptops en smartphones. Dit soort complexe SoC vereist zowel algemene als gespecialiseerde processors. Om chips zoals Apple's M-serie SoC's te realiseren, hebben we verschillende soorten processors nodig, zoals RISC CPU's, GPU's, DSP's, beveiligingsprocessors, beeldprocessors, machine learning-versnellers, beveiliging en neurale motoren, gebaseerd op verschillende algemene en gespecialiseerde ISA's van meerdere IP-adressen. leveranciers, zoals weergegeven in figuur 1.

In dit scenario zouden de belangrijkste uitdagingen zijn:

- Kiezen voor en werken met meerdere IP-leveranciers

- Verschillende IP-leveranciers kunnen verschillende IP-licentieschema's hebben en de technici hebben niet de vrijheid om de ISA's en het ontwerp aan te passen aan hun eigen ontwerpdoelen.

- Alle gespecialiseerde ISA's zullen niet lang meegaan, wat gevolgen heeft voor de productondersteuningsplannen en roadmaps voor de lange termijn.

- Ook de ontwikkeling van software/applicaties en updates waarbij meerdere ISA's en toolchains betrokken zijn, zou een uitdaging zijn.

RISC-V is een licentievrije open ISA voor algemeen gebruik met meerdere extensies. Het is een ISA die is opgedeeld in een ISA met een klein geheel getal, bruikbaar als basis voor op maat gemaakte versnellers en optionele standaarduitbreidingen ter ondersteuning van algemene softwareontwikkeling.

U kunt uw eigen extensies toevoegen om uw gespecialiseerde processor te realiseren of indien nodig de basis-ISA aanpassen omdat deze open is. Geen licentiebeperkingen. Dus in de toekomst zouden we alle algemene en gespecialiseerde processors kunnen creëren met slechts één RISC-V ISA en elke complexe SoC kunnen realiseren.

1. Wat is RISC-V en waarin verschilt het van andere ISA's?

RISC-V is een vijfde belangrijk ISA-ontwerp van UC Berkeley. Het is een open ISA die wordt onderhouden door een non-profitorganisatie, RISC-V international, waarbij alle belanghebbenden betrokken zijn bij het implementeren en onderhouden van de ISA-specificaties, gouden referentiemodellen en compliance-testsuites.

RISC-V is geen CPU-implementatie. Het is een open ISA voor zowel algemene als gespecialiseerde verwerkers. EEN volledig open ISA die vrij beschikbaar is naar de academische wereld en de industrie

RISC-V ISA is opgedeeld in een ISA met een klein geheel getal, die op zichzelf kan worden gebruikt als basis voor op maat gemaakte versnellers of educatieve doeleinden, en optionele standaarduitbreidingen ter ondersteuning van algemene softwareontwikkeling

RISC-V ondersteunt zowel 32-bits als 64-bits adresruimtevarianten voor applicaties, kernels van besturingssystemen en hardware-implementaties. Het is dus geschikt voor alle computersystemen, van ingebedde microcontrollers tot cloudservers, zoals hieronder vermeld.

Eenvoudige ingebedde microcontrollers

Beveilig ingebedde systemen die RTOS uitvoeren

Desktops/laptops/smartphones met besturingssystemen

Cloudservers waarop meerdere besturingssystemen worden uitgevoerd

2. RISC-V Basis ISA

RISC-V is een familie van verwante ISA's: RV32I, RV32E, RV64I, RV128I

Wat RV32I/ RV32E/ RV64I/RV128I betekent:

Camper – RISC-V

32/64/128 – Definieert de registerbreedte [XLEN] en adresruimte

I - Integer Basis ISA

32 Registreert voor alle basis-ISA's

E – Embedded: Base ISA met slechts 16 registers

2.1 RISC-V-registers:

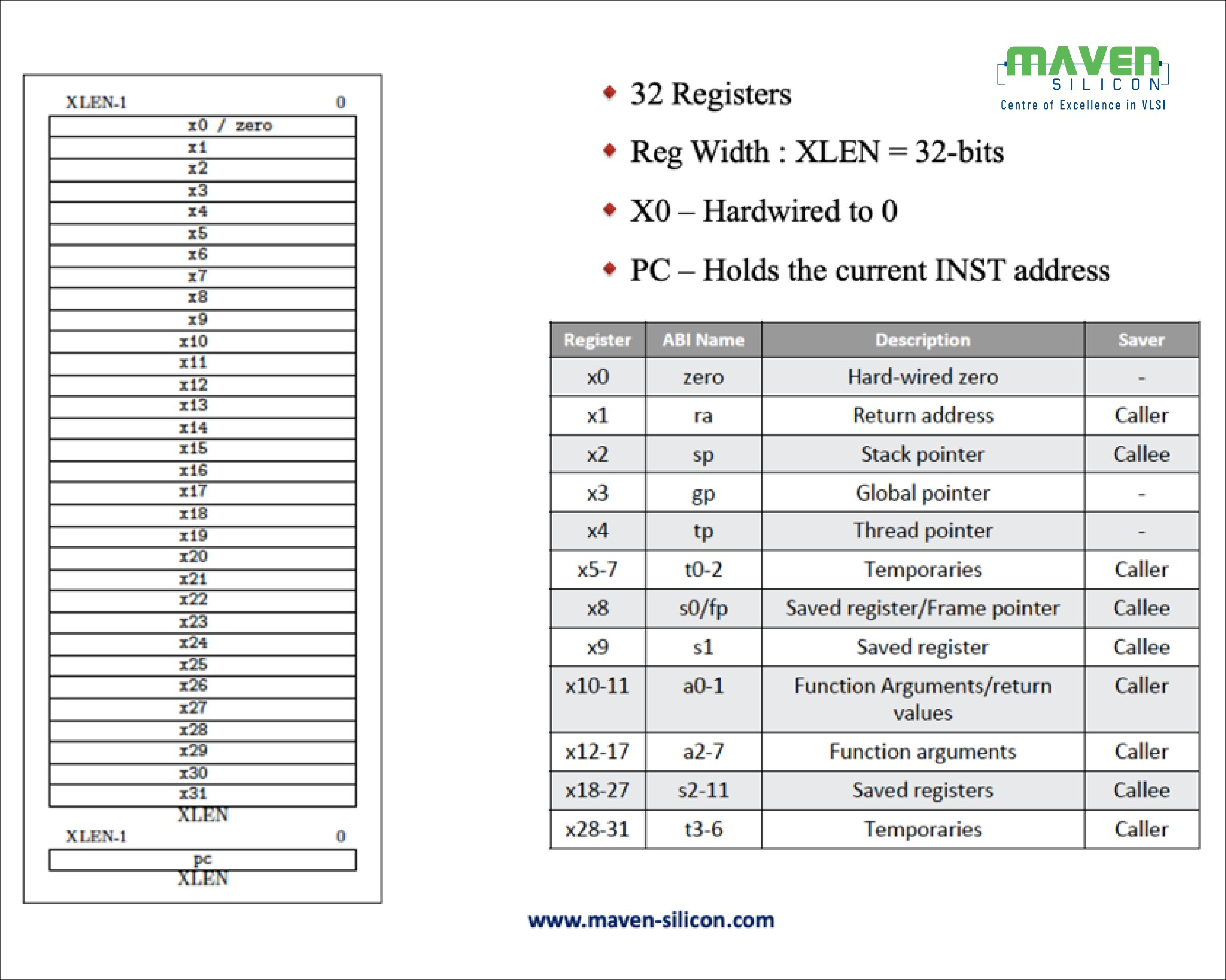

Alle basis-ISA's hebben 32 registers, zoals weergegeven in figuur 2, behalve RV32E. Alleen RV32E-basis-ISA heeft slechts 16 registers voor eenvoudige ingebedde microcontrollers, maar de registerbreedte is nog steeds 32 bits.

Het register X0 is bedraad op nul. Het speciale register, Program Counter genaamd, bevat het adres van de huidige instructie die uit het geheugen moet worden opgehaald.

Zoals weergegeven in figuur 2, RISC-V Application Binary Interface, definieert ABI standaardfuncties voor registers. De tools voor softwareontwikkeling gebruiken meestal ABI-namen voor eenvoud en consistentie. Volgens de ABI zijn extra registers gereserveerd voor opgeslagen registers, functieargumenten en tijdelijke functies in het bereik X0 tot X15, voornamelijk voor RV32E-basis-ISA, die alleen de top 16 registers nodig heeft voor het realiseren van eenvoudige ingebedde microcontrollers. Maar de RV32I-basis-ISA heeft alle 32 registers X0 tot X31.

2.2 RISC-V-geheugen:

Een RISC-V hart [Hardware Thread / Core] heeft een enkele byte adresseerbare adresruimte van 2^XLEN bytes voor alle geheugentoegangen. XLEN om te verwijzen naar de breedte van een integer register in bits: 32/64/128.

Woord van geheugen wordt gedefinieerd als 32 bits (4 bytes). Dienovereenkomstig is een halfwoord 16 bits (2 bytes), een dubbelwoord 64 bits (8 bytes) en een quadwoord 128 bits (16 bytes).

De geheugenadresruimte is cirkelvormig, zodat de byte op adres 2^XLEN −1 grenst aan de byte op adres nul. Dienovereenkomstig negeren geheugenadresberekeningen die door de hardware worden uitgevoerd overflow en wikkelen zich in plaats daarvan rond modulo 2 ^ XLEN.

RISC-V-basis-ISA's hebben little-endian- of big-endian-geheugensystemen, waarbij de geprivilegieerde architectuur de werking van big-endian verder definieert. Instructies worden in het geheugen opgeslagen als een reeks 16-bits little-endian-pakketten, ongeacht de endianiteit van het geheugensysteem.

2.3 RISC-V Load-Store-architectuur

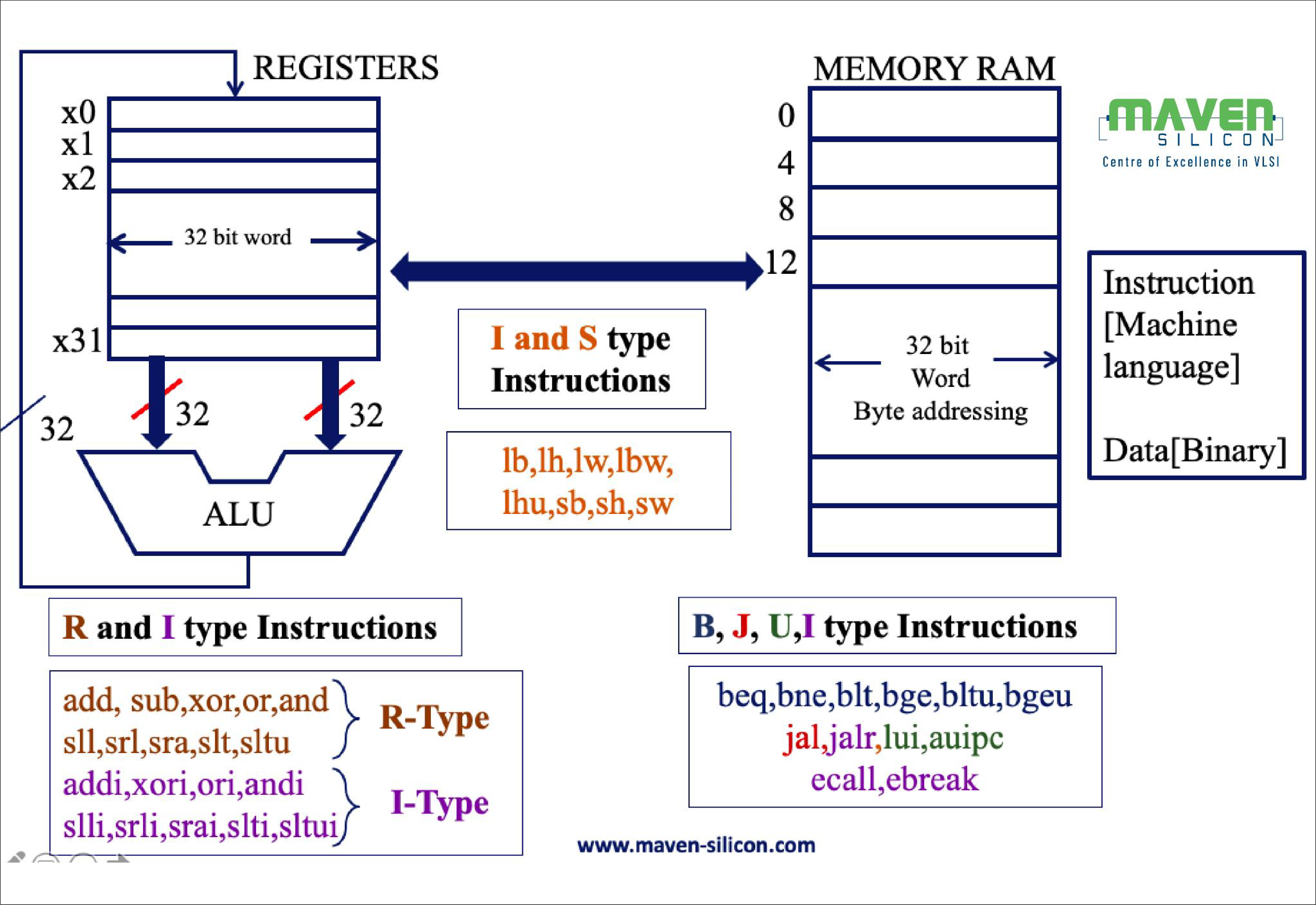

U kunt de RISC-V load-store-architectuur visualiseren die is gebaseerd op RISC-V-registers en geheugen, zoals hieronder weergegeven in figuur 3.

De RISC-V-processor haalt/laadt de instructie uit het hoofdgeheugen op basis van het adres in de pc, decodeert de 32-bits instructie en vervolgens voert de ALU rekenkundige/logische/geheugen-RW-bewerkingen uit. De resultaten van ALU zouden weer worden opgeslagen in de registers of het geheugen.

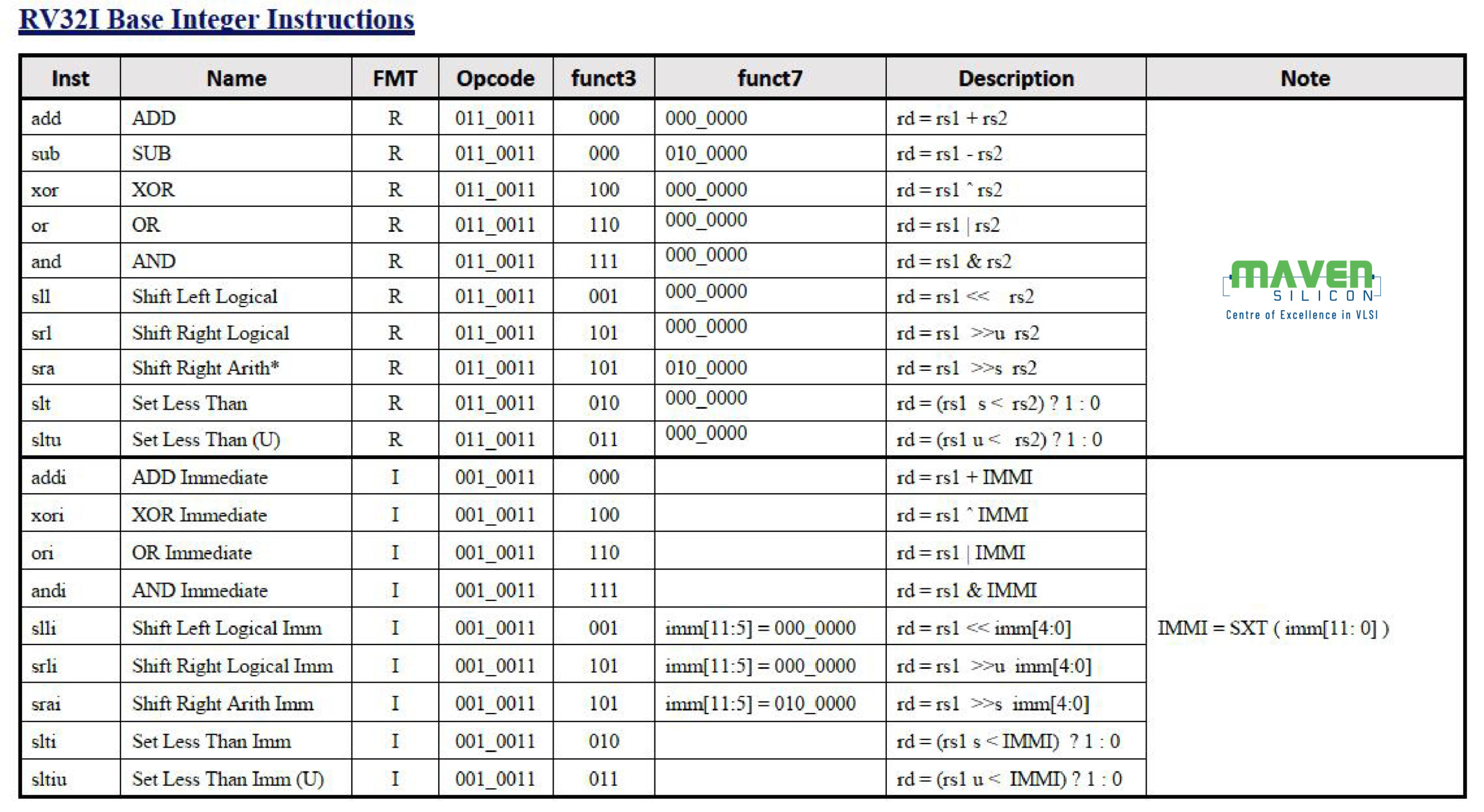

2.4 RISC-V RV32 I Basis-ISA:

RV32I base ISA heeft slechts 40 unieke instructies, maar een eenvoudige hardware-implementatie heeft slechts 38 instructies nodig. De RV32I-instructies kunnen worden geclassificeerd als:

R-Type: Registreer om instructies te registreren

I-Type: Direct registreren, Laden, JLR, Ecall & Ebreak

S-type: winkel

B-type: filiaal

J-Type: springen en koppelen

U-type: boven onmiddellijk laden/toevoegen

2.5 RISC-V ISA voor een geoptimaliseerd RTL Design:

Hier wil ik uitleggen hoe RISC-V ISA ons in staat stelt om een geoptimaliseerd Register Transfer Level-ontwerp te realiseren om te voldoen aan de low-power en high-performance doelen.

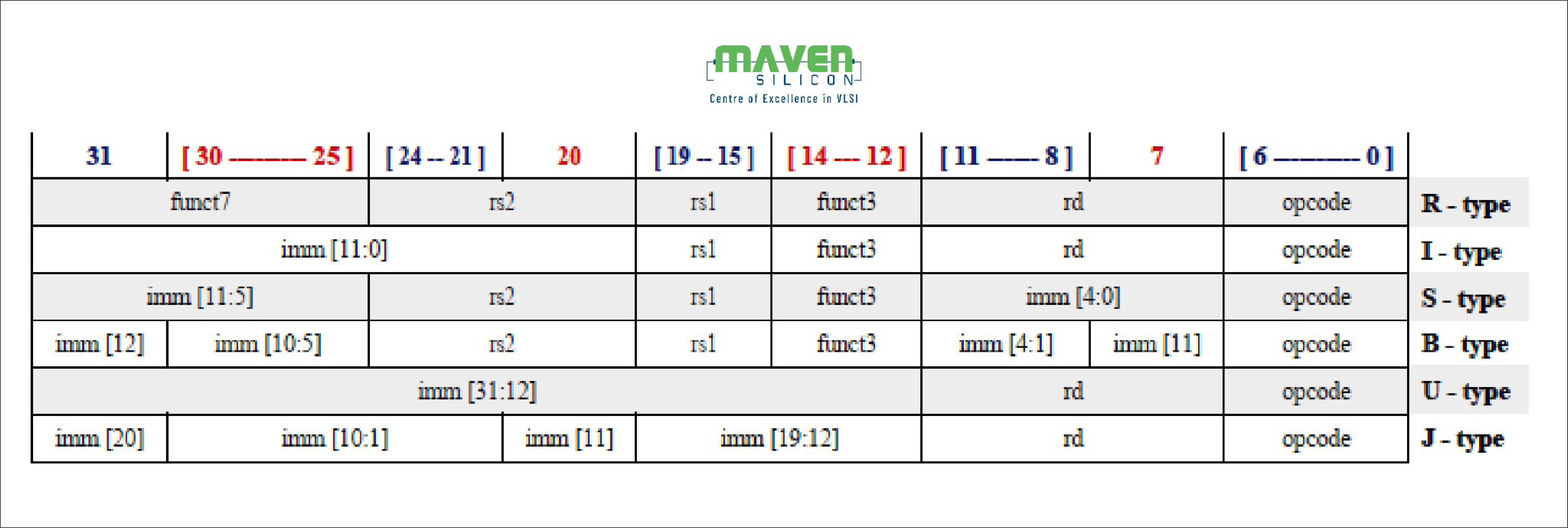

Zoals te zien is in figuur 4, houdt de RISC-V ISA de bron- (rs1 en rs2) en bestemmings- (rd) registers in alle formaten op dezelfde positie om het decoderen te vereenvoudigen.

Immediates zijn altijd teken-verlengd en zijn over het algemeen verpakt in de richting van de meest linkse beschikbare bits in de instructie en zijn toegewezen om de hardware-complexiteit te verminderen. Vooral,

het tekenbit voor alle onmiddellijke waarden bevindt zich altijd in bit 31 van de instructie om tekenuitbreidingsschakelingen te versnellen.

Sign-extension is een van de meest kritieke bewerkingen op directs (met name voor XLEN>32),

en in RISC-V wordt het tekenbit voor alle onmiddellijke waarden altijd vastgehouden in bit 31 van de instructie om toe te staan

tekenextensie om parallel te gaan met instructiedecodering.

Om het decoderen te versnellen, plaatst de basis RISC-V ISA de belangrijkste velden in elke instructie op dezelfde plaats. Zoals u kunt zien in de tabel met instructieformaten,

- De belangrijkste opcode is altijd in bits 0-6.

- Het bestemmingsregister, indien aanwezig, bevindt zich altijd in bits 7-11.

- Het eerste bronregister, indien aanwezig, bevindt zich altijd in bits 15-19.

- Het tweede bronregister, indien aanwezig, bevindt zich altijd in de bits 20-24.

Maar waarom worden de onmiddellijke bits geschud? Denk aan het fysieke circuit dat het directe veld decodeert. Omdat het een hardware-implementatie is, worden de bits parallel gedecodeerd; elk bit in de onmiddellijke uitvoer heeft een multiplexer om te selecteren van welk invoerbit het afkomstig is. Hoe groter de multiplexer, hoe duurder en langzamer hij is.

Het is ook interessant om op te merken dat alleen de hoofdopcode (bits 0-6) nodig is om te weten hoe de onmiddellijke code moet worden gedecodeerd, dus onmiddellijke decodering kan parallel aan het decoderen van de rest van de instructie worden uitgevoerd.

2.6 RV32I Base ISA-instructies

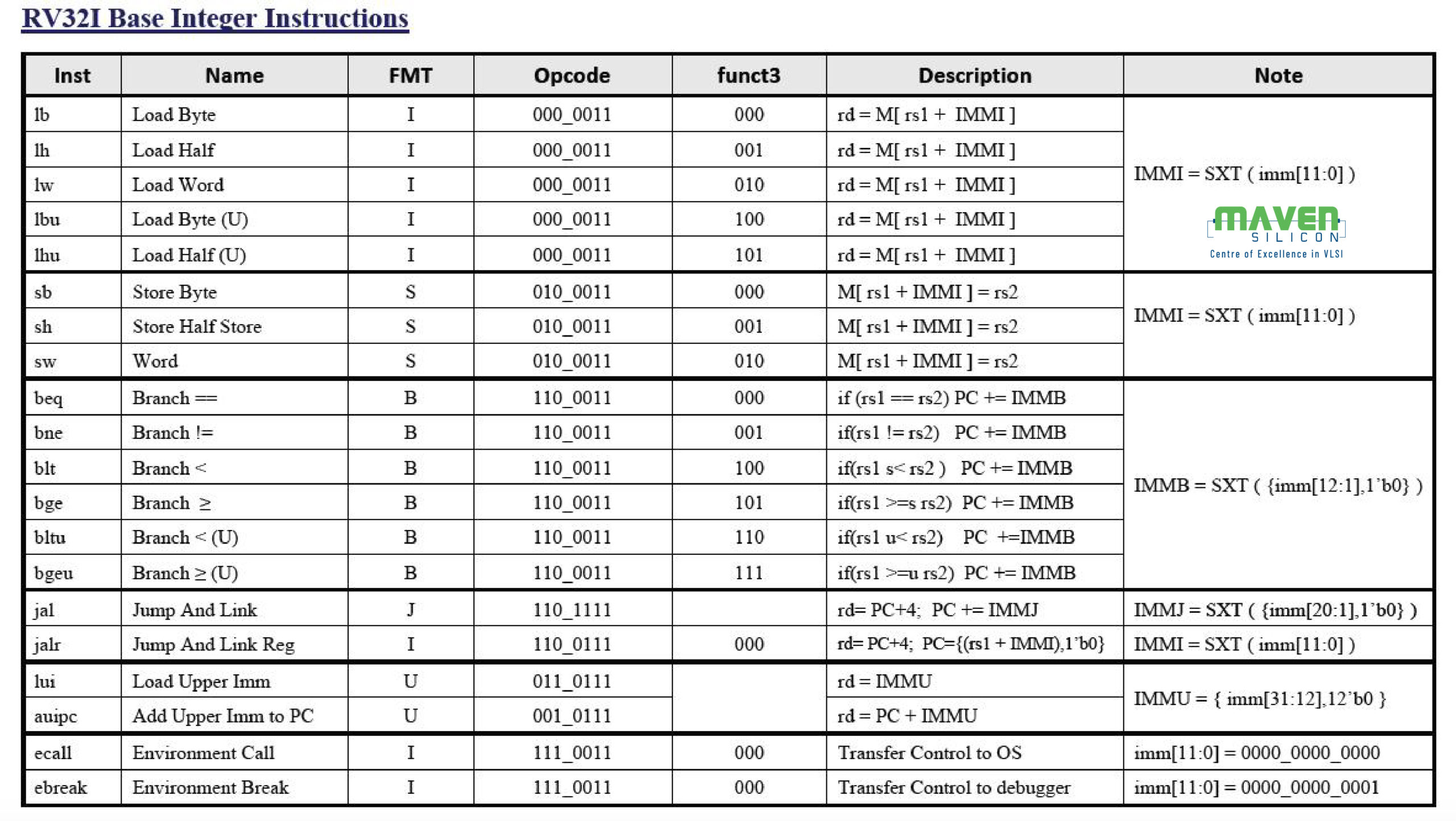

3. RISC-V ISA-extensies

Alle RISC-V ISA-extensies worden hier weergegeven:

We volgen de naamgevingsconventie voor RISC-V-processors, zoals hieronder wordt uitgelegd:

RISC-V-processoren: RV32I, RV32IMAC, RV64GC

RV32I: Integer Base ISA-implementatie

RV32IMAC: Integer Base ISA + Extensies: [Vermenigvuldigen + Atomic + Compressed]

RV64GC: 64bit IMAFDC [G-Algemeen doel: IMAFD]

Integer 64 bits Base ISA + Extensies: [Vermenigvuldigen + Atomic + SP Floating + DP Floating + Compressed]

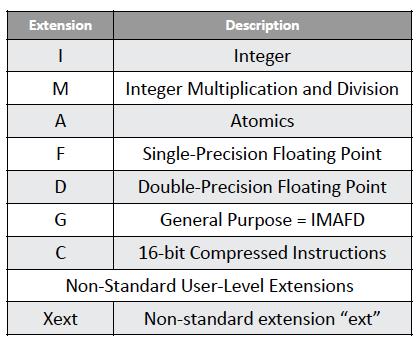

4. RISC-V bevoorrechte architectuur

RISC-V geprivilegieerde architectuur omvat alle aspecten van RISCV-systemen buiten de niet-geprivilegieerde ISA die ik tot nu toe heb uitgelegd. Bevoorrechte architectuur omvat bevoorrechte instructies en aanvullende functionaliteit die nodig is voor het uitvoeren van besturingssystemen en het aansluiten van externe apparaten.

Volgens de RISC-V bevoorrechte specificatie kunnen we verschillende soorten systemen realiseren, van eenvoudige embedded controllers tot complexe cloudservers, zoals hieronder wordt uitgelegd.

Applicatie-uitvoeringsomgeving – AEE: "Bare metal" hardwareplatforms waar harts direct worden geïmplementeerd door fysieke processorthreads en instructies hebben volledige toegang tot de fysieke adresruimte. Het hardwareplatform definieert een uitvoeringsomgeving die begint bij het opnieuw opstarten. Voorbeeld: eenvoudige en veilige ingebedde microcontrollers

Supervisor uitvoeringsomgeving – ZIE: RISC-V-besturingssystemen die meerdere uitvoeringsomgevingen op gebruikersniveau bieden door harten op gebruikersniveau te multiplexen op beschikbare fysieke processorthreads en door de toegang tot het geheugen te regelen via virtueel geheugen.

Voorbeeld: systemen zoals desktops met Unix-achtige besturingssystemen

Hypervisor-uitvoeringsomgeving – HEE: RISC-V-hypervisors die meerdere uitvoeringsomgevingen op supervisorniveau bieden voor gastbesturingssystemen.

Voorbeeld: cloudservers met meerdere gastbesturingssystemen

Ook definieert de RISC-V bevoorrechte specificatie verschillende controle- en statusregisters [CSR] om verschillende functies te implementeren, zoals interrupts, foutopsporing en geheugenbeheerfaciliteiten voor elk systeem. Misschien wilt u de specificatie raadplegen om meer te ontdekken.

Zoals in dit artikel wordt uitgelegd, kunnen we elk systeem efficiënt realiseren, van eenvoudige IoT-apparaten tot complexe smartphones en cloudservers, met behulp van een gemeenschappelijke open RISC-V ISA. Nu de schaling van monolithische halfgeleiders faalt, is specialisatie de enige manier om de rekenprestaties te verbeteren. De open RISC-V ISA is modulair en ondersteunt aangepaste instructies, waardoor het ideaal is voor het creëren van een breed scala aan gespecialiseerde processors en versnellers.

Aangezien we getuige zijn geweest van grote successen op het gebied van chipverificatie door de opkomst van de IEEE-standaard Universal Verification Methodology, zal de open RISC-V ISA ook naar voren komen als een industriestandaard ISA door alle goede eigenschappen van verschillende propriëtaire ISA's over te nemen en ons te leiden naar de toekomst van een open computertijdperk. Ben je klaar met RISC-V-expertise voor deze geweldige toekomst?

Auteur: PR Sivakumar, oprichter en CEO, Maven Silicon

LinkedIn profiel: https://www.linkedin.com/in/sivapr/

Lees ook:

CEO-interview: Sivakumar PR van Maven Silicon

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- Platoblockchain. Web3 Metaverse Intelligentie. Kennis versterkt. Toegang hier.

- Bron: https://semiwiki.com/semiconductor-services/maven-silicon/321555-is-your-career-at-risk-without-risc-v/