Bepalen of een 2.5D-apparaat een printplaat is die is verkleind om in een pakket te passen, of een chip die verder reikt dan de grenzen van een enkele chip, lijkt misschien een haarkloverij, maar kan aanzienlijke gevolgen hebben voor het algehele succes. van een ontwerp.

Planaire chips zijn altijd beperkt geweest door de grootte van het dradenkruis, namelijk ongeveer 858 mm2. Bovendien maken rendementsproblemen het silicium oneconomisch. Jarenlang heeft dit het aantal elementen beperkt dat op een vlak substraat kon worden gepropt. Eventuele extra functies zouden in extra chips moeten worden ontworpen en met een printplaat (PCB) moeten worden verbonden.

De komst van 2.5D De verpakkingstechnologie heeft een geheel nieuwe as voor expansie geopend, waardoor meerdere mogelijkheden mogelijk zijn chips met elkaar verbonden zijn binnen een geavanceerd pakket. Maar het uitgangspunt voor dit pakketontwerp kan een grote impact hebben op hoe de verschillende componenten worden geassembleerd, wie erbij betrokken is en welke tools wanneer worden ingezet.

Er zijn verschillende redenen waarom 2.5D tegenwoordig terrein wint. Eén daarvan is de kosten. “Als je kleinere chips of chiplets kunt bouwen, en die chiplets zijn ontworpen en geoptimaliseerd om in een pakket te worden geïntegreerd, kan het geheel kleiner worden”, zegt Tony Mastroianni, directeur geavanceerde verpakkingsoplossingen bij Siemens Digital Industries-software. “En omdat de opbrengst veel hoger is, heeft dat een dramatische impact op de kosten. In plaats van een rendement van 50% of minder voor die-sized chips, kun je dat verhogen tot in het bereik van 90%.”

Het onderling verbinden van chips met behulp van een PCB beperkt ook de prestaties. “Historisch gezien hadden we chips afzonderlijk verpakt en vervolgens op een PCB geplaatst en met elkaar verbonden via een bepaalde routing”, zegt Ramin Farjadrad, CEO en medeoprichter van Eliyan. “De problemen waarmee mensen te maken kregen waren tweeledig. Eén daarvan was dat de bandbreedte tussen deze chips werd beperkt door door de PCB te gaan en vervolgens door een beperkt aantal balletjes op de verpakking, waardoor de connectiviteit tussen deze chips werd beperkt.”

Het belangrijkste verschil met 2.5D vergeleken met een PCB is dat 2.5D chipafmetingen gebruikt. Er zijn veel fijnerkorrelige draden en verschillende componenten kunnen veel dichter bij elkaar worden verpakt op een tussenlaag of in een pakket dan op een bord. Om deze redenen kunnen draden korter zijn, kunnen er meer draden zijn en wordt de bandbreedte vergroot.

Dat heeft invloed op de prestaties op meerdere niveaus. “Omdat ze zo dichtbij zijn, heb je geen last van lange RC- of LC-vertragingen bij het transport, dus het gaat veel sneller”, zegt Mastroianni van Siemens. “Je hebt geen grote drivers op een chip nodig om lange sporen over het bord te rijden, dus je hebt minder kracht. U krijgt ordes van grootte betere prestaties – en een lager vermogen. Een veelgebruikte maatstaf is om te praten over picojoules per bit. De hoeveelheid energie die nodig is om bits te verplaatsen maakt 2.5D aantrekkelijk.”

Toch beïnvloedt de mentaliteit het oorspronkelijke ontwerpconcept, en dat heeft gevolgen voor de hele stroom. "Als je met een matrijsontwerper praat, zullen ze waarschijnlijk zeggen dat het maar een grote chip is", zegt John Park, productmanagementgroepdirecteur bij de Custom IC & PCB Group bij Cadans. "Maar als je met een pakketontwerper of een bordontwerper praat, zullen ze zeggen dat het eigenlijk een klein printje is."

Wie heeft er gelijk? “Vaak bepaalt de interne organisatiestructuur binnen het bedrijf hoe dit wordt aangepakt”, zegt Marc Swinnen, directeur productmarketing bij Ansys. “Op de langere termijn wil je er zeker van zijn dat je bedrijf zo is gestructureerd dat het aansluit bij de natuurkunde en niet probeert te passen bij de natuurkunde van jouw bedrijf.”

Wat duidelijk is, is dat niets zeker is. "De digitale wereld was heel regelmatig, in die zin dat we elke twee jaar een nieuw knooppunt kregen dat half zo groot was", zegt Cadence's Park. “Er zouden enkele nieuwe vereisten zijn, maar het was erg evolutionair. Verpakkingen zijn het Wilde Westen. Mogelijk krijgen we dit jaar acht nieuwe verpakkingstechnologieën, volgend jaar drie en volgend jaar twaalf. Een groot deel hiervan is afkomstig van de gieterijen, terwijl dit vroeger alleen afkomstig was van de uitbestede halfgeleiderassemblage- en testbedrijven (OSAT's) en de substraatleveranciers. Terwijl de gieterijen een nieuwkomer zijn, bieden de OSAT's een aantal echt interessante verpakkingstechnologieën aan tegen lagere kosten.”

Een deel van de reden hiervoor is dat verschillende groepen mensen verschillende eisen stellen. “De regering en het leger zien de voornaamste voordelen als heterogene integratiemogelijkheden”, zegt Swinnen van Ansys. “Ze verleggen niet de grenzen van de verwerkingstechnologie. In plaats daarvan ontwerpen ze zaken als monolithische microgolf-geïntegreerde schakelingen (MMIC's), waarbij ze golfgeleiders nodig hebben voor signalen met zeer hoge snelheid. Ze benaderen het vanuit het oogpunt van verpakkingsassemblage. Omgekeerd benaderen de high-performance compute (HPC)-bedrijven het vanuit een stapel 5nm- en 3nm-chips met hoogwaardig high-bandwidth memory (HBM). Ze zien het als een probleem met de assemblage van silicium. Het voordeel dat ze zien is de flexibiliteit van de architectuur, waar ze kernen en interfaces in kunnen stoppen en producten voor specifieke markten kunnen creëren zonder elke chiplet opnieuw te hoeven ontwerpen. Zij zien flexibiliteit als voordeel. Het leger ziet heterogene integratie als het voordeel.”

Materialen

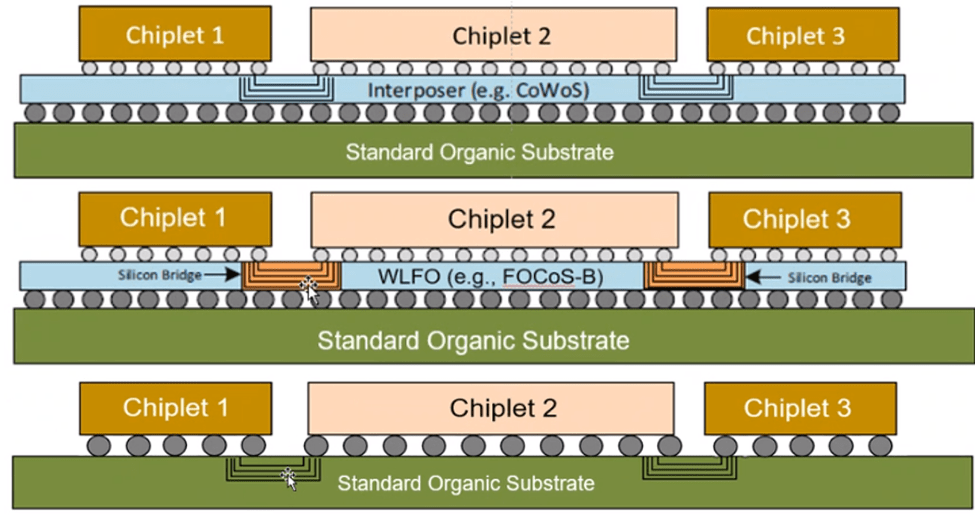

Er worden verschillende materialen gebruikt als substraat in de 2.5D-verpakkingstechnologie, die elk verschillende afwegingen hebben in termen van kosten, dichtheid en bandbreedte, en elk een selectie van verschillende fysieke problemen hebben die moeten worden overwonnen. Een van de belangrijkste differentiatiepunten is de bump pitch, zoals weergegeven in figuur 1.

Fig. 1. Chiplet-interconnectie voor verschillende substraatconfiguraties. Bron: Eliyan

Als we het hebben over een tussenvoegsel, wordt het over het algemeen als silicium beschouwd. "De interposer kan een groot stuk silicium zijn (Fig. 1 bovenaan), of gewoon siliciumbruggen tussen de chips (Fig. 1 midden) om voor de connectiviteit te zorgen", zegt Farjadrad van Eliyan. “Beide oplossingen maken gebruik van microbultjes met een hoge dichtheid. Tussenvoegsels en bruggen zorgen voor veel hobbels en sporen met hoge dichtheid, en dat geeft je bandbreedte. Als u 1,000 draden gebruikt die elk op 5 Gb draaien, krijgt u 5 Tb. Als je 10,000 hebt, krijg je 50Tb. Maar die signalen kunnen niet verder gaan dan twee of drie millimeter. Als alternatief, als u de siliciumtussenlaag vermijdt en bij een organisch pakket blijft (Fig. 1 onderaan), zoals een flip-chippakket, is de dichtheid van de sporen 5X tot 10X minder. De dikte van de draden kan echter 5x tot 10x groter zijn. Dat is een aanzienlijk voordeel, omdat de weerstand van de draden met het kwadraat van de dikte van de draden zal dalen. De dwarsdoorsnede van die draad gaat met het kwadraat van die draad omhoog, dus de weerstand daalt aanzienlijk. Als de dichtheid 5x zo laag is, betekent dit dat je signalen bijna 25x verder kunt doorgeven.”

Voor sommige mensen draait het allemaal om de bandbreedte per millimeter. “Als je een parallelle bus hebt, of een parallelle interface met hoge snelheid, en je wilt bandbreedte per millimeter, dan zou je waarschijnlijk voor een silicium-interposer kiezen”, zegt Kent Stahn, senior manager hardware engineering in Synopsys'Oplossingengroep. “Een organisch substraat is verliesarm en goedkoop, maar heeft niet de dichtheid. Daartussenin zijn er een aantal oplossingen die een deel daarvan waarmaken, maar niet voor dezelfde kosten.”

Er zijn ook andere redenen om voor een substraatmateriaal te kiezen. “De siliciuminterposer komt uit een gieterij, dus de beschikbaarheid is een probleem”, zegt Manuel Mota, senior productmanager personeel bij de Solutions Group van Synopsys. “Sommige bedrijven worden geconfronteerd met uitdagingen bij het sourcen van geavanceerde pakketten omdat er capaciteit wordt in beslag genomen. Door naar andere technologieën te gaan die iets minder bandbreedtedichtheid hebben, maar misschien wel voldoende voor jouw toepassing, kun je ze elders vinden. Dat wordt een cruciaal aspect.”

Al deze technologieën ontwikkelen zich echter snel. "De dradenkruislimiet is ongeveer 858 mm in het vierkant", zegt Park. “Mensen hebben het over interposers die misschien vier keer zo groot zijn, maar we hebben laminaten die veel groter zijn. Sommige laminaatsubstraten die uit Japan komen, benaderen hetzelfde niveau van verbindingsdichtheid dat we uit silicium kunnen halen. Persoonlijk zie ik meer beweging richting organische substraten. Chip-on-Wafer-on-Substrate (CoWoS) van TSMC maakt gebruik van een siliciuminterposer en is al ongeveer 12 jaar de technologie bij uitstek. Meer recentelijk introduceerden ze CoWoS-R, waarbij gebruik wordt gemaakt van filmpolyamide, dat dichter bij een organisch substraattype ligt. Nu horen we veel over glassubstraten.”

In de loop van de tijd kan het totale onroerend goed binnen het pakket groeien. “Het heeft geen zin dat gieterijen dingen blijven bouwen ter grootte van een printplaat van 30 inch”, voegt Park toe. “Er zijn materialen die geschikt zijn voor de grotere ontwerpen. Waar we echt dichtheid nodig hebben, is die-to-die. We willen die chiplets vlak naast elkaar, met een verbindingslengte van een paar millimeter. Wij willen het heel kort hebben. Maar de rest is alleen maar het uitwaaieren van de I/O, zodat deze verbinding maakt met de PCB.”

Dit is de reden waarom bruggen populair zijn. “We zien een vooruitgang naar bruggen voor het hogesnelheidsgedeelte van de interface”, zegt Stahn van Synopsys. “De achterkant ervan zou fanout zijn, zoals RDL fanout. We zien dat RDL-pakketten in de toekomst meer op traditionele pakketten gaan lijken.”

Interposers bieden extra mogelijkheden. “Tegenwoordig is 99% van de tussenpersonen passief”, zegt Park. “Er is geen front-end-of-line, er zijn geen apparaatlagen. Het is puur back-end-of-line-verwerking. Je voegt drie, vier, vijf metaallagen toe aan dat silicium. Dat noemen we een passieve interposer. Het creëert gewoon een die-tot-die-verbinding. Maar er zijn mensen die die dobbelsteen nemen en er een actieve tussenpersoon van maken, en daar in feite logica aan toevoegen.”

Dat kan voor verschillende doeleinden gebeuren. “Je ziet al dat sommige bedrijven actieve interposers gebruiken, waar ze energiebeheer of een deel van de bedieningslogica toevoegen”, zegt Mota. “Als je actieve circuits op de interposer gaat plaatsen, is het dan nog steeds een 2.5D-integratie of wordt het een 3D-integratie? We zien vandaag geen grote trend in de richting van actieve interposers.”

Er zijn echter enkele nieuwe problemen. "Je moet rekening houden met niet-overeenkomende thermische uitzettingscoëfficiënten (CTE), " zegt Stahn. “Dit gebeurt wanneer twee materialen met verschillende CTE’s aan elkaar worden gebonden. Laten we beginnen met de siliciumtussenlaag. Je kunt systemen met een hoger wattage krijgen, waarbij de SoC's met hun collega's kunnen praten, en dat kan veel stroom verbruiken. Een silicium interposer moet nog in een verpakking. De CTE-mismatches bevinden zich tussen het silicium en het verpakkingsmateriaal. En met de brug gebruik je hem waar je hem nodig hebt, maar het is nog steeds een silicium-die-to-die. Je moet de thermische mechanische analyse uitvoeren om er zeker van te zijn dat het vermogen dat je levert en de CTE-mismatches die je hebt, resulteren in een levensvatbaar systeem.”

Hoewel signaallengten in theorie langer kunnen worden, levert dit enkele problemen op. "Als je lange verbindingen in een chip maakt, beperk je die routes doorgaans tot een paar millimeter, en dan buffer je ze", zegt Mastroianni. “Het probleem met een passieve silicium-interposer is dat er geen buffers zijn. Dat kan echt een serieus probleem worden. Als u deze verbindingen toch moet maken, moet u deze zeer zorgvuldig plannen. En u moet er wel voor zorgen dat u een timinganalyse uitvoert. Normaal gesproken zullen uw pakketjongens die analyse niet uitvoeren. Dat is meer een probleem dat is opgelost met statische timinganalyse door siliciumingenieurs. We moeten een STA-stroom introduceren en alle extracties aanpakken die organische en siliciumachtige sporen bevatten, en het wordt een nieuw probleem. Wanneer u zich begint te verdiepen in enkele van die zeer lange sporen, houden uw eenvoudige RC-timingvertragingen, die worden aangenomen in normale STA-vertragingscalculators, geen rekening met een deel van de inductantie en wederzijdse inductie tussen die sporen, zodat u ernstige nauwkeurigheidsproblemen kunt krijgen voor die lange sporen.”

Actieve tussenpersonen helpen. “Met actieve interposers kun je een aantal langeafstandsproblemen oplossen door buffers of signaalversterkers aan te brengen”, zegt Swinnen. “Dan gaat het weer meer op een chip lijken, en dat kun je alleen op silicium doen. Je hebt de EMIB-technologie van Intel, waarbij ze een chiplet in de interposer hebben ingebed en dat is een actieve brug. De chip praat met de EMIB-chip, en ze praten allebei met je via deze kleine actieve bridge-chip, die niet bepaald een actieve interposer is, maar bijna als een actieve interposer fungeert.

Maar zelfs passieve componenten voegen waarde toe. “Het eerste dat wordt gedaan is het plaatsen van geulcondensatoren in de interposer”, zegt Mastroianni. “Dat geeft je de mogelijkheid om een goede ontkoppeling uit te voeren, waar het telt, dichtbij de dobbelsteen. Als je ze op het bord zet, verlies je veel van de voordelen van de hogesnelheidsinterfaces. Als je ze in de interposer kunt krijgen, precies onder de plek waar je de snel schakelende snelheidssignalen hebt, kun je een plaatselijke ontkoppeling krijgen.

Naast verschillende materialen is er de vraag wie de interposer ontwerpt. “De industrie lijkt het te zien als een kleine PCB in de context van wie het ontwerp doet”, zegt Matt Commens, senior manager productmanagement bij Ansys. “De interposers worden doorgaans ontworpen door verpakkingsingenieurs, ook al zijn het siliciumprocessen. Dit geldt vooral voor de high-performance exemplaren. Het lijkt contra-intuïtief, maar ze hebben die signaalintegriteitsachtergrond, ze hebben transmissielijnen ontworpen en de mismatch bij onderlinge verbindingen geminimaliseerd. Een traditionele IC-ontwerper werkt vanuit een component-oogpunt. De industrie vertelt ons dus zeker dat de mensen die ze het ontwerpwerk laten doen, een soort persona's zijn.”

Power

Er zijn enkele aanzienlijke verschillen in de routering tussen PCB's en interposers. “Interposer-routing is veel eenvoudiger, omdat het aantal componenten drastisch is verminderd in vergelijking met de PCB”, zegt Andy Heinig, afdelingshoofd voor efficiënte elektronica bij Fraunhofer IIS/EAS. “Aan de andere kant is het elektriciteitsnet op de interposer veel complexer vanwege de hogere weerstand van de metaallagen en het feit dat het elektriciteitsnet wordt onderbroken door signaaldraden. De routing voor de die-to-die-interface is complexer vanwege de routeringsdichtheid.”

De vermogensafgifte ziet er heel anders uit. "Als je naar een PCB kijkt, plaatsen ze grote metalen gietgebieden ingebed in de lagen, en maken ze gebieden leeg waar dingen doorheen moeten", zegt Park. 'Je legt een hoop koper neer en dan gooi je de andere weg. Op die manier kunnen we geen tussenpersoon bouwen. We moeten de verbinding aanbrengen, zodat de stroom- en aardingsstructuren op een siliciuminterposer meer op een digitale chip gaan lijken. Maar het signaal zal meer op een PCB- of laminaatpakket lijken.”

Routing lijkt meer op een PCB dan op een chip. "Je ziet dingen als tranen of filets waar het een verbinding maakt met een pad of via om een betere opbrengst te creëren", voegt Park toe. “De routeringsstijlen van vandaag zijn meer afgestemd op PCB's dan op een digitale IC, waar je alleen orthogonale hoeken van 90° en schone routeringskanalen hebt. Voor interposers, of het nu silicium of organisch is, is de via vaak groter dan de draad, wat een klassiek PCB-probleem is. Als we het over digitaal hebben, lijken de routers opnieuw meer op een kleine printplaat dan op een dobbelsteen.”

TSV's kunnen ook problemen veroorzaken. “Als je ze als vierkant gaat behandelen, verlies je veel ruimte op de hoeken”, zegt Swinnen. “Je wilt echt 45° rondom die objecten. Siliciumrouters zijn traditioneel Manhattan, hoewel er een lange traditie bestaat van RDL-routering, de bovenste laag waar de hobbels met elkaar zijn verbonden. Traditioneel werden daarbij achthoekige of ronde hobbels gebruikt, en vervolgens een 45°-routering. Het is niet zo flexibel als de PCB-routering, maar ze hebben herverdelingslaagrouters, en ze hebben ook een aantal routers die van de volledig aangepaste kant komen en die volledige rivierroutering hebben.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/