RISC-V 움직임은 디자이너에게 제공되는 선택의 폭이 넓기 때문에 매우 빠르게 시작되었습니다. 그러나 엄청난 유연성은 그 자체로 문제를 야기합니다. 하나는 사양 범위 내에서 허용되는 잠재적인 마이크로아키텍처 변경을 통해 입증되지 않은 RISC-V 코어 설계를 분석, 최적화 및 검증하는 방법입니다. FPGA 기반 프로토타이핑 기술로 가장 잘 알려진 S2C는 #60DAC에서 새로운 체계적인 RISC-V 아키텍처 분석 및 최적화 전략에 대한 업데이트를 제공하고 모델링 및 에뮬레이션 기능을 추가했습니다.

RISC-V 아키텍처 분석의 XNUMX단계

RISC-V는 실행 장치 및 파이프라인 구성부터 사용자 정의 지침 추가에 이르기까지 사용자 정의가 가능한 정도에서 다른 프로세서 아키텍처와 다릅니다. 개발자들은 일부 정의가 여전히 모호한 많은 응용 분야에서 다양한 RISC-V 구성에 가장 적합한 구성을 모색하고 있습니다. EDA 지원은 아직 따라잡지 못했습니다. 기본 도구는 존재하지만 사용할 수 있는 고급 모델링 플랫폼은 거의 없습니다.

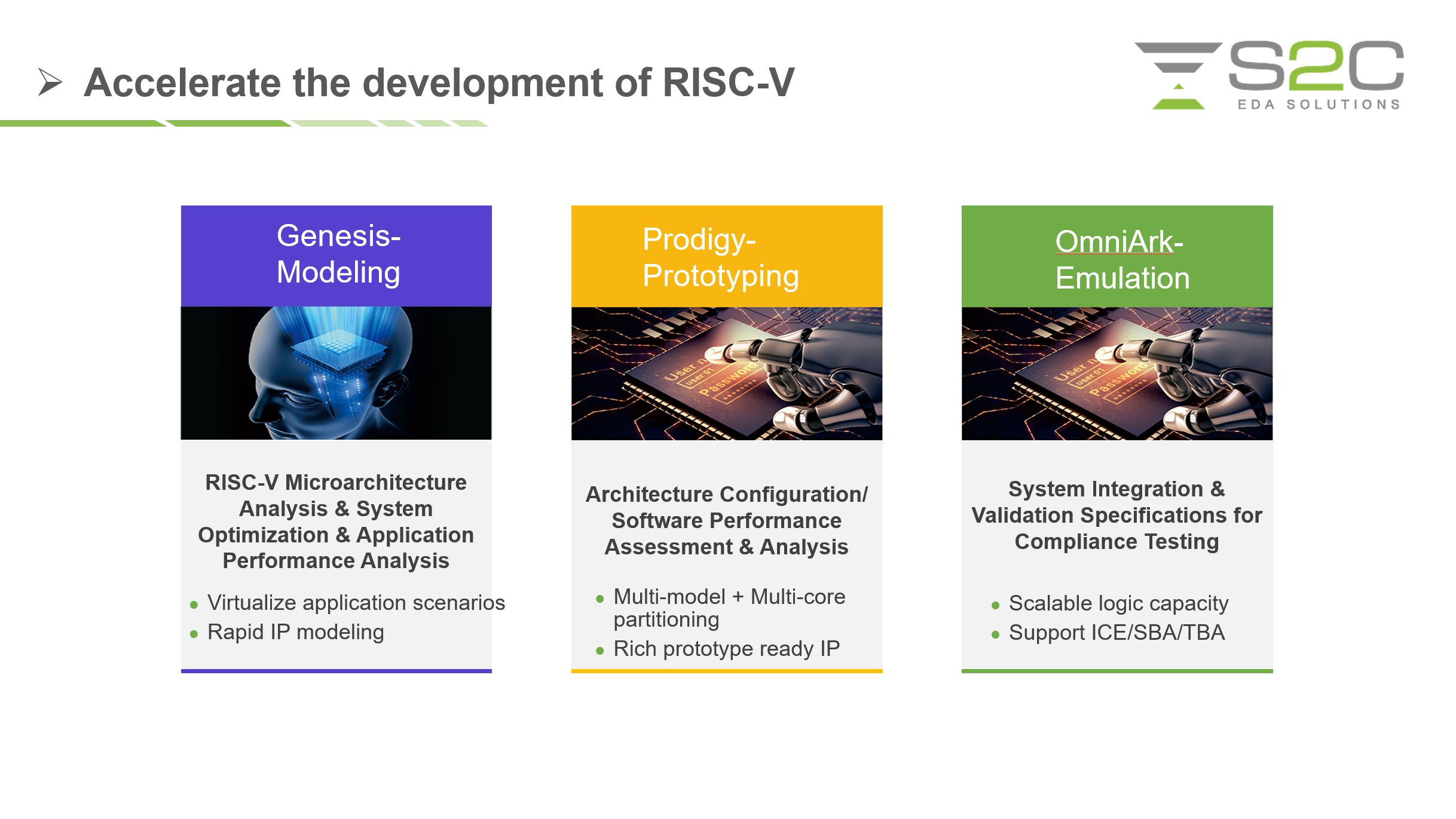

이러한 조건으로 인해 팀은 문제에 직면하게 됩니다. 구현을 위해 RISC-V 명령 세트를 확장하는 경우 시뮬레이션 또는 에뮬레이션된 성능을 평가하기 전에 해당 명령에 대한 새로운 주기 정확도 모델을 만들어야 합니다. S2C는 체계적인 RISC-V 아키텍처 분석 및 최적화를 위해 하나의 친숙한 기술과 다른 두 가지 기술을 갖춘 완전한 체인으로 이러한 공백을 메우기 위해 노력하고 있습니다.

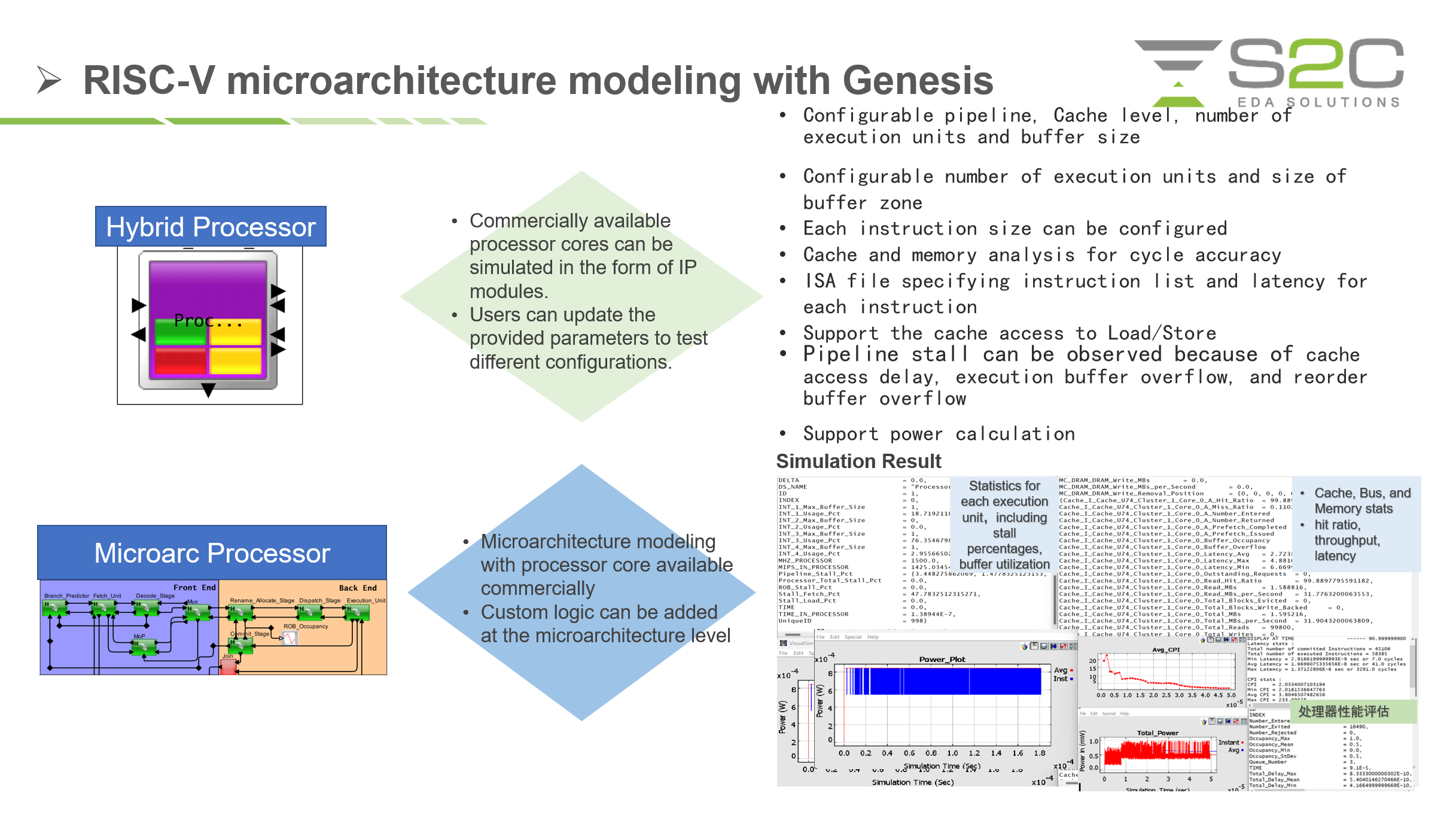

체인의 첫 번째는 S2C의 새로운 RISC-V "코어 마스터" 모델 추상화 플랫폼인 Genesis입니다. 이는 모델에 충실도가 추가됨에 따라 정확도가 높아지면서 확률론적 모델링, 시스템 아키텍처 모델링 및 정확한 주기 모델링을 제공합니다. Genesis를 사용하면 상용 RISC-V 코어를 IP 모듈로 시뮬레이션한 다음 매개변수를 업데이트하거나 마이크로아키텍처에 사용자 정의 로직을 추가할 수 있습니다. 이러한 시뮬레이션을 통해 코어의 조기 최적화가 가능해졌습니다.

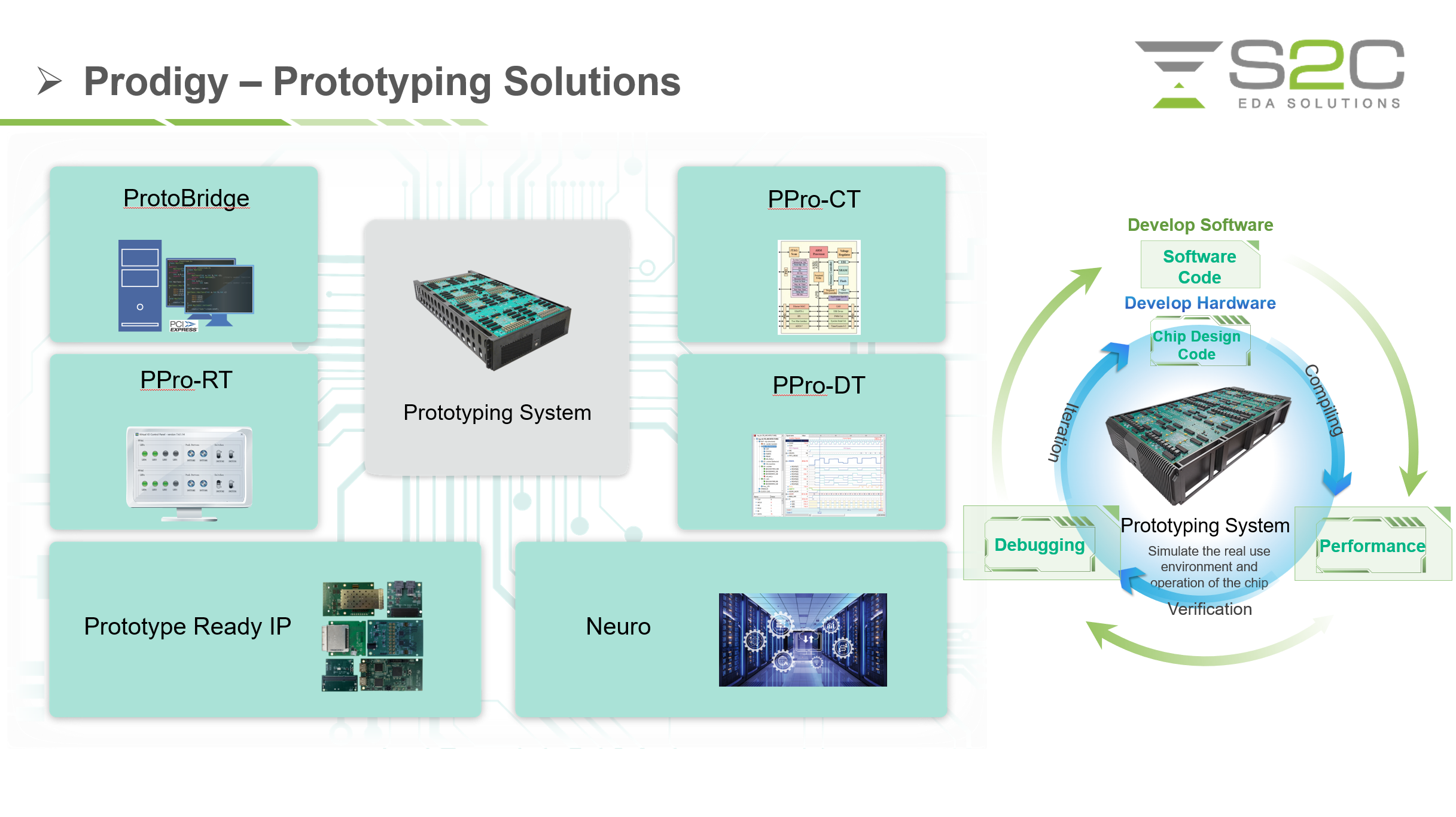

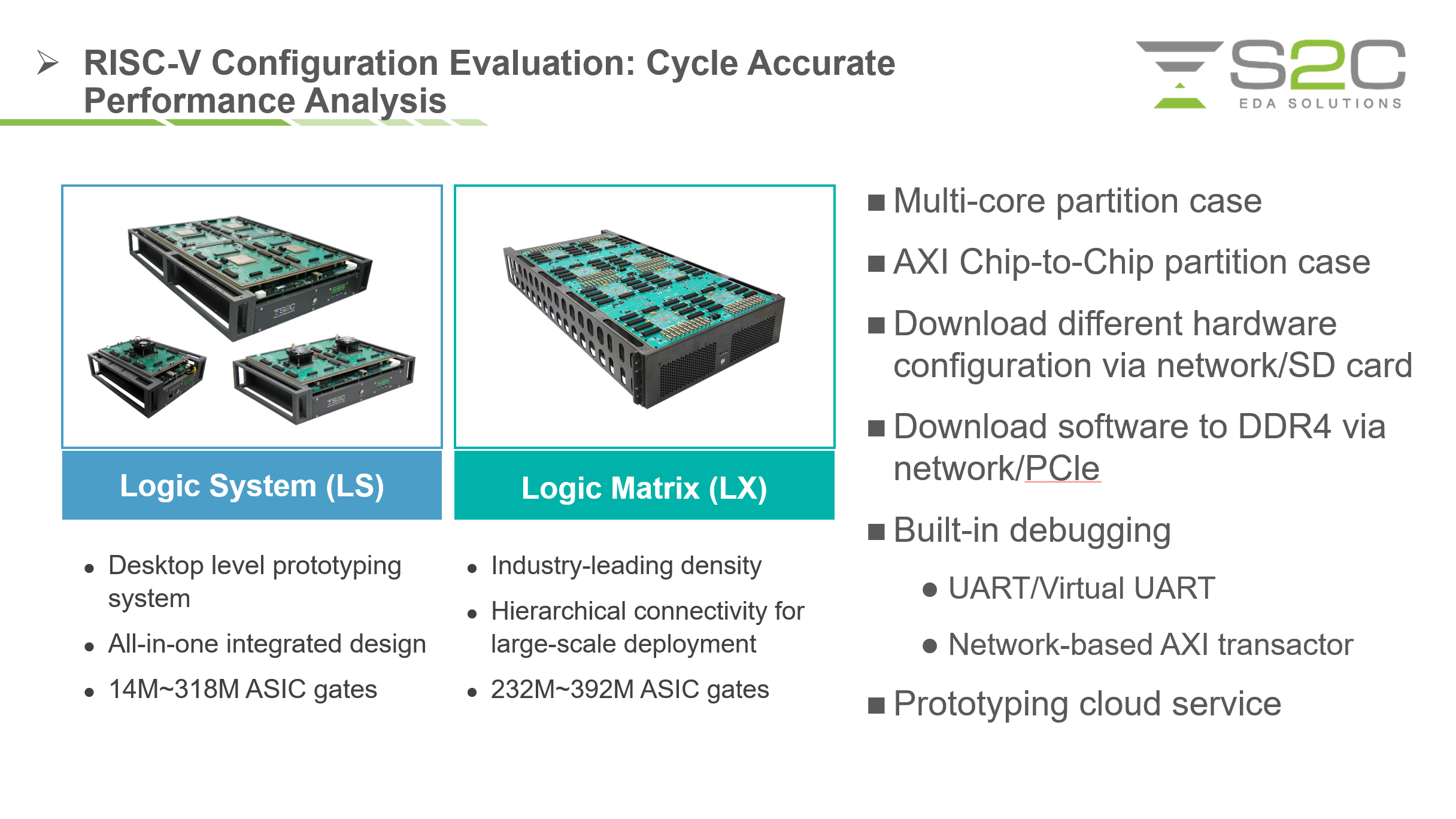

분석 체인의 중간을 차지하는 것은 S2C Prodigy 프로토타입 제품군으로, 하드웨어 로직 디버깅, 기본 성능 평가 및 초기 소프트웨어 개발을 위한 FPGA 기반 프로토타입을 촉진합니다. Prodigy 프로토타이핑 하드웨어는 SoC 주변의 실제 신호 자극 및 소비와 RISC-V IP 성능 검증을 위해 S2C에서 개발한 기성 I/O 모듈도 수용합니다.

새로운 에뮬레이션 기능은 RISC-V SoC의 대규모 검증이 가능한 S2C의 OmniArk 하이브리드 에뮬레이션 시스템과 함께 제공됩니다. OmniArk는 자동차 SoC 컴파일을 전문으로 하며 효율적인 검증 환경을 위한 강력한 디버깅 기능을 자랑합니다. 대규모 설계를 위해 최대 1억 개의 게이트까지 확장하고 QEMU, TBA, ICE와 같은 검증 모드를 지원합니다.

예: XiangShan RISC-V 핵심 프로젝트에 대한 협업

RISC-V 코어의 정확한 동작 모델은 초기 모델링, FPGA 기반 프로토타입 제작 및 하드웨어 에뮬레이션 프로세스를 통해 수행됩니다. 설계자에게 IP와 모델 모두에 대한 더 나은 제어 기능을 제공하면 하드웨어 프로토타입에서만 가능했던 작업이 설계 주기 초기에 가상 분석 활동으로 전환되어 최적화를 위한 더 많은 기회를 창출할 수 있습니다.

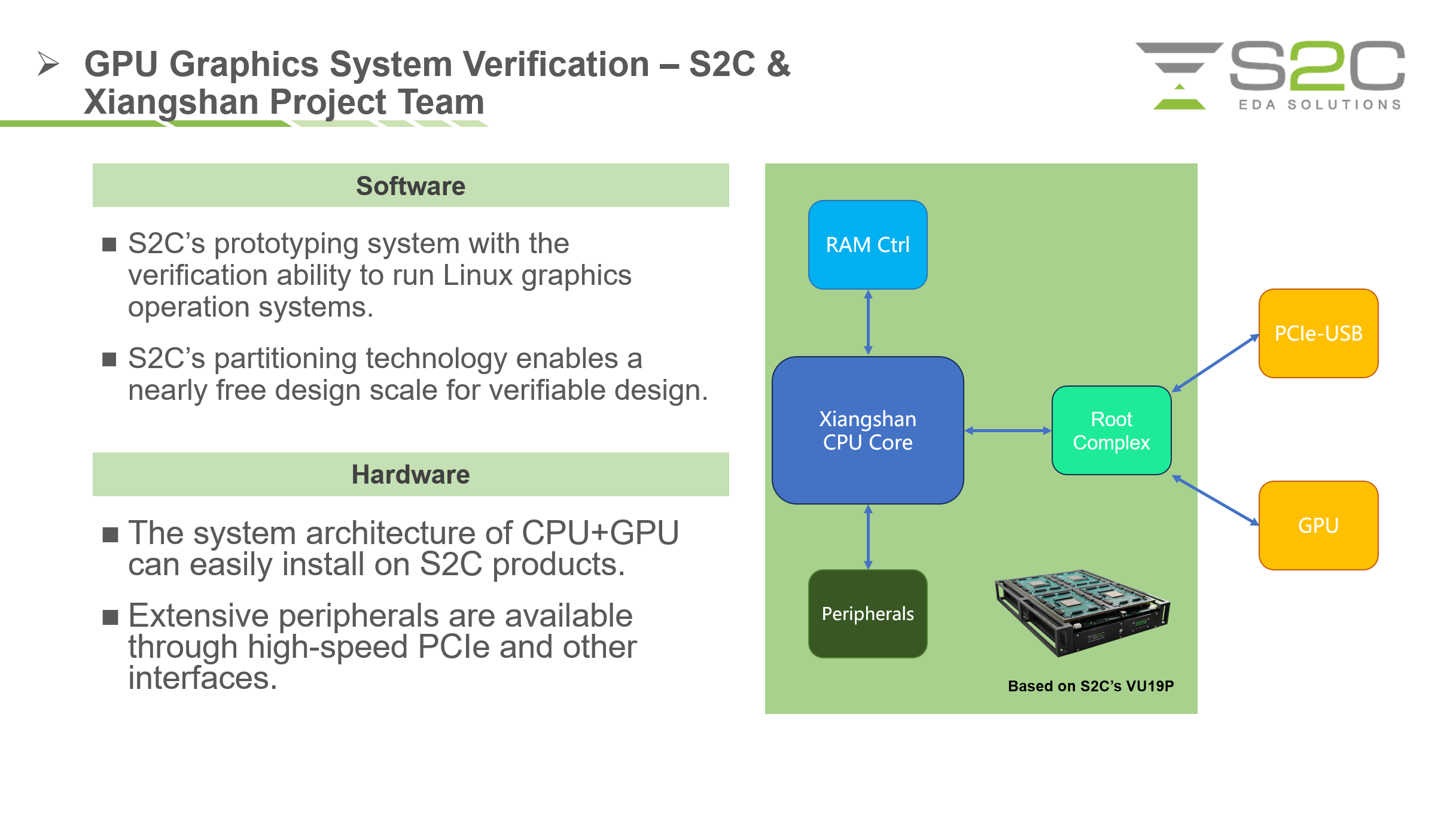

체계적인 RISC-V 아키텍처 분석 및 최적화의 예는 중국과학원(China Academy of Sciences)에 기반을 둔 XiangShan 프로젝트 팀과 S2C의 협력입니다. XiangShan은 운영 체제의 Linux 변형을 대상으로 하는 수퍼스칼라, XNUMX폭, 비순차적 RISC-V 구현입니다.

XiangShan 팀은 S2C 제품을 사용하여 외부 GPU 및 기타 주변 장치와 통합된 핵심 검증 플랫폼을 만들었습니다. 하이퍼스케일 코어는 PCIe 및 기타 인터페이스를 통해 주변 장치가 추가된 S2C FPGA 기반 프로토타이핑 플랫폼으로 분할됩니다.

S2C의 부사장인 Ying J. Chen은 "RISC-V 기술이 다양한 분야에 침투함에 따라 오픈 소스, 간결성 및 높은 확장성이 컴퓨팅의 미래를 재정의하고 있습니다."라고 말했습니다. “S2C의 XNUMX가지 주요 제품군은 RISC-V 기반의 마이크로아키텍처 분석, 시스템 통합, 사양 적합성 테스트를 위한 소프트웨어 성능 평가 등 다양한 솔루션을 제공할 수 있습니다.”

체계적인 RISC-V 아키텍처 분석 및 최적화 체인이 다가오는 미국 제품 발표와 어떻게 결합되는지에 대한 자세한 내용은 곧 S2C에서 나올 것으로 예상됩니다. 현재 S2C의 중국어 사이트에는 창세기에 대한 몇 가지 정보. XiangShan RISC-V 프로젝트에 대한 자세한 내용은 다음에서 확인할 수 있습니다. ASPLOS'23에서 제공된 튜토리얼.

또한 읽기 :

Sirius Wireless, 더 미세한 칩 설계를 위해 Wi-Fi2/BT RF IP 검증 시스템 기반 S6C와 파트너십 체결

S2C, Bluetooth LE 오디오 SoC 개발 일정 가속화

S2C는 고객이 고성능 보안 GPU 칩 검증을 달성하도록 지원합니다.

다음을 통해이 게시물 공유 :

- SEO 기반 콘텐츠 및 PR 배포. 오늘 증폭하십시오.

- PlatoData.Network 수직 생성 Ai. 자신에게 권한을 부여하십시오. 여기에서 액세스하십시오.

- PlatoAiStream. 웹3 인텔리전스. 지식 증폭. 여기에서 액세스하십시오.

- 플라톤ESG. 자동차 / EV, 탄소, 클린테크, 에너지, 환경, 태양광, 폐기물 관리. 여기에서 액세스하십시오.

- PlatoHealth. 생명 공학 및 임상 시험 인텔리전스. 여기에서 액세스하십시오.

- 차트프라임. ChartPrime으로 트레이딩 게임을 향상시키십시오. 여기에서 액세스하십시오.

- BlockOffsets. 환경 오프셋 소유권 현대화. 여기에서 액세스하십시오.

- 출처: https://semiwiki.com/prototyping/s2c-eda/333925-systematic-risc-v-architecture-analysis-and-optimization/