IC 設計には、レイアウトと回路図が同等であることを確認するトランジスタ レベルのレイアウト対回路図 (LVS) などの物理検証アプリケーションがあり、さらにソフト チェックと呼ばれるウェル領域への接続用の電気ルール チェック (ERC) もあります。すべてのデバイスへの接続には、最も一貫した電圧信号が必要です。したがって、抵抗やIRドロップなどの要因を減らすために、パスは金属層を通過する必要があります。接続の検出にはウェルズのような他の材料が必須であると考えられていました。ソフトチェックは、この状況を検出するために最も一般的に使用される方法です。の 口径 Siemens の製品ラインは DRC および LVS チェック用の最も人気のあるツールであるため、ソフト チェックについて詳しく知るために Terry Meeks の技術論文を読みました。

IC レイアウトで 1 つの金属層を接続するには、両方の金属層とビア層を正確に位置合わせする必要があります。ここでは、側面図と上面図の両方を使用した比較を示します。最初の例は Metal2 と Metal XNUMX が重なっていないため接続されていませんが、XNUMX 番目の例は適切に接続されています。

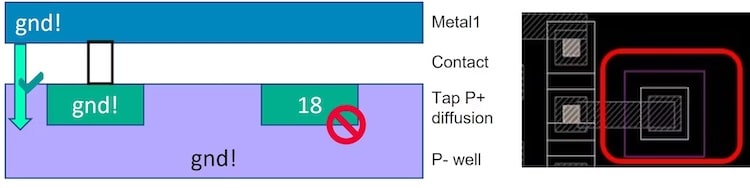

ERC ツールがソフト チェック中にウェル接続エラーを特定し、修正できるようにしたいと考えています。次の IC レイアウトにはウェル接続エラーがあり、側面図で示されています。Gnd としてテキスト表示された Metal1 信号がタップ拡散と呼ばれる拡散領域に接続されています。右側にはタップ拡散を備えた別の Metal1 層がありますが、この接続により Rwell に Gnd への高抵抗パスが作成され、ソフト チェックによってエラーとしてフラグが立てられます。

ソフト接続エラーの別の例は、ポリゴンごとに 1 つの名前しか適用できない以下の IC レイアウトで発生します。デジタル パワー ネット VDD はアナログ パワー ネット AVDD と共存できず、これらを 2 つの形状に分離する必要があります。ソフト チェックは、これらの問題にフラグを立てるのに役立ちます。

デジタル電源とアナログ電源の両方を備えた IC レイアウトは、適切にレイアウトするにはかなり複雑になる可能性があるため、ソフト チェックを行うことがさらに重要です。

ソフトチェックはLVSの実行中に含まれます。 キャリバーnmLVS ソフト チェック結果のレポートがあり、 キャリバー RVE ビューア。

RVE 結果をクリックすると、どのセルにソフト チェック エラーがあるか、ネット名、上位名と下位名、その他のプロパティが表示されます。この情報は、IC レイアウトの何を修正すべきかを正確に特定するのに役立ちます。ソフト チェック エラーの PWell などの下位レイヤーをクリックすると、ジオメトリが黄色で表示されます。

同じソフト チェック エラーの場合、上のレイヤーをクリックすると次が表示されます。

デバッグ中に、すべての上位レイヤ シェイプを表示することもできます。緑色のシェイプは選択されたネット上位レイヤ シェイプ、黄色は拒否されたネット上位レイヤ シェイプです。

RVE を使用してソフト チェック エラーをデバッグするには、選択したネットと拒否されたネットの接続をクリックする必要があります。 [ネット情報] ウィンドウには、どのレイヤーが関係しているか、図形の接続が欠落しているかどうかなどの詳細が表示されます。どのポートがネットに接続されているかを確認すると、VDD または GND の欠落エラーがあるかどうかがわかります。この例では、ネット 18 は Metal1 への接続がないため拒否されることを示しています。

まとめ

LVS チェックは、IC にエラーのないレイアウトがあることを確認するために必須であり、ソフト チェックは LVS チェックの一部です。 Siemens の Calibre nmLVS ツールには実証済みのデバッグ フローがあり、RVE を使用してレイアウト設計者がソフト チェックの失敗を迅速に特定できるようにするため、設計者はすべてのチェックに合格するまで修正して再検証できます。シーメンスはオンラインで読める技術文書を執筆しました。 ソフトチェック接続エラーの検出とデバッグ.

関連ブログ

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/eda/342526-soft-checks-are-needed-during-electrical-rule-checking-of-ic-layouts/