多くの場合、設計者は、先進的なパッケージ設計における金属充填領域に対する製造業者や製造業者の要件の多様性に驚かされます。 パッケージの製造者や製造業者は、固体の金属面や大きな金属領域を好みません。 同社の厳格な金属充填要件は、15 つの主要な問題に対処しています。 誘電体層と金属層は XNUMX µm 以下と非常に薄い場合があり、ビルドアップおよび RDL プロセス中に閉じ込められたガスのポケットにより層間剥離が発生する可能性があります。 スマートフォンにスクリーンプロテクターを貼り付けるようなもので、気泡を取り除くのがどれほど難しいかを考えてください。 また、同じ層上または層ペア間で導体密度が不均一であると、パッケージやウェハに反りが生じる可能性があります。

これらの問題が組み合わさることにより、製造ルールを満たすという設計者の仕事が困難になります。 さらに、多数のベンダーによる基板テクノロジーの多様性は、すべてに適合する万能のソリューションがないことを意味します。 この記事では、金属領域およびプレーンに対するファウンドリ/OSAT 要件を達成するために高度なパッケージ設計で一般的に使用される XNUMX つの方法論について説明します。

- 動的ハッチングされた塗りつぶされた金属領域

これまでで最も簡単で最速の方法論。 密度要件に基づいて、いくつかの追加手順が必要になる場合があります。 - 金属領域のボイドのガス放出

あらゆる状況に合わせてカスタマイズできる後処理ソリューション。 - ダミーメタルフィル

これは、ほとんどのシリコン設計が低密度領域を処理する方法です。 通常、シリコン インターポーザーの設計に使用されます。

動的ハッチングされた塗りつぶされた金属領域

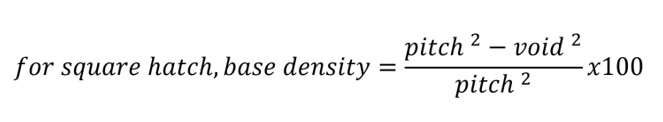

ガス放出と金属充填カバレッジの両方を解決する最も簡単な方法の XNUMX つは、動的ハッチング充填を使用することです。 正方形または斜めのハッチングを追加する場合、パッケージ デザイン ツールは平面全体の基本密度がどのくらいになるかを通知するため、目標密度を達成するのが非常に簡単になります。

鋭角の問題を防ぐために、不完全なハッチングまたは部分的なハッチングを必ず埋める必要があります。また、EMI および信号整合性の問題を防ぐために、隣接するレイヤーのハッチングをオフセットする必要もあります。 プロジェクトの最初にこれらを設定すると、テープアウトの直前またはテープアウト中に直前に設定するよりも時間を節約できます。 ほとんどのメーカーや製造業者には、製造を開始する前に満たす必要がある製造承認設計ルールがあります。 これらの設計ルールは、間隔などの製造および歩留まりの問題や、鋭角、密度、塗りつぶしなどのレイアウト項目の問題をチェックします。 違反が見つかった場合、設計ルール チェック ツールからレイアウト ツールへのクロスプローブ機能がサポートされている場合、設計者は違反を見つけて修正する時間を節約できます。

図 1. 30 µm ボイド、40 µm ピッチ、43% 充填

一部のテクノロジーでは、基本ハッチングを修正して、特定のベンダーに必要な他の機能を追加できます。

図 2. パッド ボイドと追加のプレーン ボイドを備えた HDFOWLP

専用のガス抜きボイド

設計者が独立したガス放出ボイドを利用するのはよく見られます。 動的ハッチング塗りつぶしとは異なり、これは後処理です。 設計者は、ガス放出ボイドを使用して、円、長方形、長方形、八角形、六角形などのボイド形状を作成したり、ボイドを互い違いに配置したりします。 数式が見つかったら、プロセスは予測可能であり、レイアウト変更の更新も非常に簡単です。 密度を意識したマルチパスガス抜きルーチンを使用することで、設計者は製造プロセスの要件を同時に考慮しながらシグナルインテグリティとパワーインテグリティの問題に取り組むことができ、大幅な時間の節約につながります。

金属のバランスは、層ごとの密度または層ペアの目標にすることができます。 一部のメーカーは、ウォーキング ブロックや隣接ブロックなどのサブレイヤー ブロック (密度の 125 μm ~ 250 μm ウィンドウ) も利用しています。

図 3. 125 µm 密度のサブブロック領域

どのようなルールであっても、隣接する層のボイドがオフセットされていることを確認し、ボイドが差動信号配線を越えないようにしてください。 差動信号またはペア上の隣接する層にボイドが不均一に分散している場合、問題が発生する可能性があります。 また、ボイドからマイクロビア/ポリアミド開口部、またはトレースまでのクリアランス規則が見られる場合もあります。

図 4. マルチパス密度を考慮したボイド

図 5. 隣接層の空隙クリアランス

高速設計または高電流引き込みの設計では、設計者は自動ガイドによる手動ボイド配置を利用します。 これにより、ユーザーは各ボイドがどこに配置されるかを完全に認識しながら、製造要件を満たすことができます。 5G パッケージはこの方法に最適な使用例であり、不要なボイドの手動クリーンアップに時間がかかりすぎる完全自動化方法のショットガン アプローチよりも推奨されます。

図 6. 差動ペアへの千鳥配置の長方形のボイド

図 7. ボイドの脱気分析により、ボイドの挿入が必要な領域が特定される

図 8. ボイドが追加されると、円は有効半径を示します。

空隙が必要な緑色の領域と、隣接するレイヤーが表示されます

ダミーメタルフィル

高帯域幅メモリ (HBM) または RDL 相互接続を備えたインターポーザ設計で利用されるもう XNUMX つのメタル バランシング方法は、ダミー フィルです。 ダミー フィルとは、接続されていない金属形状を指します。 これにより、静電容量が低減され、製造歩留まりが向上します。 設定された最大長まで拡張できる複数の形状を使用したマルチパスにすることができます。 また、密度を認識し、目標値に達するように塗りつぶしを追加することもできます。

ホスト レイアウト ツールで密度ウィンドウを視覚化できる密度分析ツールを使用することは、ベンダー ルールを満たさない領域とレイヤーを見つけて修正するために最も重要です。

これらの方法論のいずれにおいても、ソリューションがパフォーマンス仕様を満たしていることを確認するためにシミュレーションを行う必要があります。 ファウンドリと OSAT は製造性と歩留まりに重点を置いていますが、性能仕様への準拠を保証するのはユーザーの責任です。 ガス放出方法論を無視する前に、電力供給をシミュレーションする必要があります。 一見すると、前の例で見たように信号が何百ものボイドのある平面領域を横切るのは悪いアイデアのように聞こえるかもしれません。しかし、ソリッドフィルと同様に動作する可能性があり、問題が発生しない可能性があります。 PDN シミュレーションがなければ、その適合性を推測するだけになります。

図 9. マルチパス密度を考慮したダミー塗りつぶし

適切な方法を使用した分析により、設計が性能仕様を満たしていることが保証されます。 推奨される解析タイプには、DC 降下 (電圧降下、電流密度、ビア電流)、PDN インピーダンス解析、およびリターン パス チェックを含むシグナル インテグリティ解析が含まれます。

図 10. トレースの下のクロスハッチングされたプレーン層を流れる密結合リターン電流

まとめ

要約すると、動的ハッチング充填、ガス抜きボイド、およびダミー金属充填は、金属領域および金属面に対する鋳造/OSAT 要件を達成するための最も一般的な方法です。 重要なのは、ベンダーのルールに最も適合し、PDN 仕様を満たし、迅速な ECO ターンを可能にし、再現性のある方法論を選択することです。 検証を迅速に行うために、ベンダー サインオフ ツールとレイアウト ツールの間で動的クロスプローブを必ずオンにしてください。

ケンダル・ハイルズは、

また読む:

今日の SoC 設計の検証と検証には、XNUMX 種類のハードウェア支援型エンジンが必要です

この投稿を共有する: