私はこれまで、ミックスシグナルの話題はデジタルから切り離されており、専門家に任せられると考えて避けてきました。 その単純な見方はもはや説得力を持ちません。 アナログとデジタルは、制御ループとデータパスを通じてより緊密にリンクされるようになっており、検証においてはパフォーマンス、精度、全体的なメトリクス主導の検証の間で慎重なバランスを取る必要があります。

この分野のサポートの改善は、あると嬉しいものではありません。 2020年のウィルソンの調査では、アナログの問題によるリスピンの大幅な増加が報告されています。 さらに悪いことに、システム顧客は現在、カバレッジ、安全性、電力に関する統一されたメトリック データを要求しています。 完全なシステム検証の課題と解決策をより深く理解するには、デジタルのコンフォートゾーンから飛び出す必要があります。 この道に沿って私を導いてくださったケイデンスの Shekar Chetput (Xcelium/Mixed Signal の R&D グループ ディレクター) と Paul Graykowski (プロダクト マーケティング ディレクター) に感謝します。 😊

アプリケーションドライバーとミックスドシグナルの課題

あらゆるタイプのセンサーには、校正データとドリフト補償データを収集するためのデジタル サポートが必要です。 キャリブレーションも IO インターフェイスの要素です。 DDR がよく知られた例です。 5G/6G の RF は、やはりデジタル ドメインから管理される複数の帯域とハイブリッド ビームフォーミングをサポートする必要があります。 EV に不可欠なバッテリー管理システムは、プレコンディショニング、急速充電、トップオフ、バッテリー保護などの高度な充電と使用動作を処理し、すべて (ご想像のとおり) デジタルで監視されます。

非常に高い安全性と信頼性の基準が保たれている医療用インプラントは、無線通信を提供するようになりました。また、センシングとアクチュエーターは身体モデル (RC ネットワーク) に対して検証する必要があります。 不揮発性メモリセルは複数の電圧を処理し、読み取り、プログラミング、摩耗/エラー検出のための回路をサポートします。 デジタル設計であっても、デジタル制御下で複数の電圧を供給し、複雑な電源管理シナリオを監視する電源管理 IC (PMIC) に依存しています。 これらは現在、EV の高電圧管理にまで拡張されています。

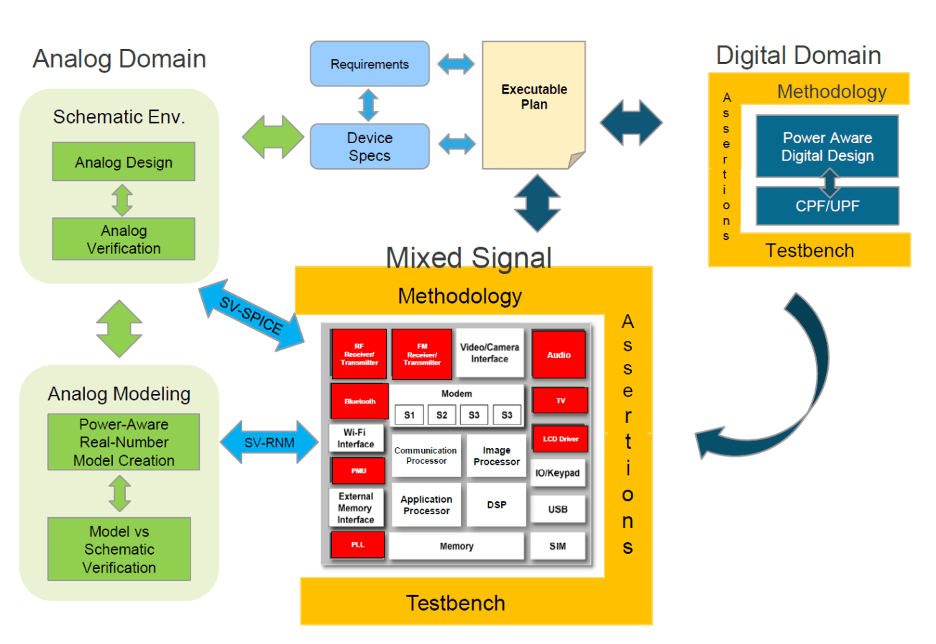

すべての目的に共通するのは、SPICE モデルの精度は高いがサイクル/秒が非常に低いアナログ/RF の世界と、サイクル/秒のスループットは非常に高いがアナログ精度が非常に低いデジタルの世界 (0/秒) の間のバランスを見つける必要があることです。 1 は電圧を表し、電流やインピーダンスの概念はありません)。 協調シミュレーションは明白な答えですが、低精度/高パフォーマンスと高精度/低パフォーマンスを単に結合することはできません。 これらにはインテリジェントなインターフェイスが必要です。

正しいバランスを見つける

まず SPICE の実行を高速化し、デジタル シミュレーションをより正確にします。 Cadence は、Spectre FX シミュレーターを通じて SPICE を高速化します。回路の一部は、完全なアナログ精度から段階的に抽象化されたモードまで、完全な精度を犠牲にしながらある程度の精度を維持する 4 つのモードのいずれかで実行できます。

デジタルの精度を向上させるための最初のステップは、単純なインターフェイスには十分な実数信号である Verilog-AMS/SystemVerilog wreal のサポートです。 Verilog/SV ネットタイプでサポートされる実数モデル (RNM) を使用すると、アナログ モデリングに近いものが可能になります。RNM では、信号が電圧、電流、インピーダンス構造としてモデル化され、接続されたネット間の解決が可能になります。 ケイデンスは、RNM ネットタイプ EEnet (電気的等価ネット) を提供します。 EEnets を使用すると、テストを実行する有意義な動作モデルを何桁も高速に構築できると同時に、一部のユースケースでは SPICE レベルの精度に近づくことができます。

Spectre FX と RNM/EEnet モデルを組み合わせると、モデリングにさまざまな可能性が提供されます。 完全な動作の wreal または EEnet モデルは、アーキテクチャ設計において、詳細に行き詰まりすぎずにさまざまなオプションを検討するのに非常に役立ちます。 モデルが利用可能になると、この使用例が現在大きな注目を集めていると Shekar 氏は語ります。

より詳細な検証では、速度を重視する特定のアナログ ブロックには RNM を、電源電圧や温度変動に対する感度解析など、RNM 解析の範囲を超えて精度が重要な SPICE レベルには、組み合わせて使用することが理想的であることがよくあります。

モデルの構築

これだけ聞くと素晴らしいように思えますが、これらのモデルはどこから来たのでしょうか? 基本的なネットタイプは柔軟ですが、非常に低レベルなので、SystemVerilog に慣れていないアナログ設計者による多大な投資が必要になります。 Cadence には、ベース共通回路 (コンデンサ、ダイオード、インダクタ、MOS デバイスなど) の EEnet 標準ライブラリと、これらのコンポーネントの使用例を示すミックスド シグナル モジュールのテスト ライブラリがあります。 設計者は、これらのコンポーネントを使用して、より複雑なコンポーネントを概略的に構築できます。

Shekar 氏によると、EEnet の初期の頃から顧客と協力してきたため、この基本ライブラリは非常に安定しており、最近では Xcelium Mixed-Signal App の一部としてリリースされたとのことです。 ケイデンスは現在、いくつかの中間レベルのコンポーネント (PLL、電圧レギュレータ、ADC、DAC など) の構築とレビューに取り組んでいます。 同社の顧客は、さらに複雑な機能まで拡張する独自の中間レベルのコンポーネントも構築しています。 パッケージ化されたライブラリを待つのではなく、必要性が進歩を促進しているようです。

モデルの構築には多大な労力が費やされるため、標準化について少し余談を述べます。 Lu Dai (Accellera 議長) は今年の DVCon で私に、Accellera ミックスド シグナル ワーキング グループは非常に活発であり、ユーザーからの要求も強いと語った。 Cadence は参加しており、この分野で定評があるため、彼らのリリースは標準で最終的に合意されたものに近いものになる可能性が高いと思います。 しかしルー氏は、SV 標準は現在 IEEE に準拠しており、更新頻度が低いため、一部の SV 混合信号更新要求の動きが遅いと警告しました。 Accellera は回避策を検討しています。

テストベンチの自動化、アサーション、カバレッジなど

シミュレーションのスループットを高めることは常に重要な目標ですが、混合信号検証チームにはさらに多くのことが必要です。 彼らは、デジタル ピアが日常的に使用している自動化を望んでおり、これを混合信号にも拡張するために熱心にロビー活動を行っています。 Accellera の下で UVM-AMS 作業グループがこの目的に向けてすでに進行中です。 標準はまだリリースされておらず、スケジュールの問題にも取り組んでいますが、正しい方向に進んでいます。

それまでの間、設計者と検証者は独自のフローを通じてこれらのニーズに応えます。 これらも進化する標準を追跡しているのではないかと思います。 Cadence は、UVM テストベンチ、通常のアサーション、および複雑な混合信号アサーションとランダム化を通じて、デジタルとアナログにわたるメトリック駆動の検証をサポートします。 純粋なアナログの場合、カバレッジおよびその他のステータスを Virtuoso ADE Verifier から vManager にインポートできます。

要約すると、ミックスドシグナル検証は大幅に進歩しており、標準化による進歩が期待されています。 ミックスシグナル検証は、まさにデジタル検証の第一級パートナーになりつつあります。 Xcelium Mixed Signal アプリに関する詳細情報を入手できます こちら、Spectre FX シミュレーター こちら ミックスシグナルに関する有益なウェビナー こちら.

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 自動車/EV、 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- チャートプライム。 ChartPrime でトレーディング ゲームをレベルアップしましょう。 こちらからアクセスしてください。

- ブロックオフセット。 環境オフセット所有権の近代化。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/eda/334146-mixed-signal-verification-is-growing-in-importance/