低消費電力 SoC に対する絶え間ない需要は、多くの市場で明らかです。例としては、最先端のモバイル、IoT、ウェアラブル デバイスや、AI や 5G/6G 通信に対する高いコンピューティング需要などが挙げられます。低電力の要因としては、バッテリー寿命、熱管理、およびハイコンピューティングアプリケーションの場合は全体的な運用コストが挙げられます。低消費電力を実現するには、いくつかのアプローチが利用可能です。多くの人に共通するのは、最適な Foundation IP、つまり組み込みメモリとロジック ライブラリの必要性です。これはシノプシスにとって重要な投資分野であり、市場でのリーダーシップを発揮する分野です。利用可能なオプションと利点を理解するのに役立つ XNUMX つの有益な出版物が入手可能になりました。 Synopsys Foundation IP メモリ コンパイラとロジック ライブラリを使用すれば、極度の低消費電力を実現できることがわかりました。

入手可能な情報を見てみましょう。

技術速報

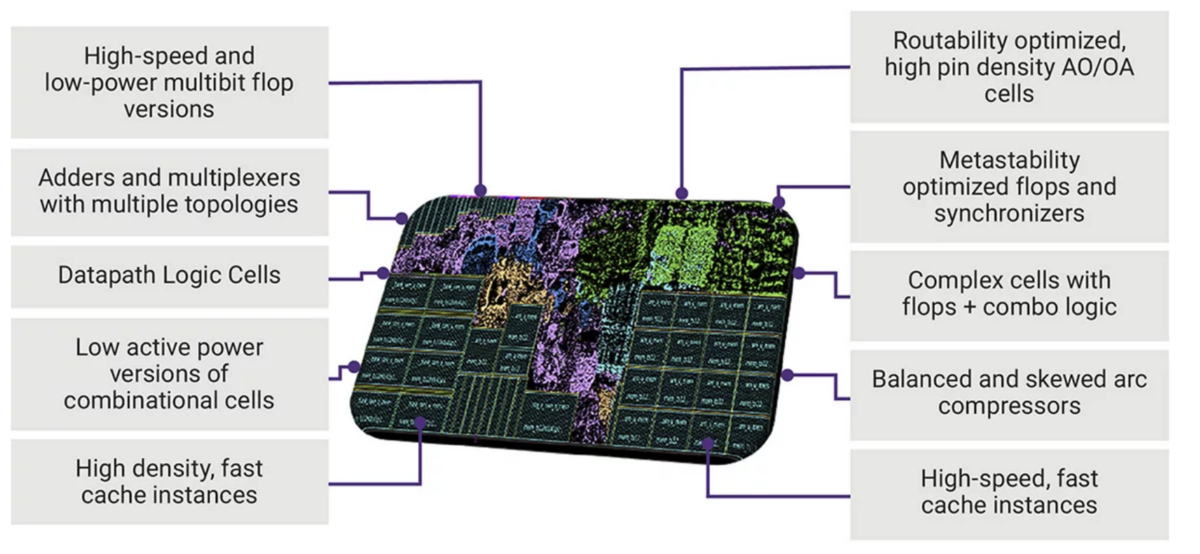

から始めます Synopsys Foundation IP を使用した HPC および AI アプリケーションの PPA の最適化、ロジック ライブラリに焦点を当てた技術情報。この記事では、Synopsys のツール対応 Foundation IP ソリューションについて詳しく説明します。最適化された回路、幅広い動作電圧範囲のサポート、顧客固有の最適化を追加する柔軟性などのトピックについて説明します。この記事では、可能な最大のパフォーマンス、または電力とパフォーマンスの最適なトレードオフのいずれかを達成するための視点も提供します。以下の図は、HPC デザイン キットで使用できるロジック ライブラリ回路をまとめたものです。

消費電力の向上がどのように達成されるかについての詳細は、多くのアプリケーションおよび設計戦略にわたって提供されます。取り上げられるトピックには、幅広い動作電圧範囲にわたる動的な電圧スケーリング、AI とアプリケーション固有のアクセラレータ ブロック PPA の最適化、ネットワーク オン チップのソリューション、効率的な SoC 実装のために Synopsys HPC Design Kit が Synopsys EDA とどのように連携最適化されるかなどが含まれます。

この技術情報には、豊富な情報と例が含まれています。あなたはできる ここからこの情報にアクセスしてください.

ホワイトペーパー

また、次のタイトルの包括的なホワイト ペーパーも入手できます。 どこまで下げることができますか?トランジスタの限界を押し上げる。この記事では、組み込みメモリとロジック ライブラリの両方について詳しく説明します。極度の低消費電力を実現する背後にある詳細を検証します。モバイル、Bluetooth と IoT、ハイパフォーマンス コンピューティング、自動車、暗号化など、いくつかのアプリケーション分野について説明します。

埋め込みメモリについては、支援技術や電源電圧の分割など、いくつかのアプローチが説明されています。低電圧で高密度の低電力メモリ動作を実現するには、メモリ支援回路の技術と設計の間の注意深い相互最適化が必要であることが指摘されています。いくつかの強化された支援テクニックをレビューします。出力の向上範囲は 10% ~ 37% です。

記憶の信頼性についても議論する。この記事では、電圧が低下すると、SRAM セルが劣化し始めると説明しています。この劣化により、読み取りの混乱、ビットセルの反転、SER の発生、センシングの失敗、制御信号の逸脱、BL 信号の弱化など、複数の問題が発生する可能性があります。したがって、最先端の低電力アプリケーションで必要とされるより低い極低電圧をサポートするには、支援技術が必要です。

ここでシノプシスが採用したアプローチは大きな違いをもたらします。信頼性を向上させる戦略と経年劣化をシミュレートする方法について説明します。詳細は自分で読んでください。リンクが表示されます。データは、5 ~ 10 年の寿命を追加した説得力のある結果を示しています。

0.4V 以下での極低電圧動作を可能にする戦略を含むロジック ライブラリについても説明します。アーキテクチャの最適化も見直されます。標準セルのアーキテクチャ技術を使用して、動的電力と漏れ電力の両方を削減できます。たとえば、シノプシスは、深低電圧動作に最適なトポロジーを実現するために、スタックベースではなくステージベースのアーキテクチャ技術を使用しています。このアプローチの背後にある戦略が示されています。

特性評価の最適化についても説明します。特性評価の重要な部分の 1 つは、オンチップ バリエーション (OCV) と呼ばれる、SoC 全体にわたるプロセスのバリエーションをモデル化することです。ここでは、精度を向上させ、パフォーマンスと電力を最適化するための機械学習など、いくつかの高度な技術が採用されています。

ホワイトペーパーは、超低電圧動作を実現するために SoC レベルですべてを統合する方法の概要で締めくくられています。電圧低減については、DVFS (dynamic Voltage and Frequency Scaling) 技術や、ライト スリープ、ディープ スリープ、フル シャットダウン、POFF (ペリフェラル オフ) モードなどのさまざまなシャットダウン戦略とともに説明します。

このホワイト ペーパーでは、電力最適化に関する多くのトピックを詳細に取り上げています。ぜひお勧めします。あなたはできる ここでコピーを入手してください。このようにして、Synopsys Foundation IP メモリ コンパイラとロジック ライブラリを使用して極度の低消費電力を実現することが可能になります。

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/