Chiplets gewinnen auf dem Automobilmarkt zunehmend an Bedeutung, da die zunehmende Elektrifizierung und der intensive Wettbewerb Unternehmen dazu zwingen, ihre Entwicklungs- und Produktionspläne zu beschleunigen.

Die Elektrifizierung hat einige der größten und bekanntesten Automobilhersteller in Aufruhr versetzt, die angesichts sehr kurzer Marktfenster und sich ständig ändernder Anforderungen darum kämpfen, wettbewerbsfähig zu bleiben. Anders als in der Vergangenheit, als Automobilhersteller in der Regel fünf bis sieben Jahre dauernde Entwicklungszyklen durchführten, kann die neueste Technologie in Fahrzeugen heute durchaus davon ausgehen, dass sie innerhalb weniger Jahre veraltet ist. Und wenn sie nicht mithalten können, gibt es eine ganze Reihe neuer Start-ups, die günstige Fahrzeuge herstellen und die Möglichkeit haben, Funktionen so schnell wie ein Software-Update zu aktualisieren oder auszutauschen.

Aber Software unterliegt Geschwindigkeits-, Sicherheits- und Zuverlässigkeitsbeschränkungen, und viele Autohersteller setzen jetzt ihre Anstrengungen auf die Möglichkeit, die Hardware anzupassen. Hier kommen Chiplets ins Spiel, und der Fokus liegt nun darauf, wie man eine ausreichende Interoperabilität über große Ökosysteme hinweg aufbauen kann, um daraus einen Plug-and-Play-Markt zu machen. Zu den Schlüsselfaktoren für die Interoperabilität von Automobil-Chiplets gehören Standardisierung, Verbindungstechnologien, Kommunikationsprotokolle, Energie- und Wärmemanagement, Sicherheit, Tests und Ökosystemzusammenarbeit.

Ähnlich wie bei nicht-automobilen Anwendungen auf Platinenebene konzentrieren sich viele Designbemühungen auf einen Die-to-Die-Ansatz, der eine Reihe neuartiger Designüberlegungen und Kompromisse nach sich zieht. Auf Chipebene werden die Verbindungen zwischen verschiedenen Prozessoren, Chips, Speicher und I/O aufgrund der gestiegenen Anforderungen an die Designleistung immer komplexer, was zu einer Vielzahl von Standardisierungsaktivitäten führt. Verschiedene Verbindungs- und Schnittstellentypen wurden vorgeschlagen, um unterschiedlichen Zwecken zu dienen Chiplet Technologien für dedizierte Funktionen – Prozessoren, Speicher und I/Os, um nur einige zu nennen – verändern die Herangehensweise an das Chipdesign.

„Automobil-OEMs sind sich darüber im Klaren, dass sie, um ihr eigenes Schicksal zu kontrollieren, ihre eigenen SoCs kontrollieren müssen“, sagte David Fritz, Vizepräsident für virtuelle und hybride Systeme bei Siemens EDA. „Sie verstehen jedoch nicht, wie weit EDA seit ihrem College-Studium im Jahr 1982 fortgeschritten ist. Außerdem glauben sie, dass sie zum neuesten Prozessknoten gehen müssen, wo ein Maskensatz 100 Millionen US-Dollar kosten wird.“ Das können sie sich nicht leisten. Sie haben auch keinen Zugang zu Talenten, da der Talentpool recht klein ist. Zusammen mit all dem kommt den OEMs die Erkenntnis, dass sie, um ihr Schicksal in die Hand zu nehmen, eine Technologie benötigen, die von anderen entwickelt wurde, die aber beliebig kombiniert werden kann, um ein einzigartiges, differenziertes Produkt zu erhalten, von dem sie überzeugt sind, dass es zumindest für einige wenige zukunftssicher ist Modelljahre. Dann wird es wirtschaftlich rentabel. Das Einzige, was in Frage kommt, sind Chiplets.“

Chiplets können für bestimmte Funktionen optimiert werden, was Automobilherstellern dabei helfen kann, Zuverlässigkeits- und Sicherheitsanforderungen mit einer Technologie zu erfüllen, die sich in mehreren Fahrzeugdesigns bewährt hat. Darüber hinaus können sie die Markteinführungszeit verkürzen und letztendlich die Kosten verschiedener Features und Funktionen senken.

Die Nachfrage nach Chips ist im letzten Jahrzehnt gestiegen. Laut Allied Market Research wird die weltweite Nachfrage nach Automobilchips von 49.8 Milliarden US-Dollar im Jahr 2021 auf 121.3 Milliarden US-Dollar im Jahr 2031 steigen. Dieses Wachstum wird noch mehr Innovationen und Investitionen in Automobilchips anziehen, und Chiplets dürften davon stark profitieren.

Es wird jedoch einige Zeit dauern, bis der Markt für Chiplets ausgereift ist, und er wird wahrscheinlich schrittweise eingeführt. Zunächst bietet ein Anbieter verschiedene Varianten proprietärer Matrizen an. Dann werden die Partner zusammenarbeiten, um sich gegenseitig mit Chiplets zu unterstützen, wie es bei einigen Anbietern bereits geschehen ist. Die letzte Stufe werden universell interoperable Chiplets sein, wie sie von UCIe oder einem anderen Verbindungsschema unterstützt werden.

Das Erreichen der Endphase wird am schwierigsten sein und erhebliche Änderungen erfordern. Um die Interoperabilität sicherzustellen, müssen ausreichend große Teile des Automobilökosystems und der Lieferkette zusammenkommen, darunter Hardware- und Softwareentwickler, Gießereien, OSATs sowie Material- und Ausrüstungslieferanten.

Die Dynamik nimmt zu

Positiv ist, dass nicht alles bei Null beginnt. Auf Platinenebene nutzten Module und Subsysteme schon immer Onboard-Chip-zu-Chip-Schnittstellen und werden dies auch weiterhin tun. Verschiedene Chip- und IP-Anbieter, darunter Cadence, Diode, Microchip, NXP, Renesas, Rambus, Infineon, Arm und Synopsys, stellen handelsübliche Schnittstellenchips oder IP zur Herstellung des Schnittstellensiliziums bereit.

Das Universal Chiplet Interconnect Express (UCIe)-Konsortium ist die treibende Kraft hinter dem Die-to-Die-Standard für offene Verbindungen. Die Gruppe veröffentlichte ihre neueste UCIe 1.1-Spezifikation im August 2023. Zu den Vorstandsmitgliedern gehören Alibaba, AMD, Arm, ASE, Google Cloud, Intel, Meta, Microsoft, NVIDIA, Qualcomm und Samsung und andere. Industriepartner zeigen breite Unterstützung. AIB und Bunch of Wires (BoW) wurden ebenfalls vorgeschlagen. Darüber hinaus hat Arm gerade seine eigene Chiplet-Systemarchitektur sowie eine aktualisierte AMBA-Spezifikation zur Standardisierung von Protokollen für Chiplets veröffentlicht.

„Chiplets gibt es bereits, bedingt durch die Notwendigkeit“, sagte Arif Khan, Senior Product Marketing Group Director für Design IP bei Cadence. „Die wachsenden Prozessor- und SoC-Größen stoßen an die Retikelgrenze und die Skaleneffekte. Die inkrementellen Gewinne aus Fortschritten in der Prozesstechnologie sind geringer als die steigenden Kosten pro Transistor und Design. Die Fortschritte in der Verpackungstechnologie (2.5D/3D) und der Schnittstellenstandardisierung auf Die-to-Die-Ebene, wie beispielsweise UCIe, werden die Chiplet-Entwicklung erleichtern.“

Fast alle heute verwendeten Chiplets werden von großen Chipherstellern wie Intel, AMD und Marvell selbst entwickelt, da sie die Eigenschaften und das Verhalten dieser Chiplets genau steuern können. Aber es wird auf allen Ebenen daran gearbeitet, diesen Markt für mehr Akteure zu öffnen. Wenn dies geschieht, können kleinere Unternehmen damit beginnen, aus den bisherigen Errungenschaften der prominenten Vorreiter Kapital zu schlagen und auf der Grundlage dieser Entwicklungen Innovationen zu entwickeln.

„Viele von uns glauben, dass der Traum von einem serienmäßigen, interoperablen Chiplet-Portfolio wahrscheinlich Jahre dauern wird, bis er Wirklichkeit wird“, sagte Guillaume Boillet, Senior Director Strategic Marketing bei Arteris, und fügte hinzu, dass die Interoperabilität durch Gruppen von Partnern entstehen wird, die dies tun befassen sich mit dem Risiko unvollständiger Spezifikationen.

Dies erhöht auch die Attraktivität von FPGAs und eFPGAs, die ein gewisses Maß an Anpassung und Aktualisierungen für Hardware im Feld ermöglichen können. „Chiplets sind eine echte Sache“, sagte Geoff Tate, CEO von Flex Logix. „Im Moment kann ein Unternehmen, das zwei oder mehr Chiplets herstellt, viel wirtschaftlicher arbeiten als ein Unternehmen, das Chips in nahezu Retikelgröße fast ohne Ausbeute baut. Die Chiplet-Standardisierung scheint noch in weiter Ferne zu liegen. Auch UCIe ist noch kein fester Standard. Nicht alle sind sich einig über UCIe, Bare-Die-Tests und darüber, wer das Problem hat, wenn das integrierte Paket nicht funktioniert usw. Wir haben einige Kunden, die eFPGA für Schnittstellen verwenden oder evaluieren, bei denen sich Standards wie UCIe im Wandel befinden. Sie können jetzt Silizium implementieren und das eFPGA später zur Anpassung an Standardänderungen verwenden.“

Es gibt auch andere Bestrebungen, Chiplets zu unterstützen, allerdings aus etwas anderen Gründen – insbesondere wegen der steigenden Kosten für die Geräteskalierung und der Notwendigkeit, mehr Funktionen in Chips zu integrieren, die an den fortschrittlichsten Knotenpunkten auf das Retikel beschränkt sind. Aber diese Bemühungen ebnen auch den Weg für Chiplets in der Automobilindustrie, und es gibt starke Unterstützung aus der Industrie, damit das alles klappt. Beispielsweise untersucht die neue Heterogeneous Integration Roadmap (HIR) unter der Schirmherrschaft von SEMI, ASME und drei IEEE-Gesellschaften verschiedene Design-, Material- und Verpackungsprobleme der Mikroelektronik, um eine Roadmap für die Halbleiterindustrie zu erstellen. Ihr aktueller Schwerpunkt umfasst 2.5D, 3D-ICs, Wafer-Level-Packaging, integrierte Photonik, MEMS und Sensoren sowie System-in-Package (SiP), Luft- und Raumfahrt, Automobil und mehr.

Auf dem jüngsten Heterogeneous Integration Global Summit 2023 trafen sich Vertreter von AMD, Applied Materials, ASE, Lam Research, MediaTek, Micron, Onto Innovation und TSMC, und andere zeigten starke Unterstützung für Chiplets. Eine weitere Gruppe, die Chiplets unterstützt, ist die Chiplet-Design-Austausch (CDX) Arbeitsgruppe, die Teil der ist Offene domänenspezifische Architektur (ODSA) und der Open Compute Project Foundation (OCP). Die Chiplet Design Exchange (CDX)-Charta konzentriert sich auf die verschiedenen Merkmale von Chiplets und der Chiplet-Integration, einschließlich elektrischer, mechanischer und thermischer Design-Austauschstandards für 2.5D-Stack- und 3D-integrierte Schaltkreise (3D-ICs). Zu seinen Vertretern gehören Ansys, Applied Materials, Arm, Ayar Labs, Broadcom, Cadence, Intel, Macom, Marvell, Microsemi, NXP, Siemens EDA, Synopsys und andere.

„Die Wünsche der Automobilunternehmen hinsichtlich der Funktionalität jedes Chiplets befinden sich noch im Umbruch“, bemerkte Fritz von Siemens. „Das eine Extrem hat diese Probleme, das andere Extrem hat diese Probleme. Das ist der Sweet Spot. Das ist es, was benötigt wird. Und das sind die Arten von Unternehmen, die diese Art von Arbeit erledigen können, und dann könnte man sie zusammenstellen. Dann ist diese Interoperabilitätssache keine große Sache. Der OEM kann es zu komplex machen, indem er sagt: „Ich muss mit dem gesamten Spektrum an Möglichkeiten umgehen.“ Die Alternative wäre, dass sie sagen könnten: „Es ist wie ein Hochgeschwindigkeits-PCIe.“ Wenn ich von einem zum anderen kommunizieren möchte, weiß ich bereits, wie das geht. Ich habe Treiber, die mein Betriebssystem ausführen. Das würde eine Menge Probleme lösen, und ich glaube, dass das auch der Fall sein wird.“

Ein Weg zur universellen Chiplet-Entwicklung?

In Zukunft werden Chiplets ein Schwerpunkt sowohl für die Automobil- als auch für die Chipindustrie sein, und das wird alles umfassen, von Chiplet-IP über Speicherverbindungen bis hin zu Anpassungsoptionen und -beschränkungen.

Beispielsweise kündigte Renesas Electronics im November 2023 Pläne für seine SoCs und MCUs der nächsten Generation an. Das Unternehmen zielt auf alle wichtigen Anwendungen im gesamten digitalen Automobilbereich ab, einschließlich Vorabinformationen zu seinem R-Car-SoC der fünften Generation für Hochleistungsanwendungen mit fortschrittlicher In-Package-Chiplet-Integrationstechnologie, die Automobilingenieuren mehr Flexibilität bei der Anpassung bieten soll ihre Entwürfe.

Renesas wies darauf hin, dass Ingenieure die Möglichkeit haben werden, KI-Beschleuniger in einen einzigen Chip zu integrieren, wenn in fortschrittlichen Fahrerassistenzsystemen (ADAS) mehr KI-Leistung erforderlich ist. Das Unternehmen sagte, diese Roadmap sei das Ergebnis jahrelanger Zusammenarbeit und Diskussionen mit Tier-1- und OEM-Kunden, die nach einer Möglichkeit verlangten, die Entwicklung ohne Qualitätseinbußen zu beschleunigen, einschließlich der Entwicklung und Verifizierung der Software, noch bevor die Hardware verfügbar ist.

„Aufgrund des ständig steigenden Bedarfs an mehr Compute-on-Demand und des zunehmenden Bedarfs an höherer Autonomie in den Autos von morgen sehen wir in den kommenden Jahren Herausforderungen bei der Skalierung monolithischer Lösungen und der Erfüllung der Leistungsanforderungen des Marktes“, sagte er Vasanth Waran, Senior Director für SoC Business & Strategies bei Renesas. „Chiplets ermöglichen es, die Rechenlösungen über die Anforderungen des Marktes hinaus zu skalieren.“

Renesas kündigte Pläne zur Gründung eines an Chiplet-basierte Produktfamilie ab 2025 speziell auf den Automobilmarkt ausgerichtet.

Standardschnittstellen ermöglichen eine SoC-Anpassung

Es ist nicht ganz klar, wie viele Überschneidungen es zwischen Standardprozessoren, in denen heute die meisten Chiplets verwendet werden, und Chiplets, die für Automobilanwendungen entwickelt wurden, geben wird. Aber die zugrunde liegenden Technologien und Entwicklungen werden sicherlich aufeinander aufbauen, wenn diese Technologie in neue Märkte vordringt.

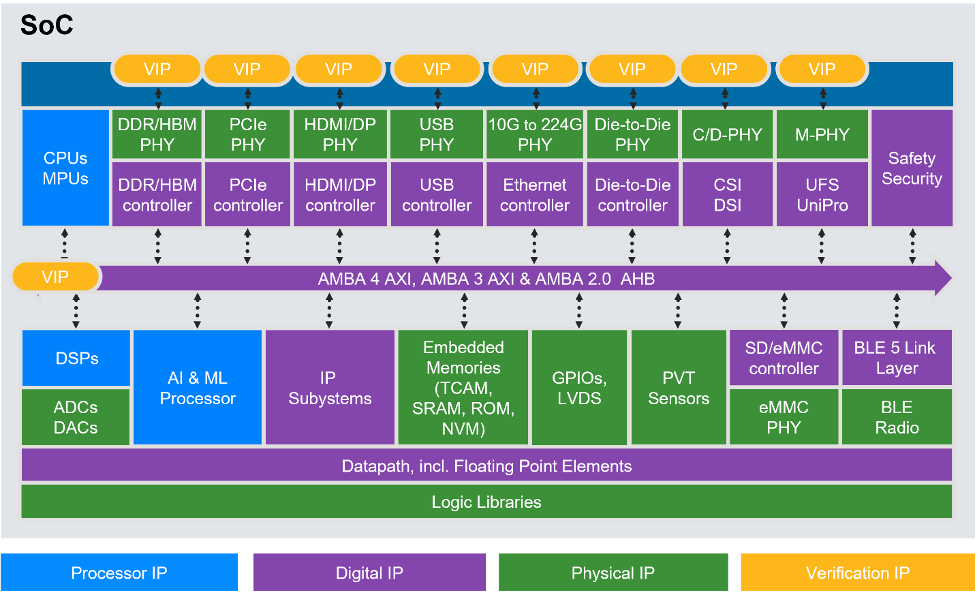

„Ob es sich um einen KI-Beschleuniger oder eine ADAS-Automobilanwendung handelt, Kunden benötigen IP-Blöcke mit Standardschnittstelle“, bemerkte David Ridgeway, Senior Product Manager, IP Accelerated Solutions Group bei Synopsys. „Es ist wichtig, vollständig verifizierte IP-Subsysteme rund um ihre IP-Anpassungsanforderungen bereitzustellen, um die in den SoCs der Kunden verwendeten Subsystemkomponenten zu unterstützen. Wenn ich von Anpassung spreche, ist Ihnen möglicherweise nicht bewusst, wie anpassbar IP im Laufe der letzten 10 bis 20 Jahre geworden ist, sowohl auf der PHY-Seite als auch auf der Controller-Seite. Beispielsweise ist PCI Express von PCIe Gen 3 zu Gen 4 zu Gen 5 und jetzt Gen 6 übergegangen. Der Controller kann so konfiguriert werden, dass er mehrere Bifurkationsmodi mit kleineren Verbindungsbreiten unterstützt, darunter ein x16, zwei x8 oder vier x4. Unser Subsystem-IP-Team arbeitet mit Kunden zusammen, um sicherzustellen, dass alle Anpassungsanforderungen erfüllt werden. Für KI-Anwendungen ist die Signal- und Leistungsintegrität äußerst wichtig, um ihre Leistungsanforderungen zu erfüllen. Fast alle unsere Kunden streben danach, die Grenzen zu überschreiten, um die höchstmögliche Speicherbandbreitengeschwindigkeit zu erreichen, damit ihre TPU viel mehr Transaktionen pro Sekunde verarbeiten kann. Immer wenn es sich bei den Anwendungen um Cloud Computing oder künstliche Intelligenz handelt, wünschen sich Kunden eine möglichst schnelle Reaktionszeit.“

Abb. 1: IP-Blöcke einschließlich Prozessor, Digital, PHY und Verifizierung helfen Entwicklern bei der Implementierung des gesamten SoC. Quelle: Synopsys

Die Optimierung von PPA dient dem obersten Ziel der Effizienzsteigerung und macht Chiplets für Automobilanwendungen besonders attraktiv. Wenn UCIe ausgereift ist, wird erwartet, dass es die Gesamtleistung exponentiell verbessert. UCIe kann beispielsweise eine Shoreline-Bandbreite von 28 bis 224 GB/s/mm in einem Standardpaket und 165 bis 1317 GB/s/mm in einem erweiterten Paket liefern. Dies stellt eine Leistungssteigerung um das 20- bis 100-fache dar. Die Senkung der Latenz von 20 ns auf 2 ns bedeutet eine Verbesserung um das Zehnfache. Ein weiterer Pluspunkt ist die rund zehnmal höhere Energieeffizienz von 10 pJ/b (Standard-Paket) und 10 pJ/b (Advanced-Paket). Der Schlüssel liegt darin, die Schnittstellenentfernung nach Möglichkeit zu verkürzen.

Zur Optimierung von Chiplet-Designs bietet das UCIe-Konsortium einige Vorschläge an:

- Sorgfältige Berücksichtigung architektonischer Schnittlinien (z. B. Chiplet-Grenzen) bei der Planung und Optimierung von Leistung, Latenz, Siliziumfläche und IP-Wiederverwendung. Beispielsweise kann sich die Anpassung eines Chiplets, das einen hochmodernen Prozessknoten benötigt, während die Wiederverwendung anderer Chiplets auf älteren Knoten erforderlich ist, auf Kosten und Zeit auswirken.

- Thermische und mechanische Verpackungseinschränkungen müssen für thermische Verpackungsumschläge, Hotspots, Chiplet-Platzierungen sowie E/A-Routing und Breakouts geplant werden.

- Prozessknoten müssen sorgfältig ausgewählt werden, insbesondere im Kontext des zugehörigen Stromversorgungsschemas.

- Eine Teststrategie für Chiplets und verpackte/zusammengebaute Teile muss im Vorfeld entwickelt werden, um sicherzustellen, dass Siliziumprobleme bereits in der Testphase auf Chiplet-Ebene erkannt werden und nicht erst nach dem Zusammenbau in ein Paket.

Zusammenfassung

Die Idee der Standardisierung von Die-to-Die-Schnittstellen setzt sich schnell durch, aber der Weg dorthin erfordert Zeit, Mühe und viel Zusammenarbeit zwischen Unternehmen, die selten miteinander kommunizieren. Der Bau eines Fahrzeugs erfordert einen bestimmten Automobilhersteller. Der Bau eines Fahrzeugs mit Chiplets erfordert die Zusammenarbeit von Entwicklern, Gießereien, OSATs sowie Material- und Ausrüstungslieferanten.

Automobil-OEMs sind Experten darin, Systeme zusammenzustellen und innovative Wege zur Kostensenkung zu finden. Es bleibt jedoch abzuwarten, wie schnell und effektiv sie ein Ökosystem interoperabler Chiplets aufbauen und nutzen können, um die Designzyklen zu verkürzen, die Anpassung zu verbessern und sich an eine Welt anzupassen, in der die Spitzentechnologie möglicherweise veraltet ist, wenn sie vollständig entwickelt und getestet ist und für Verbraucher verfügbar.

— Ann Mutschler hat zu diesem Bericht beigetragen.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/