IC-Designs verfügen über physikalische Verifizierungsanwendungen wie Layout Versus Schematic (LVS) auf Transistorebene, um sicherzustellen, dass Layout und Schaltpläne gleichwertig sind. Darüber hinaus gibt es einen Electrical Rules Check (ERC) für Verbindungen zu Well-Regionen, der als Soft Check bezeichnet wird. Die Verbindungen zu allen Geräten müssen möglichst konsistente Spannungssignale aufweisen. Daher sollte der Pfad durch die Metallschichten verlaufen, um den Widerstand und Faktoren wie IR-Abfall zu reduzieren. Das Erkennen von Verbindungen hielt andere Materialien – wie Wells – für unerlässlich. Soft-Checks sind die am häufigsten eingesetzte Methode, um diese Situation zu erkennen. Der Kaliber Die Produktlinie von Siemens ist das beliebteste Tool für DRC- und LVS-Prüfungen. Deshalb habe ich einen technischen Artikel von Terry Meeks gelesen, um mehr über Soft Checks zu erfahren.

Die Verbindung zweier Metallschichten in einem IC-Layout erfordert eine präzise Ausrichtung beider Metallschichten und der Via-Schicht. Hier ist ein Vergleich unter Verwendung einer Seitenansicht und einer Ansicht von oben, wobei das erste Beispiel nicht verbunden ist, da Metall1 und Metall 2 sich nicht überlappen, während das zweite Beispiel ordnungsgemäß verbunden ist.

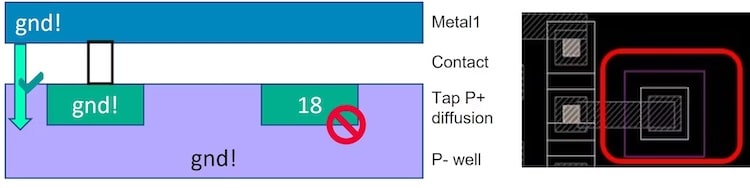

Wir möchten, dass unser ERC-Tool bei Softchecks Bohrlochkonnektivitätsfehler erkennt, damit diese behoben werden können. Das folgende IC-Layout weist einen Well-Konnektivitätsfehler auf und wird in der Seitenansicht dargestellt, wobei das als Gnd bezeichnete Metal1-Signal mit einem Diffusionsbereich verbunden ist, der als Tap-Diffusion bezeichnet wird. Auf der rechten Seite befindet sich eine weitere Metal1-Schicht mit einer Abzweigungsdiffusion, aber diese Konnektivität erzeugt einen hochohmigen Pfad im Rwell zu Gnd und wird von der Soft-Prüfung als Fehler gekennzeichnet.

Ein weiteres Beispiel für einen Soft-Connectivity-Fehler tritt im IC-Layout unten auf, wo wir nur einen Namen pro Polygon anwenden können. Das digitale Stromnetz VDD kann nicht mit dem analogen Stromnetz AVDD koexistieren, und wir müssen diese in zwei Formen aufteilen. Soft Checks helfen dabei, diese Probleme zu erkennen.

Das richtige Layout eines IC-Layouts mit sowohl digitalen als auch analogen Netzteilen kann ziemlich komplex werden, daher ist es umso wichtiger, Soft-Checks durchzuführen.

Soft Checks sind während Ihrer LVS-Läufe und mit enthalten Kaliber nmLVS Es gibt einen Bericht über die Soft-Check-Ergebnisse, der dann mit dem angezeigt werden kann Kaliber RVE Zuschauer.

Wenn Sie auf die RVE-Ergebnisse klicken, erfahren Sie, welche Zelle den Soft-Check-Fehler aufweist, welche Netznamen, Ober- und Unternamen und andere Eigenschaften vorliegen. Diese Informationen helfen dabei, genau zu bestimmen, was im IC-Layout korrigiert werden muss. Wenn Sie für einen Soft-Check-Fehler auf eine niedrigere Ebene wie einen PWell klicken, wird die Geometrie in Gelb angezeigt.

Für denselben Soft-Check-Fehler wird beim Klicken auf die obere Ebene Folgendes angezeigt:

Während des Debuggens können Sie auch alle Formen der oberen Ebene anzeigen. Die grünen Formen sind die ausgewählten Nettoformen der oberen Ebene, während Gelb die abgelehnte Nettoform der oberen Ebene ist.

Das Debuggen von Soft-Check-Fehlern mit RVE erfordert das Klicken auf die Konnektivität ausgewählter und abgelehnter Netze. Ein Netzinformationsfenster zeigt Details an, z. B. welche Ebenen beteiligt sind und ob Formen keine Konnektivität aufweisen. Wenn Sie sich ansehen, welche Ports mit einem Netz verbunden sind, können Sie feststellen, ob VDD- oder GND-Fehler fehlen. Dieses Beispiel zeigt, dass Netz 18 abgelehnt wird, da die Verbindung zu Metal1 fehlt.

Zusammenfassung

LVS-Prüfungen sind obligatorisch, um sicherzustellen, dass ein IC ein fehlerfreies Layout aufweist, und Soft-Checks sind Teil Ihrer LVS-Prüfungen. In ihrem Calibre nmLVS-Tool gibt es einen bewährten Debugging-Ablauf von Siemens, der RVE verwendet, um Layout-Designern dabei zu helfen, Soft-Check-Fehler schnell zu identifizieren, sodass Designer Korrekturen vornehmen und erneut überprüfen können, bis alle Prüfungen erfolgreich sind. Siemens hat einen Fachartikel zum Online-Lesen verfasst, Erkennen und Debuggen von Soft-Check-Konnektivitätsfehlern.

Verwandte Blogs

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/342526-soft-checks-are-needed-during-electrical-rule-checking-of-ic-layouts/