Der MOSFET-Gate-Widerstand ist ein sehr wichtiger Parameter, der viele Eigenschaften von MOSFETs und CMOS-Schaltungen bestimmt, wie zum Beispiel:

• Schaltgeschwindigkeit

• RC-Verzögerung

• Fmax – maximale Schwingungsfrequenz

• Gate (thermisches) Rauschen

• Serienwiderstand und Qualitätsfaktor in MOS-Kondensatoren und Varaktoren

• Schaltgeschwindigkeit und Gleichmäßigkeit bei Leistungs-FETs

• Viele andere Geräte- und Schaltungseigenschaften

Viele akademische und Forschungsarbeiten wurden über den Gate-Widerstand geschrieben. Für die praktische Arbeit von IC-Designern und Layoutern wurden jedoch viele wichtige Dinge nicht besprochen oder erklärt, zum Beispiel:

• Wird der Gate-Widerstand von SPICE-Modellen oder von parasitären Extraktionswerkzeugen gehandhabt?

• Wie gehen parasitäre Extraktionswerkzeuge mit dem Gate-Widerstand um?

• Wie kann man den Gate-Widerstand aus dem Layout oder aus der extrahierten Netzliste nach dem Layout auswerten?

• Wie kann man feststellen, ob der Gate-Widerstand durch den „intrinsischen“ Gate-Widerstand (Gate-Poly) oder durch das Routing der Gate-Metallisierung begrenzt ist, und was sind die kritischsten Schichten und Polygone?

• Wird der Gate-Verteilungseffekt (Faktoren von 1/3 und 1/12 für einfach- und doppelt kontaktiertes Poly) im IC-Designfluss (in PDK) erfasst?

• Wird die vertikale Gate-Widerstandskomponente in Gießerei-PDKs erfasst?

• Soll das Gate breiter oder schmaler gemacht werden, um den Gate-Widerstand zu verringern?

• Was ist der Unterschied zwischen dem Umgang mit Gate-Widerständen in PDKs für HF und normalen MOSFETs oder p-Zellen?

Der Zweck dieses Artikels ist es, diese Fragen zu entmystifizieren und einige Einblicke für IC-Design- und Layout-Ingenieure zu geben, um den Gate-Widerstand in ihren Designs besser zu verstehen.

Definition und Messung des Gate-Widerstands

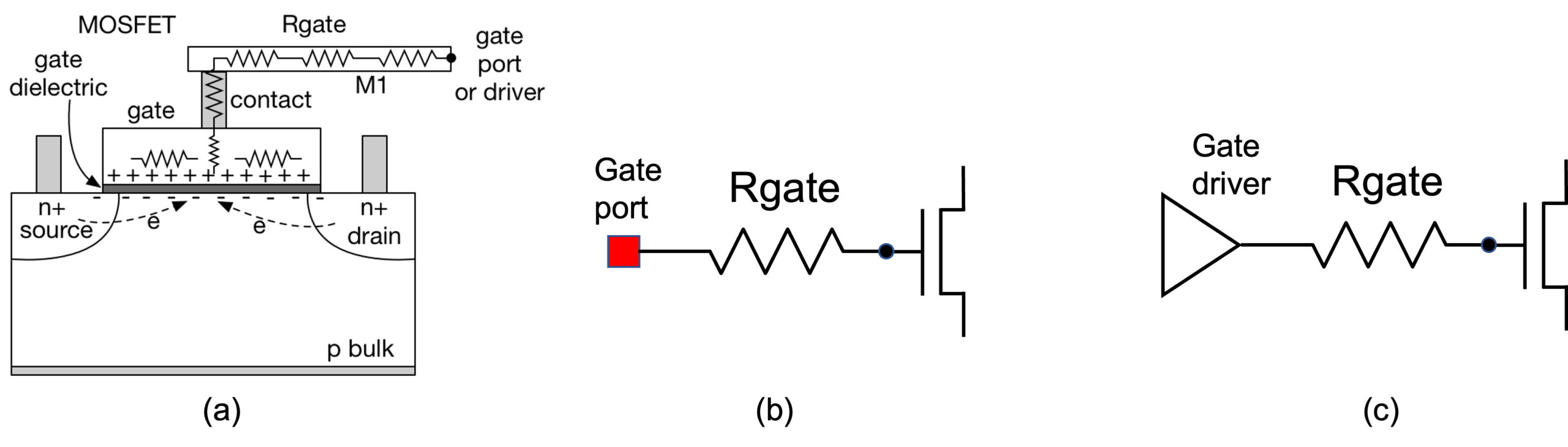

Der Gate-Widerstand ist ein „effektiver“ Widerstand vom Ansteuerpunkt (Gate-Port oder Gate-Treiber) zu den Pins der MOSFET-Gate-Instanz – siehe Abb. 1. (Beispiel-Pin ist ein Verbindungspunkt zwischen einem Terminal des SPICE-Modells und einem resistiven Netzwerk, einem Netz).

Die Einfachheit des Schemas in Abbildung 1 kann jedoch sehr irreführend sein. Gate-Netze können sehr groß sein, viele Ansteuerpunkte, viele (Dutzende von) Schichten (Metall und Via), Millionen von Polygonen und bis zu Millionen von Gate-Instanz-Pins (Verbindungspunkte für Gate-Terminals des SPICE-Modells) enthalten – siehe Figur 2.

Das Gate-Netzwerk bildet ein großes verteiltes System mit einem oder mehreren Fahrpunkten und vielen Zielpunkten.

Sehr oft sieht und verhält sich das Gate-Netz wie ein riesiges, reguläres Taktnetzwerk, das die Gate-Spannung an einen FET verteilt.

Das Ableiten eines äquivalenten, effektiven Gate-Widerstands für ein so großes und komplexes System ist keine einfache und unkomplizierte Aufgabe. Die SPICE-Schaltungssimulation gibt den Gate-Widerstandswert nicht explizit an.

Die Kenntnis des Werts des Gate-Widerstands ist sehr nützlich, um die Schaltgeschwindigkeit, Verzögerung, Rauschen, Fmax und andere Eigenschaften abzuschätzen, um festzustellen, ob die Eigenschaften innerhalb der Spezifikation liegen. Auch die Kenntnis der Beiträge zum Gate-Widerstand – nach Schicht und nach Layout-Polygonen – ist sehr nützlich, um die Optimierungsbemühungen des Layouts zu steuern.

Handhabung des Gate-Widerstands durch parasitäre Extraktionswerkzeuge

Um den Gate-Widerstand im IC-Design-Flow zu verstehen, ist es wichtig zu wissen, wie parasitäre Extraktionswerkzeuge ihn behandeln und modellieren.

Alle branchenüblichen Werkzeuge zum Extrahieren von Parasiten handhaben den Gate-Widerstand und seine Extraktion ähnlich. Im Layout wird die MOS-Gate-Struktur durch eine 2D-Maske dargestellt, die traditionell „Poly“ genannt wird – obwohl das Material durch einen komplexen Gate-Metallstapel gebildet werden kann und eine komplexe 3D-Struktur haben kann.

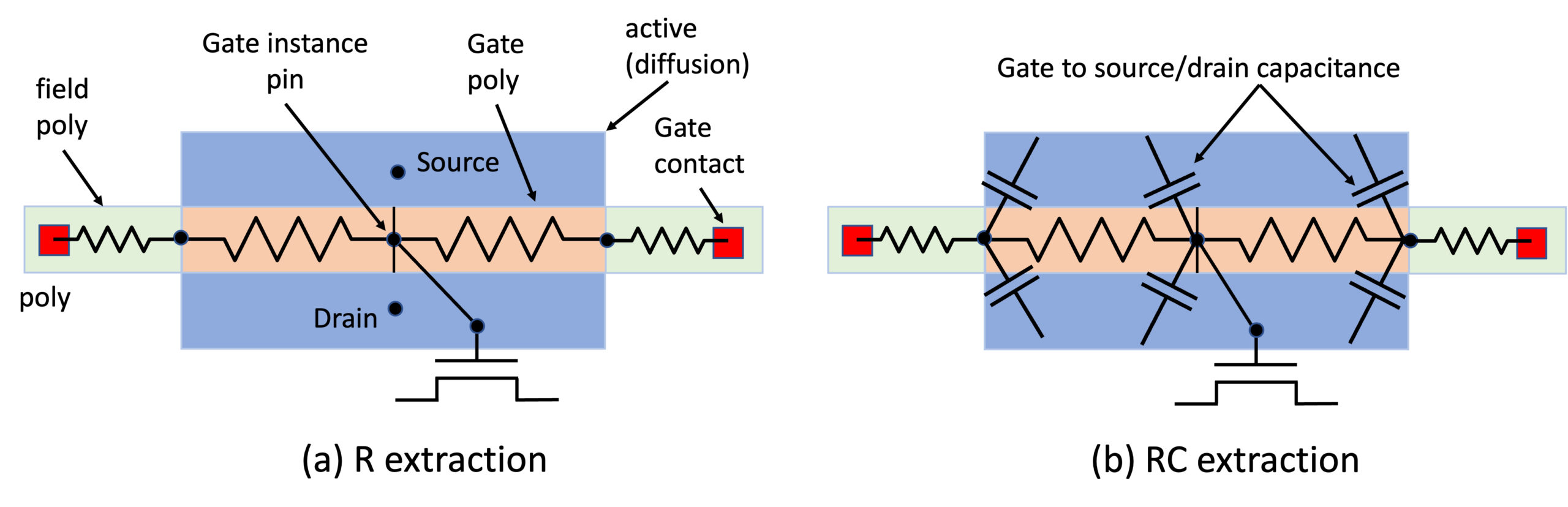

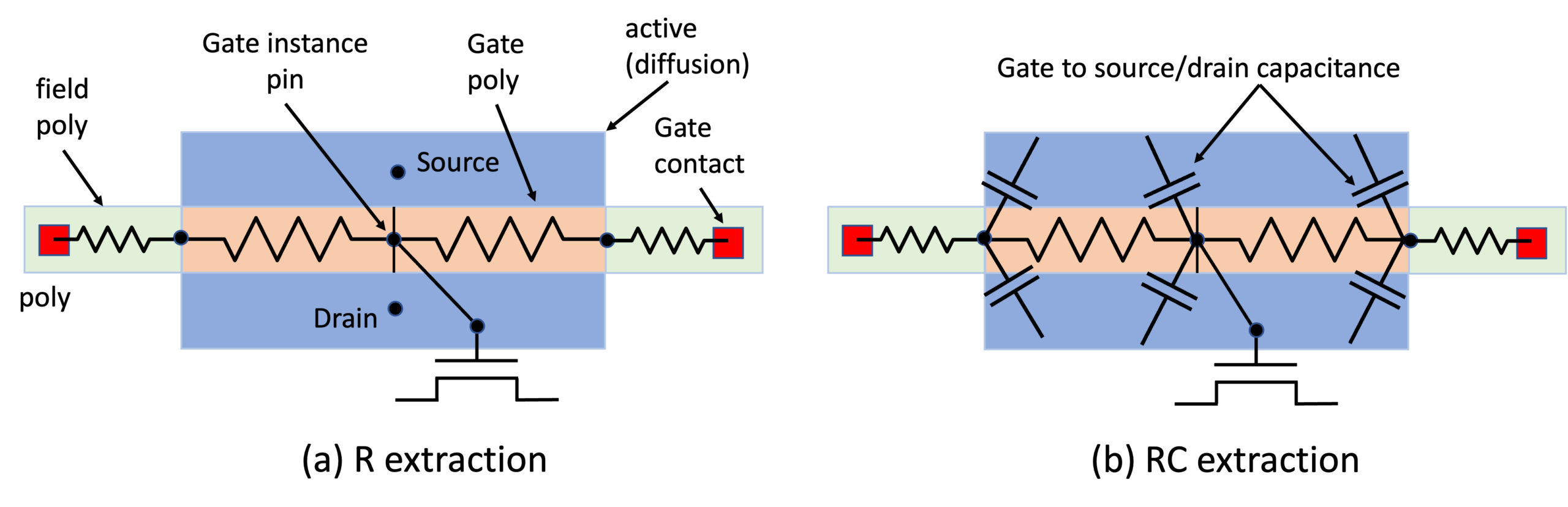

Sie brechen die Polylinie am Schnittpunkt mit der aktiven (Diffusions-)Schicht und unterteilen sie in „Gate-Poly“ (Poly über aktiv) und „Feld-Poly“ (Poly außerhalb aktiv), wie in Abbildung 3 gezeigt.

Das Gate-Poly ist auch am Mittelpunkt gebrochen. Der Gate-Instanz-Pin des MOSFET (SPICE-Modell) ist mit dem Mittelpunkt des Gate-Poly verbunden. Gate-Poly wird durch zwei parasitäre Widerstände beschrieben, die die Bruchstellen verbinden. Ein genaueres Modell des Gate-Poly mit zwei positiven und einem negativen Widerstand kann im PDK aktiviert werden, aber einige Foundries ziehen es vor, es nicht zu verwenden (siehe nächster Abschnitt zum Gate-Delta-Modell).

Parasitäre Widerstände, die das Feld-Poly darstellen, sind mit den Gate-Kontakten oder mit MEOL-Schichten (Middle-End-Of-Line) und weiter mit oberen Metallschichten verbunden.

Die extrinsische parasitäre MOSFET-Kapazität zwischen Gate-Poly und Source/Drain-Diffusion und Kontakten wird durch parasitäre Extraktionswerkzeuge berechnet und den Knoten der Widerstandsnetzwerke zugewiesen. Verschiedene Extraktionswerkzeuge tun dies unterschiedlich – einige Werkzeuge verbinden diese parasitären Kapazitäten mit dem Mittelpunkt des Gate-Poly, während einige andere Werkzeuge sie mit den Endpunkten der Gate-Poly-Widerstände verbinden. Die Details der parasitären Kapazitätsverbindung zum Gate-Widerstandsnetzwerk können einen großen, signifikanten Einfluss auf die Transienten- und AC-Reaktion haben, insbesondere in fortgeschrittenen Knoten (16 nm und niedriger), wo der parasitäre Gate-Widerstand enorm ist.

Diese Details können in der DSPF-Datei eingesehen werden, werden aber normalerweise nicht in der offenen Literatur oder in der Foundry-PDK-Dokumentation diskutiert. Die visuelle Überprüfung von Text-DSPF-Dateien ist mühsam und erfordert einige Fachkenntnisse. Spezialisierte EDA-Tools (z. B. ParagonX [3]) können verwendet werden, um die Konnektivität von RC-Netzwerken für Post-Layout-Netzlisten (DSPF, SPEF) zu visualisieren, sie zu untersuchen (R- und C-Werte anzuzeigen und zu überprüfen), elektrische Analysen durchzuführen und andere nützliche Dinge zu tun .

Delta-Gate-Modell

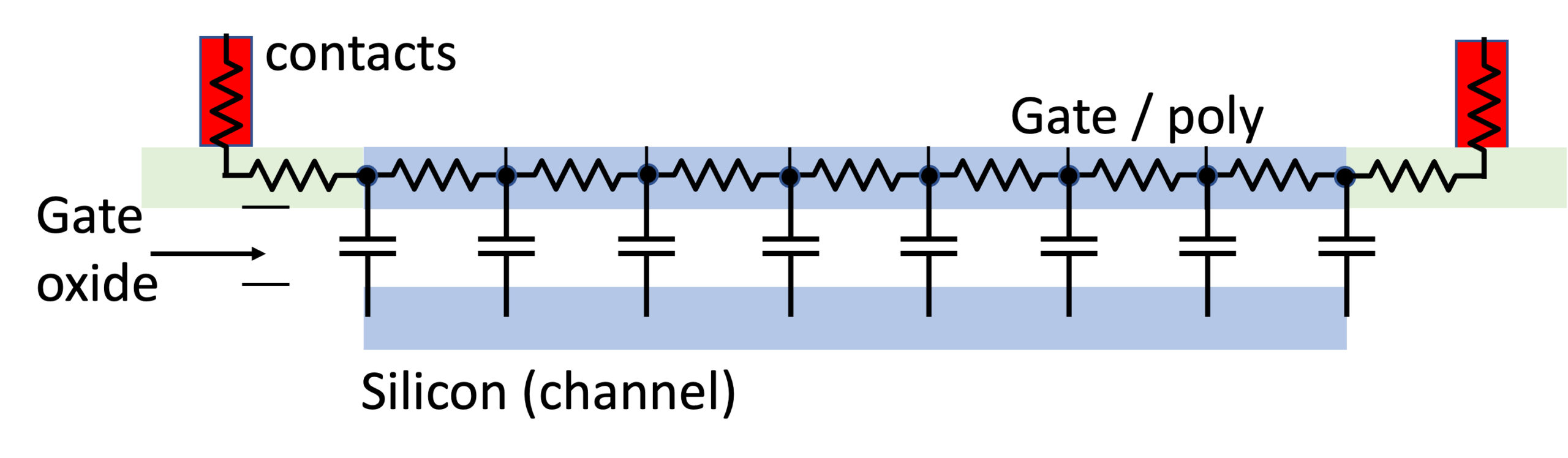

Das MOSFET-Gate bildet ein großes verteiltes RC-Netzwerk entlang der Gate-Breite – dargestellt in Abbildung 4.

Dieses verteilte Netzwerk hat ein anderes Wechselstrom- und Einschwingverhalten als eine einfache konzentrierte Ein-R- und Ein-C-Schaltung. Es wurde gezeigt [2-3], dass sich ein solches RC-Netzwerk ungefähr genauso verhält wie ein Netzwerk mit einem R- und einem C-Element, wobei C die Gesamtkapazität ist und R = 1/3 * W / L * rsh für einseitig verbundenes Poly und R=1/12 * W/L * rsh für doppelseitig verbundenes Poly. Diese Koeffizienten – 1/3 und 1/12 – ermöglichen effektiv ein genaues Modell reduzierter Ordnung für das Gate, wodurch eine große Anzahl von R- und C-Elementen auf zwei (oder drei) Widerstände und einen Kondensator reduziert wird.

Um diese Koeffizienten in einer Standard-RC-Netzliste (SPICE-Netzliste oder DSPF) zu aktivieren, haben einige kluge Köpfe ein sogenanntes Gate-Delta-Modell erfunden – bei dem ein Gate durch zwei positive und einen negativen Widerstand beschrieben wird – siehe Abbildung 5.

Einige SPICE-Simulatoren haben Probleme mit negativen Widerständen, das ist möglicherweise der Grund, warum dieses Modell keine breite Akzeptanz gefunden hat. Einige Foundries und PDKs unterstützen das Delta-Gate-Modell, andere nicht.

Viele Leute sind überrascht, wenn sie negative Widerstände in DSPF-Dateien sehen. Wenn diese Widerstände neben dem Gate-Instanz-Pin liegen, sind sie Teil der Gate-Delta-Schaltung.

Verteilte Effekte entlang der Gate-Länge (in Richtung von Source zu Drain) werden normalerweise auf der Ebene der Schaltungsanalyse aufgrund eines kleinen Werts der Gate-Länge im Vergleich zur Gate-Breite ignoriert.

Auswirkung von Interconnect-Parasiten auf den Gate-Widerstand

In „alten“ Technologien hatten Metallverbindungen (Metalle und Vias) einen sehr niedrigen Widerstand, und der Gate-Widerstand wurde von Gate-Poly dominiert. Die Analyse und Berechnung des Gate-Widerstands war sehr einfach.

Bei den neuesten Technologien (z. B. 16 nm und niedriger) haben Zwischenverbindungen einen sehr hohen Widerstand und können einen erheblichen Teil (50 % oder mehr) zum Gate-Widerstand beitragen. Je nach Layout kann der Gate-Widerstand erhebliche Beiträge von beliebigen Schichten haben – von Geräten (Gate-Poly, Feld-Poly), MEOL oder BEOL.

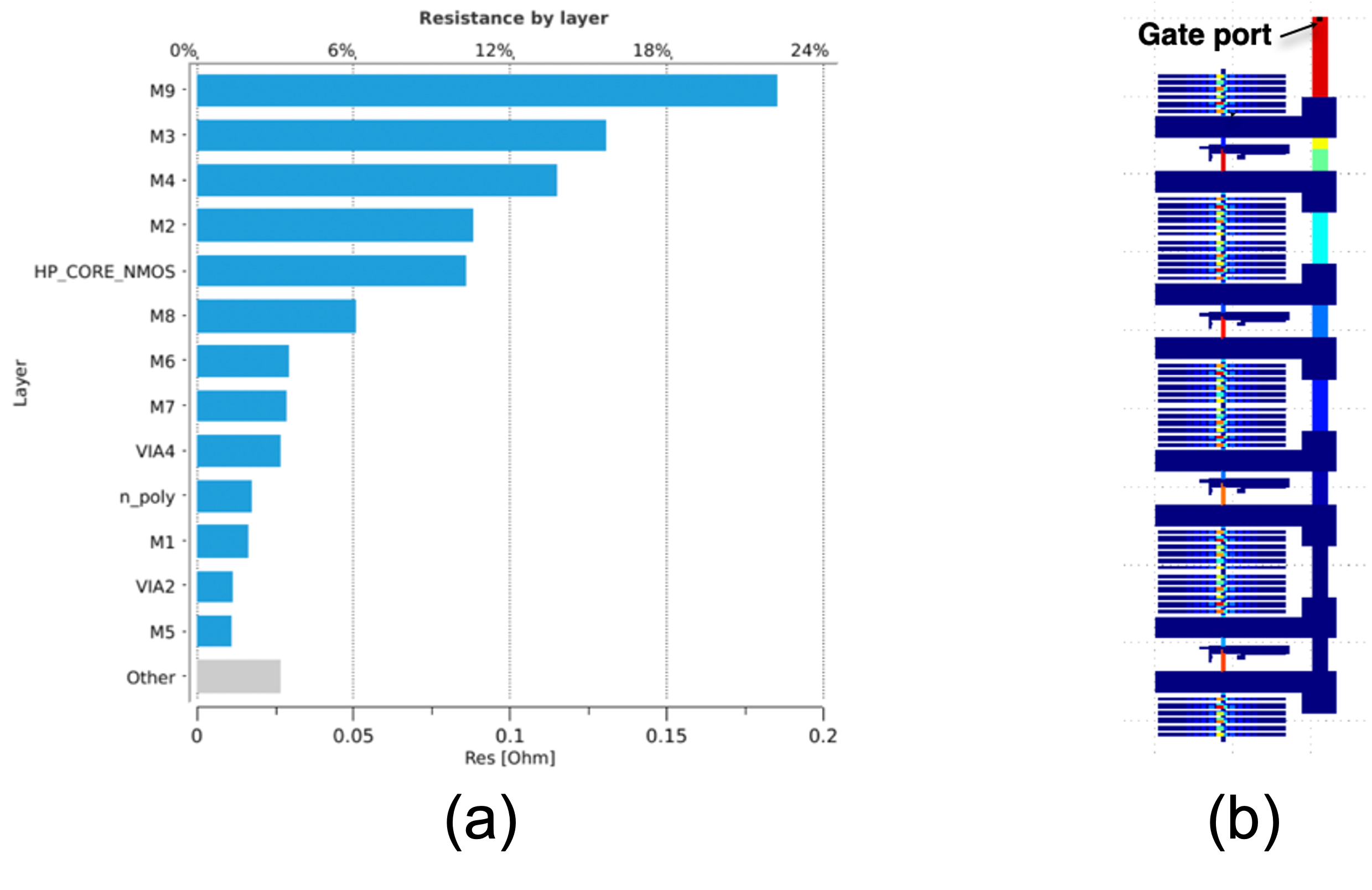

Abbildung 6 zeigt die Ergebnisse der Gate-Widerstandssimulation mit ParagonX [3]. Pareto-Diagramm mit Widerstandsbeiträgen nach Schicht hilft bei der Identifizierung der wichtigsten Schichten für den Gate-Widerstand. Die Visualisierung der Beiträge von Layout-Polygonen zum Gate-Widerstand weist sofort auf Engpässe, Engpässe für den Gate-Widerstand hin, was sehr nützlich ist, um Bemühungen zur Layout-Optimierung zu leiten.

Gate-Widerstand in FinFETs

Bei planaren MOSFETs hat das Gate eine sehr einfache planare Struktur, und der Stromfluss im Gate ist eindimensional entlang der Richtung der Gatebreite.

Bei FinFET-Technologien wickelt sich das Gate um sehr hohe Siliziumlamellen und hat daher eine sehr komplizierte 3D-Struktur. Ferner wird das Gate-Material basierend auf der Austrittsarbeit ausgewählt, um die Schwellenspannung abzustimmen (die Schwellenspannung in FinFETs wird nicht durch die Kanaldotierung, sondern durch Gate-Materialien abgestimmt). Diese Materialien haben einen sehr hohen Widerstand, viel höher als angefordertes Poly (das einen typischen Flächenwiderstand von ~10 Ohm/sq hat). Das Gate kann aus mehreren Schichten bestehen – einer Grenzschicht mit Silizium und einer oder mehreren Schichten darüber.

All diese Details werden den IC-Designern und Layoutern jedoch abstrahiert, und sie sehen übliche Polygone für „Poly“ und für „Aktiv“ – was die Designarbeit erheblich erleichtert.

Handshake zwischen SPICE-Modell und parasitärer Extraktion

Im Allgemeinen berücksichtigen sowohl SPICE-Modelle als auch parasitäre Extraktionswerkzeuge den Gate-Widerstand. Die parasitäre Extraktion gilt als genauere Methode zur Berechnung parasitärer R- und C-Werte um die Geräte herum, da sie (im Gegensatz zu SPICE) das Layout „kennt“.

Um Doppelzählungen von parasitären Widerständen und Kapazitäten (im SPICE-Modell und bei der parasitären Extraktion) zu vermeiden, gibt es einen Handshake-Mechanismus zwischen der SPICE-Modellierung und der parasitären Extraktion, basierend auf speziellen Instanzparametern.

Reguläres Gerät im Vergleich zu kompakten RF-Pcell-Modellen

Reguläre MOSFET-SPICE-Modelle beschreiben den Gate-Widerstand für hohe Frequenzen, hohe Schaltgeschwindigkeiten oder für HF- oder Rauschleistung nicht genau genug. Um eine hohe Simulationsgenauigkeit zu ermöglichen, empfehlen die Gießereien in der Regel die Verwendung von HF-P-Zellen mit fester Größe, die eine Abschirmung (Schutzringe und Metallkäfige) enthalten und die durch aus Messungen abgeleitete Modelle mit hoher Genauigkeit beschrieben werden. Diese HF-P-Zellen haben jedoch eine viel größere Fläche als Standard-MOSFETs, und viele Designer ziehen es vor, Standard-MOSFETs zu verwenden, um die Fläche zu reduzieren.

Vertikale Komponente des Gate-Widerstands

Bei „alten“ Technologien (vor 16 nm) wurde der Gate-Widerstand vom Seitenwiderstand dominiert. In fortgeschrittenen Technologien führen jedoch mehrere Grenzflächen zwischen Gate-Materialschichten zu einem großen vertikalen Gate-Widerstand. Dieser Widerstand ist umgekehrt proportional zur Fläche des Gate-Poly. Er kann als zusätzlicher Widerstand modelliert werden, der den Gate-Instanz-Pin mit dem Mittelpunkt des Gate-Poly verbindet – siehe Abbildung 7(a). Wenn das Gate schmaler wird (geringere Anzahl von Finnen), sinkt folglich der Gate-Widerstand, steigt aber bei sehr kleinen Gate-Breiten an. Es zeigt ein charakteristisches nicht-monotones Verhalten, wie in Abbildung 7(b) zu sehen ist. Die alte Faustregel „der schmalere Anschnitt hat einen geringeren Anschnittwiderstand“ funktioniert nicht mehr. Designer und Layouter müssen die optimale (nicht minimale) Gate-Breite (Anzahl der Finnen) auswählen, um den Gate-Widerstand zu minimieren.

![Figure7 (a) Gate-Modell, das den vertikalen Gate-Widerstand berücksichtigt, und (b) gemessener und simulierter Gate-Widerstand gegenüber der Anzahl der Finnen (Ref. [2]).](https://zephyrnet.com/wp-content/uploads/2023/05/gate-resistance-in-ic-design-flow-6.jpg)

Je nach Technologie, PDK und Gießerei kann der vertikale Gate-Widerstand in die parasitäre Extraktion einbezogen werden oder nicht. Es ist sehr einfach, dies in der DSPF-Datei zu überprüfen – wenn der Gate-Instanz-Pin direkt mit der Mitte des Gate-Poly verbunden ist – wird der vertikale Widerstand nicht berücksichtigt. Wenn es durch einen positiven Widerstand mit der Mitte des Gate-Poly verbunden ist, repräsentiert dieser Widerstand den vertikalen Gate-Widerstand.

Technologietrends

Mit der Technologieskalierung steigen sowohl die Gate-Widerstände als auch die Verbindungswiderstände erheblich – um bis zu ein oder zwei Größenordnungen. Infolgedessen werden die Details des Layouts, die für den Gate-Widerstand in älteren Knoten nicht wichtig waren, in fortgeschrittenen Knoten sehr wichtig.

Andere MOSFET-Gate-ähnliche Strukturen

Während sich die Diskussion des Gate-Widerstands in diesem Artikel auf MOSFETs konzentriert, gelten die gleichen Argumente und Ansätze auch für andere verteilte Systeme, die vom Gate oder von Gate-ähnlichen Systemen gesteuert werden, wie zum Beispiel:

• IGBTs (Insulated Gate Bipolar Transistors)

• Entkopplungskondensatoren

• MOS-Kondensatoren

• Varaktoren

• Deep-Trench- und andere MIM-ähnliche integrierte Kondensatoren

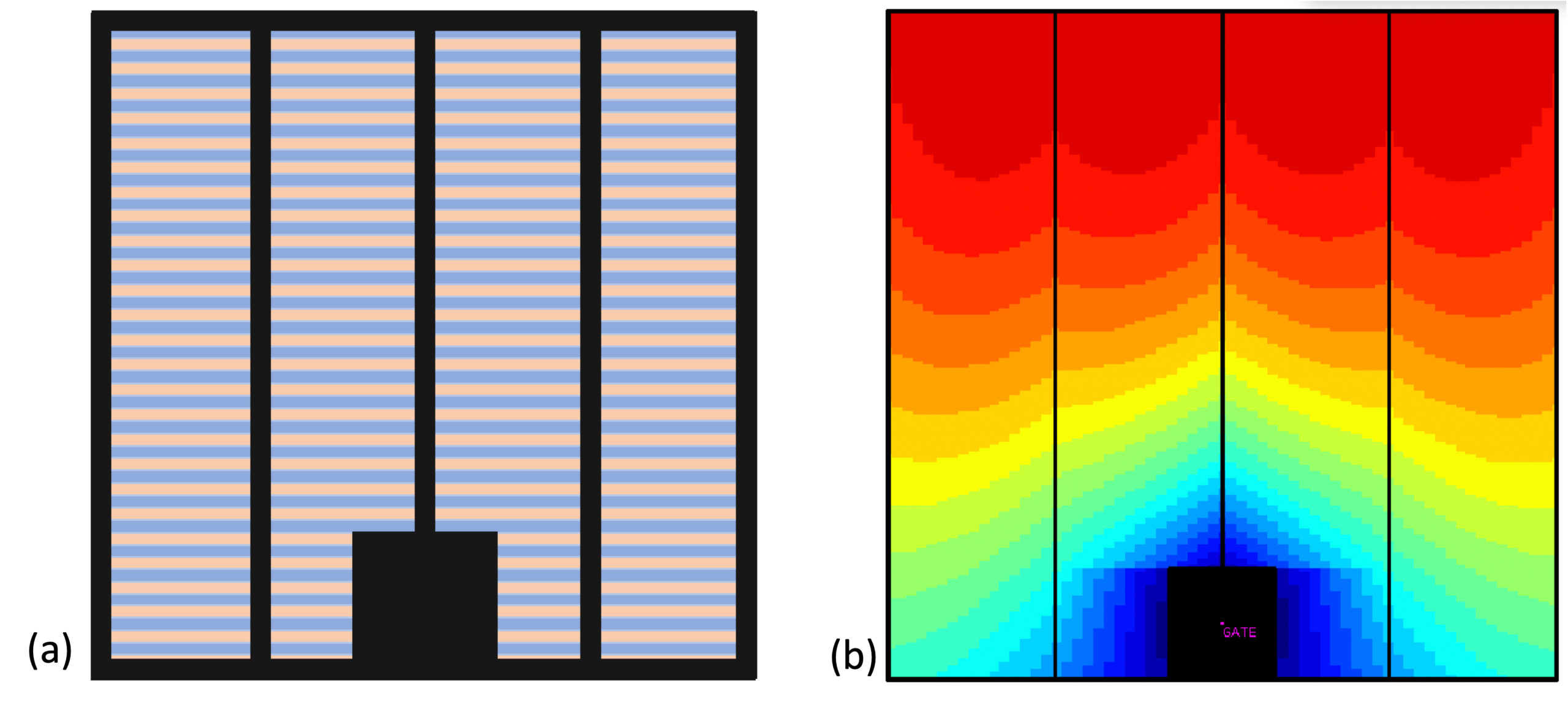

Abbildung 8 zeigt eine Gate-Struktur eines vertikalen MOSFET und die Verteilung der Gate-Verzögerung über die Gerätefläche, simuliert mit ParagonX [3].

Bibliographie

1. B. Razavi, et al., „Einfluss des verteilten Gate-Widerstands auf die Leistung von MOS-Geräten“, IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 41, S. 750-754, 11 1994.

2. AJSholten et al., „FinFET compact modeling for analog and RF applications“, IEDM'2010, S. 190.

3. ParagonX-Benutzerhandbuch, Diakopto Inc., 2023.

Lesen Sie auch:

Ihre symmetrischen Layouts zeigen Diskrepanzen in SPICE-Simulationen. Was ist los?

Schnelle EM/IR-Analyse, eine neue EDA-Kategorie

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoAiStream. Web3-Datenintelligenz. Wissen verstärkt. Hier zugreifen.

- Die Zukunft prägen mit Adryenn Ashley. Hier zugreifen.

- Quelle: https://semiwiki.com/eda/diakopto/328285-gate-resistance-in-ic-design-flow/