Während der GOMACTech Bei der Konferenz, die letzte Woche in South Carolina stattfand, hatte ich einen Zoom-Anruf mit Deepak Shankar, Gründer und VP Technology bei Mirabilis Design Inc., um Fragen zu stellen und eine Live-Demo anzusehen VisualSim – eine Modellierungs-, Simulations-, Erkundungs- und Kooperationsplattform zur Entwicklung von Elektronik und SoCs. Was VisualSim so besonders macht, ist, dass es im Paket mit etwa 500 gebrauchsfertigen High-Level-IP-Blöcken geliefert wird, darunter 35 ARM-Prozessoren, etwa 100 Prozessoren und über 30 verschiedene Verbindungen. Benutzer von VisualSim verbinden diese IP-Blöcke schnell visuell miteinander, um ihre Systeme inklusive Netzwerken zu erstellen. Ein Automobildesigner kann mit VisualSim das gesamte Netzwerk modellieren, einschließlich 5G-Kommunikation, Ethernet, SDA und OTA-Updates.

Ein High-Level-Modell ermöglicht die schnellste Erkundung der Architektur und das Eingehen architektonischer Kompromisse, lange bevor die Implementierung mit RTL-Code überhaupt beginnt. Sie können komplexe Aktivitäten wie einen Bus, Speicher und sogar Cache modellieren und Dinge wie End-to-End-Verzögerungen und Latenz messen. Ingenieure können messen, wie hoch ihr Cache-Hit/Miss-Verhältnis ist und was mit Anfragen an L2-Caches passiert. Alle gängigen Netzwerkprotokolle werden modelliert: AXI, CHI, CMN600, Arteris NOC, UCIe usw.

Mit diesem Modellierungsansatz kann ein Architekt ein SoC, ein komplettes Flugzeug- oder Automobilsystem modellieren und dann mit der Messung seiner Leistung beginnen, um zu sehen, ob es die Anforderungen erfüllt. VisualSim ist ein Multi-Domain-Simulator, der Analog-, Software-, Stromversorgungs-, Digital- und Netzwerksysteme in einem einzigen Modell integrieren kann.

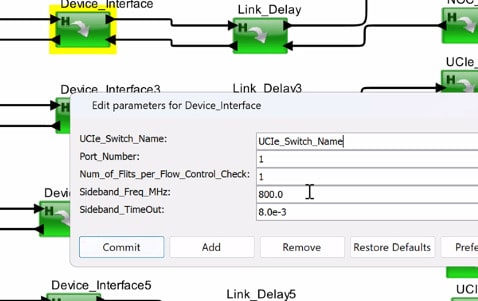

Für die Live-Demo zeigte mir Deepak ein Chiplet-basiertes Design, das separate Chiplets für DSP, GPU, AI-Prozessor und CPU enthielt, die alle über UCIe miteinander verbunden waren, und jeder IP-Block wurde parametrisiert, um eine individuelle Anpassung und Erkundung zu ermöglichen.

In den UCIe-Block wurde eine IP-Adresse namens UCIe-Switch eingefügt, und ein Benutzer kann diesen Block mit fünf Parametern auf hoher Ebene anpassen.

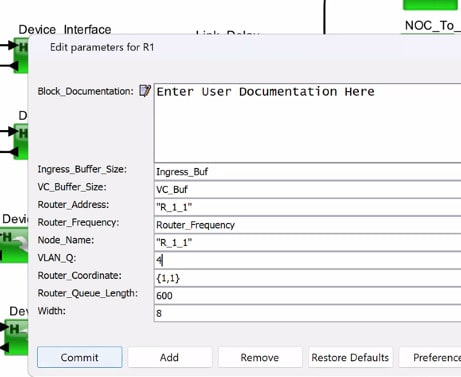

Ein Router-IP-Block hatte 10 Parameter zur Anpassung.

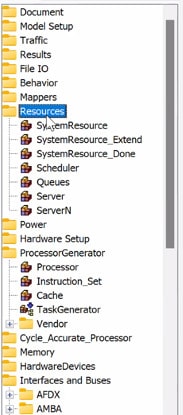

Um jeden IP-Block zu finden, gab es auf der linken Seite der GUI eine scrollbare Liste mit jeder IP-Familie in der Bibliothek. In Sekundenschnelle können Sie eine IP durchsuchen, auswählen und mit der Anpassung beginnen.

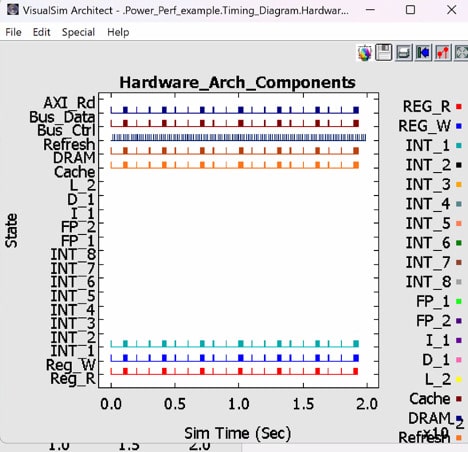

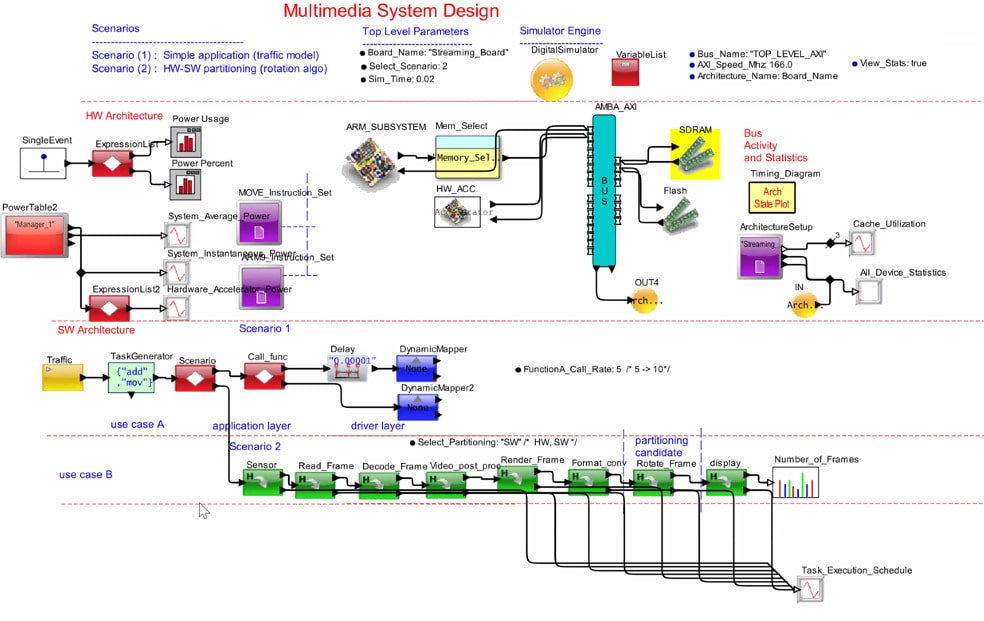

In VisualSim verbinden Sie jede IP im Datenfluss und bleiben dabei auf einem hohen Niveau. Bei der nächsten Live-Demo ging es um den Entwurf eines Multimedia-Systems. Die Simulation von 20 ms dauerte etwa 15 Sekunden an der Wand und lief auf einem Laptop. Während die Simulation läuft, können Sie die Systemleistung als Momentanleistung anzeigen, die Pipeline-Auslastung, die Cache-Auslastung und die Speichernutzung messen und sogar ein Zeitdiagramm anzeigen. Diese Echtzeitsimulation löste 7.5 Millionen Ereignisse aus und der Kunde baute dieses Modell, einschließlich des gesamten SoC, in weniger als zwei Wochen.

Ein weiteres Kundenbeispiel, das Deepak erwähnte, umfasste 45 Master und wurde in etwa 4 Wochen fertiggestellt und vollständig getestet.

Sie können einen Blick in jeden der IP-Blöcke werfen und Metriken wie „Bestanden/Nicht bestanden“ analysieren und dann verstehen, warum der Fehler fehlgeschlagen ist. Es gibt sogar eine KI-Engine, die dabei hilft, Daten effizienter zu analysieren und beispielsweise einen Pufferüberlauf zu finden, der einen Fehler verursacht hat. Während Ihr Modell ausgeführt wird, werden Analysen erfasst, um die Systemleistung zu messen und architektonische Engpässe zu identifizieren.

VisualSim wird zweimal pro Jahr aktualisiert, und dann gibt es Patch-Updates, wenn neue IP-Blöcke hinzugefügt werden. Ein Architekt definiert Anforderungen in einer Excel-Datei mit Metriken wie Latenzgrenzen und Pufferbelegung.

Benutzer von VisualSim können den Bereich der Nutzlastgröße in Bezug auf Bytes, Geschwindigkeitsbereiche und bevorzugte Werte definieren. Ihr Systemmodell kann die Kombinationen durchsuchen, um den besten Parametersatz zu finden. Der Simulator versteht es sogar, die Mindest-, Höchst- und Vorzugswerte zu ermitteln. Sie können festlegen, welche Systemparameter untersucht werden. Anschließend wurde eine Multimedia-Systemdemo gezeigt und anschließend live simuliert.

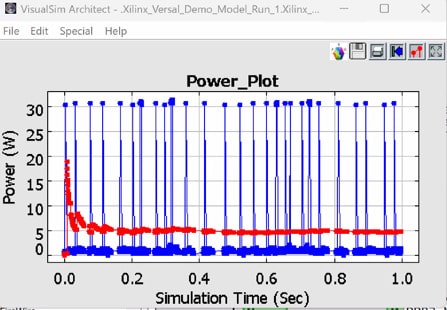

Für einen FPGA-Block wählen Sie den Anbieter und die Teilenummer aus und können dann die Latenz für jede Aufgabe und die Kanalstatistik des NOC sehen, nachdem eine Simulation ausgeführt wurde. Bei Verwendung von Xilinx Versal-Teilen wurde ein Leistungsdiagramm für eine Betriebssekunde angezeigt.

Alle Live-Demos wurden auf einem Windows-Laptop ausgeführt. Weitere unterstützte Betriebssysteme sind: Unix, Mac. Der Betrieb von VisualSim erfordert eine minimale HW-Infrastruktur, da die Modelle auf hohem Niveau sind.

VisualSim-Benutzer erhalten über 500 vorgefertigte Beispiele, die Ihnen einen schnellen Einstieg erleichtern, z. B. ein komplettes Kommunikationssystem mit Antenne, Transceiver, FPGA mit Basisband und Ethernet-Schnittstelle. Systemarchitekten, die VisualSim verwenden, können mit allen untergeordneten Spezialisten wie RTL-Designern zusammenarbeiten.

Kompromisse auf Systemebene können modelliert und bewertet werden, wie zum Beispiel:

- Wechsel von 64-QAM zur QPSK-Modulation

- Vom schnelleren zum langsameren Prozessor

- Ändern der Ethernet-Spezifikationen

Wenn Sie mit VisualSim beginnen, um zu modellieren, zu implementieren und dann zu messen, können Sie mit einer Genauigkeit von 95 % im Vergleich zu RTL-Implementierungsergebnissen rechnen. Das Versprechen der Verwendung von High-Level-Modellen besteht darin, Leistungsprobleme vor der Implementierung oder Integration zu beseitigen. Es ist wirklich keine Codierung für ein gesamtes Systemmodell erforderlich.

Mirabilis hat bisher weltweit 65 Kunden und rund 250 abgeschlossene Projekte. Zu den namhaften Kunden gehören: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Zusammenfassung

Früher hat ein Systemdesigner beim Essen im Restaurant vielleicht seine Ideen auf einer Serviette niedergeschrieben und sich dann wieder an die Arbeit gemacht, um ein paar Excel-Tabellen mit geheimnisvollen Gleichungen zusammenzubasteln, um ein Modell zu erstellen. Heute gibt es eine neue Wahl, und das ist Geben VisualSim von Mirabilis einen Versuch. Sie können jetzt in nur wenigen Wochen ein gesamtes System modellieren und gleichzeitig architektonische Kompromisse eingehen, während Sie tatsächliche Simulationen durchführen, bevor Sie sich mit detaillierten Implementierungsdetails befassen.

Verwandte Blogs

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/