Die Definition, ob es sich bei einem 2.5D-Gerät um eine Leiterplatte handelt, die so verkleinert wurde, dass sie in ein Gehäuse passt, oder um einen Chip, der über die Grenzen eines einzelnen Chips hinausragt, mag wie eine haarspalterische Semantik erscheinen, kann aber erhebliche Konsequenzen für den Gesamterfolg haben eines Entwurfs.

Planare Chips waren schon immer durch die Größe des Absehens begrenzt, die etwa 858 mm beträgt2. Darüber hinaus machen Ertragsprobleme das Silizium unwirtschaftlich. Dies hat jahrelang die Anzahl der Merkmale begrenzt, die auf einem planaren Substrat untergebracht werden konnten. Alle zusätzlichen Funktionen müssten in zusätzliche Chips integriert und mit einer Leiterplatte (PCB) verbunden werden.

Das Aufkommen von 2.5D Die Verpackungstechnologie hat eine völlig neue Expansionsachse eröffnet und ermöglicht mehrere Chiplets innerhalb eines miteinander verbunden sein erweitertes Paket. Der Ausgangspunkt für dieses Paketdesign kann jedoch große Auswirkungen darauf haben, wie die verschiedenen Komponenten zusammengebaut werden, wer daran beteiligt ist und welche Tools wann eingesetzt werden.

Es gibt mehrere Gründe, warum 2.5D heute auf dem Vormarsch ist. Einer davon sind die Kosten. „Wenn man kleinere Chips oder Chiplets bauen kann und diese Chiplets so konzipiert und optimiert wurden, dass sie in ein Gehäuse integriert werden können, kann das Ganze kleiner werden“, sagt Tony Mastroianni, Direktor für fortschrittliche Verpackungslösungen bei Siemens Digital Industries Software. „Und weil der Ertrag viel höher ist, hat das dramatische Auswirkungen auf die Kosten. Anstatt bei Chips in Chipgröße eine Ausbeute von 50 % oder weniger zu erzielen, können Sie diese auf bis zu 90 % steigern.“

Auch die Verbindung von Chips über eine Leiterplatte schränkt die Leistung ein. „In der Vergangenheit hatten wir Chips separat verpackt und dann auf eine Leiterplatte gesteckt und mit etwas Routing miteinander verbunden“, sagt Ramin Farjadrad, CEO und Mitbegründer von Eliyan. „Die Probleme, mit denen die Menschen konfrontiert wurden, waren zweierlei. Einer davon war, dass die Bandbreite zwischen diesen Chips dadurch begrenzt war, dass sie durch die Leiterplatte und dann durch eine begrenzte Anzahl von Kugeln auf dem Gehäuse gingen, was die Konnektivität zwischen diesen Chips einschränkte.“

Der Hauptunterschied zwischen 2.5D und einer Leiterplatte besteht darin, dass 2.5D Chipabmessungen verwendet. Es gibt viel feinkörnigere Drähte und verschiedene Komponenten können auf einem Interposer oder in einem Gehäuse viel enger zusammengepackt werden als auf einer Platine. Aus diesen Gründen können Leitungen kürzer sein, es kann mehr Leitungen geben und die Bandbreite wird erhöht.

Das wirkt sich auf mehreren Ebenen auf die Leistung aus. „Da sie so nahe beieinander liegen, gibt es beim Transport keine langen RC- oder LC-Verzögerungen, es geht also viel schneller“, sagt Mastroianni von Siemens. „Man braucht keine großen Treiber auf einem Chip, um lange Leiterbahnen über die Platine zu treiben, sodass man weniger Strom benötigt. Sie erhalten eine um Größenordnungen bessere Leistung – und einen geringeren Stromverbrauch. Eine gängige Metrik ist die Angabe von Pico-Joule pro Bit. Die Menge an Energie, die zum Bewegen von Bits erforderlich ist, macht 2.5D überzeugend.“

Dennoch wirkt sich die Denkweise auf das ursprüngliche Designkonzept aus, und das hat Auswirkungen auf den gesamten Ablauf. „Wenn Sie mit einem Chip-Designer sprechen, wird er wahrscheinlich sagen, dass es sich nur um einen großen Chip handelt“, sagt John Park, Produktmanagement-Gruppenleiter bei der Custom IC & PCB Group bei Kadenz. „Aber wenn Sie mit einem Gehäusedesigner oder einem Platinendesigner sprechen, werden sie sagen, dass es sich im Grunde genommen um eine winzige Leiterplatte handelt.“

Wer hat Recht? „Oft entscheidet die interne Organisationsstruktur im Unternehmen darüber, wie dabei vorgegangen wird“, sagt Marc Swinnen, Leiter Produktmarketing bei Ansys. „Langfristig möchten Sie sicherstellen, dass Ihr Unternehmen so strukturiert ist, dass es der Physik entspricht, und nicht versuchen, sich an die Physik Ihres Unternehmens anzupassen.“

Klar ist, dass nichts sicher ist. „Die digitale Welt war insofern sehr regelmäßig, als wir alle zwei Jahre einen neuen Knoten halber Größe bekamen“, sagt Cadence's Park. „Es würde einige neue Anforderungen geben, aber es war sehr evolutionär. Verpackungen sind der Wilde Westen. Wir könnten dieses Jahr acht neue Verpackungstechnologien bekommen, nächstes Jahr drei und nächstes Jahr zwölf. Viele davon stammen von den Gießereien, während sie früher nur von den ausgelagerten Halbleitermontage- und Testunternehmen (OSATs) und den Substratlieferanten stammten. Während die Gießereien ein neuer Marktteilnehmer sind, bieten die OSATs einige wirklich interessante Verpackungstechnologien zu geringeren Kosten an.“

Dies liegt unter anderem daran, dass verschiedene Personengruppen unterschiedliche Anforderungen haben. „Die Regierung und das Militär sehen den Hauptvorteil in heterogenen Integrationsfähigkeiten“, sagt Swinnen von Ansys. „Sie drängen nicht auf den neuesten Stand der Verarbeitungstechnologie. Stattdessen entwerfen sie Dinge wie monolithische integrierte Mikrowellenschaltkreise (MMICs), bei denen sie Wellenleiter für sehr schnelle Signale benötigen. Sie nähern sich dem Thema aus der Sicht der Verpackungsmontage. Umgekehrt gehen die High-Performance-Computing-Unternehmen (HPC) von einem Stapel von 5-nm- und 3-nm-Chips mit Hochleistungsspeicher mit hoher Bandbreite (HBM) aus. Sie sehen darin ein Problem bei der Siliziummontage. Als Vorteil sehen sie die Flexibilität der Architektur, mit der sie Kerne und Schnittstellen einbauen und Produkte für bestimmte Märkte entwickeln können, ohne jedes Chiplet neu entwerfen zu müssen. Sie sehen Flexibilität als Vorteil. Das Militär sieht in der heterogenen Integration den Vorteil.“

Materialien

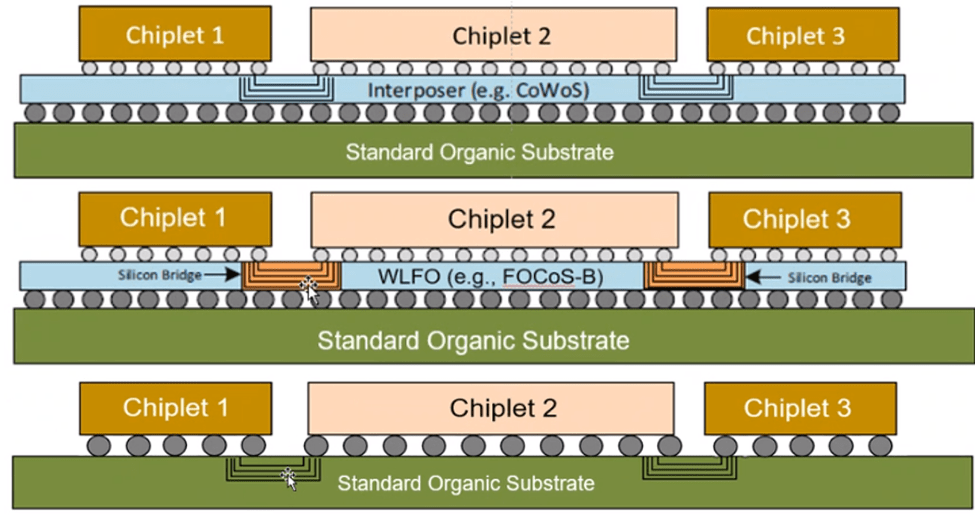

In der 2.5D-Packaging-Technologie werden mehrere Materialien als Substrat verwendet, von denen jedes unterschiedliche Kompromisse in Bezug auf Kosten, Dichte und Bandbreite aufweist und außerdem eine Reihe unterschiedlicher physikalischer Probleme mit sich bringt, die überwunden werden müssen. Einer der Hauptunterschiede ist der Bump-Pitch, wie in Abbildung 1 dargestellt.

Abb. 1. Chiplet-Verbindung für verschiedene Substratkonfigurationen. Quelle: Eliyan

Wenn es um eine geht InterposerIm Allgemeinen wird davon ausgegangen, dass es sich um Silizium handelt. „Der Interposer könnte ein großes Stück Silizium sein (Abb. 1 oben) oder nur Siliziumbrücken zwischen den Chips (Abb. 1 Mitte), um die Konnektivität bereitzustellen“, sagt Farjadrad von Eliyan. „Beide Lösungen nutzen Mikrohöcker mit hoher Dichte. Interposer und Brücken sorgen für viele Bumps und Leiterbahnen mit hoher Dichte, und das gibt Ihnen Bandbreite. Wenn Sie 1,000 Kabel mit jeweils 5 GB verwenden, erhalten Sie 5 TB. Wenn Sie 10,000 haben, erhalten Sie 50 TB. Aber diese Signale dürfen nicht weiter als zwei oder drei Millimeter reichen. Wenn Sie alternativ den Silizium-Interposer vermeiden und bei einem organischen Gehäuse bleiben (Abb. 1 unten), beispielsweise einem Flip-Chip-Gehäuse, ist die Dichte der Leiterbahnen 5- bis 10-mal geringer. Allerdings kann die Dicke der Drähte das 5- bis 10-fache betragen. Das ist ein erheblicher Vorteil, da der Widerstand der Drähte im Quadrat zur Dicke der Drähte abnimmt. Der Querschnitt dieses Drahtes vergrößert sich im Quadrat zu diesem Draht, sodass der Widerstand deutlich abnimmt. Wenn die Dichte fünfmal geringer ist, bedeutet das, dass Sie Signale fast 5-mal weiter übertragen können.“

Für manche Menschen kommt es vor allem auf die Bandbreite pro Millimeter an. „Wenn Sie einen parallelen Bus oder eine parallele Schnittstelle mit hoher Geschwindigkeit haben und Bandbreite pro Millimeter wünschen, würden Sie sich wahrscheinlich für einen Silizium-Interposer entscheiden“, sagt Kent Stahn, Senior Manager für Hardware-Engineering in Synopsys'Solutions Group. „Ein organisches Substrat ist verlustarm und kostengünstig, hat aber nicht die nötige Dichte. Dazwischen gibt es eine Reihe von Lösungen, die einiges davon leisten, aber nicht zu den gleichen Kosten.“

Es gibt auch andere Gründe, sich für ein Substratmaterial zu entscheiden. „Der Silizium-Interposer stammt aus einer Gießerei, daher ist die Verfügbarkeit ein Problem“, sagt Manuel Mota, leitender Produktmanager in der Solutions Group von Synopsys. „Einige Unternehmen stehen bei der Beschaffung fortschrittlicher Pakete vor Herausforderungen, da Kapazitäten ausgeschöpft sind. Wenn Sie auf andere Technologien umsteigen, die eine etwas geringere Bandbreitendichte haben, die aber vielleicht für Ihre Anwendung ausreicht, können Sie sie woanders finden. Das wird zu einem kritischen Aspekt.“

Allerdings schreiten alle diese Technologien rasant voran. „Die Absehengrenze liegt bei etwa 858 mm im Quadrat“, sagt Park. „Die Leute reden über Interposer, die vielleicht viermal so groß sind, aber wir haben Laminate, die viel größer sind. Einige der aus Japan stammenden Laminatsubstrate erreichen nahezu die gleiche Verbindungsdichte, die wir mit Silizium erreichen können. Ich persönlich sehe einen stärkeren Trend hin zu organischen Substraten. Chip-on-Wafer-on-Substrate (CoWoS) von TSMC nutzt einen Silizium-Interposer und ist seit etwa 12 Jahren die Technologie der Wahl. Kürzlich führten sie CoWoS-R ein, bei dem Folienpolyamid verwendet wird, das eher einem organischen Substrattyp ähnelt. Jetzt hören wir viel über Glassubstrate.“

Mit der Zeit kann sich die Gesamtfläche des Pakets vergrößern. „Für Gießereien macht es keinen Sinn, weiterhin Dinge in der Größe einer 30-Zoll-Leiterplatte zu bauen“, fügt Park hinzu. „Es gibt Materialien, die für größere Designs geeignet sind. Wo wir wirklich Dichte brauchen, ist von Sterben zu Sterben. Wir wollen diese Chiplets direkt nebeneinander, mit einer Verbindungslänge von ein paar Millimetern. Wir wollen es ganz kurz haben. Aber der Rest besteht nur darin, die E/A aufzufächern, damit sie mit der Leiterplatte verbunden werden.“

Aus diesem Grund sind Brücken beliebt. „Wir sehen eine Entwicklung hin zu Brücken für den Hochgeschwindigkeitsteil der Schnittstelle“, sagt Stahn von Synopsys. „Die Rückseite davon wäre Fanout, wie RDL-Fanout. Wir sehen RDL-Pakete, die in Zukunft eher traditionellen Paketen ähneln werden.“

Interposer bieten zusätzliche Möglichkeiten. „Heute sind 99 % der Interposer passiv“, sagt Park. „Es gibt kein Front-End-of-Line, es gibt keine Geräteebenen. Es handelt sich um eine reine Back-End-of-Line-Verarbeitung. Sie fügen diesem Silizium drei, vier, fünf Metallschichten hinzu. Das nennen wir einen passiven Interposer. Es geht lediglich darum, diese Die-zu-Die-Verbindung herzustellen. Aber es gibt Leute, die diesen Würfel nehmen und ihn zu einem aktiven Interposer machen, was im Grunde genommen Logik hinzufügt.“

Das kann zu unterschiedlichen Zwecken geschehen. „Man sieht bereits, dass einige Unternehmen aktive Interposer einsetzen, bei denen sie das Energiemanagement oder einen Teil der Steuerlogik hinzufügen“, sagt Mota. „Wenn man anfängt, aktive Schaltkreise auf Interposern zu platzieren, handelt es sich dann immer noch um eine 2.5D-Integration oder wird es zu einer 3D-Integration? Wir sehen heute keinen großen Trend zu aktiven Interposern.“

Es gibt jedoch einige neue Probleme. „Man muss Unstimmigkeiten bei den Wärmeausdehnungskoeffizienten (CTE) berücksichtigen“, sagt Stahn. „Das passiert immer dann, wenn zwei Materialien mit unterschiedlichen WAK miteinander verbunden werden. Beginnen wir mit dem Silizium-Interposer. Es gibt Systeme mit höherer Wattzahl, bei denen die SoCs mit ihren Kollegen kommunizieren können und die viel Strom verbrauchen können. Ein Silizium-Interposer muss immer noch in einem Paket untergebracht werden. Die CTE-Fehlanpassungen bestehen zwischen dem Silizium und dem Gehäusematerial. Und mit der Brücke können Sie sie dort einsetzen, wo Sie sie brauchen, aber es ist immer noch eine Silizium-Die-to-Die-Verbindung. Sie müssen die thermomechanische Analyse durchführen, um sicherzustellen, dass die Leistung, die Sie liefern, und die CTE-Fehlanpassungen, die Sie haben, zu einem funktionsfähigen System führen.“

Obwohl die Signallängen theoretisch länger werden können, wirft dies einige Probleme auf. „Wenn Sie diese langen Verbindungen innerhalb eines Chips herstellen, beschränken Sie diese Routen normalerweise auf ein paar Millimeter und puffern sie dann“, sagt Mastroianni. „Das Problem bei einem passiven Silizium-Interposer ist, dass es keine Puffer gibt. Das kann wirklich zu einem ernsten Problem werden. Wenn Sie diese Verbindungen herstellen müssen, müssen Sie diese sehr sorgfältig planen. Und Sie müssen sicherstellen, dass Sie eine Timing-Analyse durchführen. Normalerweise werden Ihre Paket-Mitarbeiter diese Analyse nicht durchführen. Das ist eher ein Problem, das von Siliziumingenieuren mit statischer Timing-Analyse gelöst wurde. Wir müssen einen STA-Fluss einführen und uns mit allen Extraktionen befassen, die organische und siliziumartige Spuren enthalten, und das wird zu einem neuen Problem. Wenn Sie anfangen, sich mit einigen dieser sehr langen Leiterbahnen zu befassen, berücksichtigen Ihre einfachen RC-Zeitverzögerungen, die in normalen STA-Verzögerungsrechnern angenommen werden, einen Teil der Induktivität und Gegeninduktivität zwischen diesen Leiterbahnen nicht, sodass es zu ernsthaften Genauigkeitsproblemen kommen kann für diese langen Spuren.“

Aktive Interposer helfen. „Mit aktiven Interposern können Sie einige der Langstreckenprobleme überwinden, indem Sie Puffer oder Signalverstärker einbauen“, sagt Swinnen. „Dann sieht es wieder mehr wie ein Chip aus, und das geht nur auf Silizium. Sie verfügen über die EMIB-Technologie von Intel, bei der ein Chiplet in den Interposer eingebettet ist und das eine aktive Brücke ist. Der Chip kommuniziert mit dem EMIB-Chip, und beide kommunizieren mit Ihnen über diesen kleinen aktiven Brückenchip, der nicht gerade ein aktiver Interposer ist, sich aber fast wie ein aktiver Interposer verhält.“

Aber auch passive Komponenten bieten einen Mehrwert. „Als Erstes werden Grabenkondensatoren in den Interposer eingebaut“, sagt Mastroianni. „Das gibt Ihnen die Möglichkeit, eine gute Entkopplung dort durchzuführen, wo es darauf ankommt, in der Nähe des Würfels. Wenn Sie sie auf der Platine installieren, gehen viele Vorteile der Hochgeschwindigkeitsschnittstellen verloren. Wenn Sie sie in den Interposer einbauen können, direkt unter der Stelle, an der sich die schnell schaltenden Geschwindigkeitssignale befinden, können Sie eine lokale Entkopplung erzielen.“

Neben unterschiedlichen Materialien stellt sich die Frage, wer den Interposer entwirft. „Die Industrie scheint es als eine kleine Leiterplatte zu betrachten, wenn man bedenkt, wer das Design macht“, sagt Matt Commens, Senior Manager für Produktmanagement bei Ansys. „Die Interposer werden typischerweise von Verpackungsingenieuren entworfen, obwohl es sich um Siliziumprozesse handelt. Dies gilt insbesondere für die Hochleistungsmodelle. Es scheint nicht intuitiv zu sein, aber sie haben diesen Hintergrund in der Signalintegrität, sie haben Übertragungsleitungen entworfen und die Fehlanpassung bei Verbindungen minimiert. Ein traditioneller IC-Designer arbeitet aus Komponentensicht. Die Branche sagt uns also sicherlich, dass die Leute, die sie mit der Designarbeit beauftragen, Personas vom Typ „Verpackung“ sind.“

Power

Es gibt einige erhebliche Unterschiede beim Routing zwischen PCBs und Interposern. „Das Interposer-Routing ist viel einfacher, da die Anzahl der Komponenten im Vergleich zur Leiterplatte drastisch reduziert wird“, sagt Andy Heinig, Abteilungsleiter für effiziente Elektronik bei Fraunhofer IIS/EAS. „Andererseits ist das Stromnetz auf dem Interposer aufgrund des höheren Widerstands der Metallschichten und der Tatsache, dass das Stromnetz durch Signaldrähte unterbrochen ist, viel komplexer. Das Routing für die Die-to-Die-Schnittstelle ist aufgrund der Routing-Dichte komplexer.“

Die Leistungsabgabe sieht ganz anders aus. „Wenn man sich eine Leiterplatte anschaut, werden diese großen Metallgussbereiche in die Schichten eingebettet und Bereiche ausgespart, durch die Dinge hindurchgehen müssen“, sagt Park. „Man legt einen Haufen Kupfer hin und streicht dann die anderen aus. Auf diese Weise können wir keinen Interposer bauen. Wir müssen die Verbindung aufbringen, damit die Strom- und Erdungsstrukturen auf einem Silizium-Interposer eher wie ein digitaler Chip aussehen. Aber das Signal wird eher wie eine Leiterplatte oder ein Laminatgehäuse aussehen.“

Das Routing ähnelt eher einer Leiterplatte als einem Chip. „An den Stellen, an denen eine Verbindung zu einem Pad oder einer Durchkontaktierung hergestellt wird, sieht man Dinge wie Tropfen oder Filets, um eine bessere Ausbeute zu erzielen“, fügt Park hinzu. „Heutzutage sind die Routing-Stile eher auf Leiterplatten als auf digitale ICs ausgerichtet, wo es lediglich orthogonale 90°-Ecken und saubere Routing-Kanäle gibt. Bei Interposern, egal ob aus Silizium oder organisch, ist die Durchkontaktierung oft größer als der Draht, was ein klassisches PCB-Problem darstellt. Wenn wir über digitale Router sprechen, ähneln sie wiederum eher einer kleinen Leiterplatte als einem Chip.“

Auch TSVs können Probleme verursachen. „Wenn man sie quadratisch behandelt, verliert man an den Ecken viel Platz“, sagt Swinnen. „Man möchte wirklich einen 45°-Winkel um diese Objekte haben. Silicon-Router sind traditionell Manhattan-Router, obwohl es eine lange Tradition des RDL-Routings gibt, bei dem es sich um die oberste Schicht handelt, auf der die Bumps verbunden sind. Dabei wurden traditionell achteckige oder runde Höcker und dann eine 45°-Fräsung verwendet. Es ist nicht so flexibel wie das PCB-Routing, aber sie verfügen über Umverteilungsschicht-Router und einige Router, die von der vollständig kundenspezifischen Seite kommen und über ein vollständiges River-Routing verfügen.“

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/