TSMC gần đây đã tổ chức Hội nghị chuyên đề công nghệ hàng năm tại Santa Clara, CA. Các bài thuyết trình cung cấp cái nhìn tổng quan toàn diện về tình trạng công nghệ và lộ trình sắp tới của họ, bao gồm tất cả các khía cạnh của quy trình công nghệ và phát triển bao bì tiên tiến. Bài viết này sẽ tóm tắt những điểm nổi bật của các bài thuyết trình về công nghệ đóng gói tiên tiến – một bài viết trước đề cập đến lĩnh vực công nghệ xử lý.

Tổng Quát

TSMC đã hợp nhất các sản phẩm bao bì 2.5D và 3D của họ thành một thương hiệu duy nhất – “Vải 3D”. Kỳ vọng là sẽ có những khách hàng trong tương lai theo đuổi cả hai tùy chọn để cung cấp sự tích hợp dày đặc, không đồng nhất của chức năng cấp hệ thống – ví dụ: cả lắp ráp dọc 3D “mặt trước”, kết hợp với tích hợp 2.5D “mặt sau”.

Về mặt kỹ thuật, việc tích hợp 2.5D của SoC với ngăn xếp HBM bộ nhớ băng thông cao “3D” đã là một sản phẩm kết hợp. Như minh họa ở trên, TSMC đang hình dung ra sự kết hợp các cấu trúc liên kết phong phú hơn nhiều trong tương lai, kết hợp SoIC 3D với 2.5D CoWoS/InFO như một phần của các thiết kế hệ thống không đồng nhất rất phức tạp.

Giống như các bài thuyết trình về công nghệ quy trình tại Hội nghị chuyên đề, các bản cập nhật công nghệ đóng gói khá đơn giản – một dấu hiệu cho thấy việc thực hiện lộ trình đang diễn ra thành công. Có một số lĩnh vực cụ thể đại diện cho những hướng đi mới sẽ được nêu bật bên dưới.

Đặc biệt lưu ý là khoản đầu tư của TSMC vào nhà máy Tích hợp hệ thống nâng cao, sẽ hỗ trợ các sản phẩm Vải 3D, cung cấp khả năng sản xuất thử nghiệm và lắp ráp đầy đủ.

Bao bì 2.5D

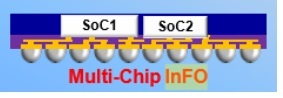

Có hai loại công nghệ đóng gói 2.5D – “chip-on-wafer-on-substrate” (CoWoS) và “tích hợp fanout” (InFO).

(Lưu ý rằng trong hình trên, một số dịch vụ InFO được TSMC ký hiệu là “2D”.)

Sáng kiến quan trọng của cả hai công nghệ này là tiếp tục mở rộng kích thước gói tối đa để cho phép tích hợp số lượng khuôn lớn hơn (và ngăn xếp HBM). Ví dụ: việc chế tạo các lớp kết nối trên bộ chuyển đổi silicon (CoWoS-S) yêu cầu “khâu” nhiều mức phơi sáng in thạch bản – mục tiêu là tăng kích thước bộ chuyển đổi theo bội số của kích thước kẻ ô tối đa.

CoWoS đã mở rộng để cung cấp ba công nghệ interposer khác nhau (“wafer” trong CoWoS):

- CoWoS-S

- sử dụng bộ chuyển đổi silicon, dựa trên quá trình xử lý lớp phân phối lại và in thạch bản wafer silicon hiện có

- sản xuất số lượng lớn kể từ năm 2012, >100 sản phẩm cho hơn 20 khách hàng cho đến nay

- bộ chuyển mạch tích hợp các tụ điện “rãnh” nhúng

- Đang phát triển kích thước tâm ngắm tối đa gấp 3 lần – để hỗ trợ cấu hình thiết kế với 2 SoC lớn và 8 ngăn xếp bộ nhớ HBM3, với eDTC1100 (1100nF/mm**2)

- CoWoS-R

- sử dụng một bộ xen kẽ hữu cơ để giảm chi phí

- lên đến 6 lớp kết nối phân phối lại, 2um/2um L/S

- Kích thước tâm ngắm 4X hỗ trợ một SoC với 2 ngăn xếp HBM2 trong gói 55mmX55mm; Kích thước tâm ngắm 2.1X đang được phát triển, với 2 SoC và 2HBM2 trong gói 85mmX85mm

- CoWoS-L

- sử dụng một “cầu nối” silicon nhỏ được lắp vào một bộ chuyển tiếp hữu cơ, để kết nối mật độ cao giữa các cạnh khuôn liền kề (khoảng cách 0.4um/0.4um L/S)

- Kích thước kẻ ô 2X hỗ trợ 2 SoC với 6 ngăn xếp HBM2 2023); Kích thước tâm ngắm 4X đang được phát triển để hỗ trợ 12 ngăn xếp HBM3 (2024)

TSMC nhấn mạnh rằng họ đang làm việc với nhóm tiêu chuẩn HBM về cấu hình vật lý của các yêu cầu kết nối HBM3 để triển khai CoWoS. (Tiêu chuẩn HBM3 dường như đã giải quyết các vấn đề sau đối với định nghĩa ngăn xếp: dung lượng từ 4GB với bốn khuôn 8Gb đến 64GB với mười sáu khuôn 32Gb; giao diện tín hiệu 1024 bit; băng thông lên tới 819GBps.) Các cấu hình CoWoS sắp ra mắt này có nhiều Ngăn xếp HBM3 sẽ cung cấp dung lượng bộ nhớ và băng thông cực lớn.

Ngoài ra, để dự đoán khả năng tiêu thụ điện năng lớn hơn nhiều trong các thiết kế CoWoS sắp tới, TSMC đang nghiên cứu các giải pháp làm mát thích hợp, cả vật liệu giao diện nhiệt (TIM) được cải tiến giữa khuôn và gói, cũng như chuyển từ làm mát không khí sang làm mát ngâm.

Sau khi định hướng vị trí chính xác (mặt úp xuống) trên giá đỡ tạm thời, khuôn được bọc trong một “tấm bán dẫn” epoxy. Các lớp kết nối phân phối lại được thêm vào bề mặt wafer hoàn nguyên. Sau đó, các gói gói được kết nối trực tiếp với các lớp phân phối lại.

Có các cấu trúc liên kết InFO_PoP, InFO_oS và InFO_B.

Như được hiển thị bên dưới, InFO_PoP biểu thị cấu hình gói trên gói và tập trung vào việc tích hợp gói DRAM với khuôn logic cơ sở. Các phần lồi trên khuôn trên DRAM sử dụng vias InFO (TIV) để tiếp cận các lớp phân phối lại.

- InFO_PoP chủ yếu dành cho nền tảng di động

- hơn 1.2 tỷ chiếc được xuất xưởng kể từ năm 2016

Một vấn đề với việc triển khai InFO_PoP là gói DRAM hiện là thiết kế tùy chỉnh và chỉ có thể được chế tạo tại TSMC. Có một cấu trúc liên kết InFO_B thay thế đang được phát triển, trong đó gói DRAM (LPDDR) hiện có được thêm vào bên trên, với việc lắp ráp sẽ được cung cấp bởi nhà sản xuất hợp đồng bên ngoài.

InFO_oS (trên chất nền) cho phép bao bọc nhiều khuôn, với các lớp phân phối lại và các vi mạch của chúng được kết nối với một chất nền bằng TSV.

- đã sản xuất được hơn 5 năm, tập trung vào khách hàng của HPC

- 5 lớp RDL trên đế, với 2um/2um L/S

- chất nền cho phép chiếm diện tích gói hàng lớn, hiện ở mức 110mm X 110mm với các kế hoạch cho kích thước lớn hơn

- Sân va chạm 130um C4

Như mô tả ở trên, InFO_M là một giải pháp thay thế cho InFO_oS, với nhiều lớp khuôn và phân phối lại được bao bọc, không có chất nền + TSV bổ sung (gói < 500mm**2, sản xuất trong nửa cuối năm 2).

Bao bì 3D

Thông tin-3D

Có một công nghệ gói xếp chồng 3D sử dụng khuôn vi va chạm được tích hợp theo chiều dọc với các lớp phân phối lại và TIV, tập trung vào nền tảng di động.

SoIC 3D

Họ bao bì cấu trúc liên kết 3D xếp chồng theo chiều dọc tiên tiến hơn được ký hiệu là “chip tích hợp hệ thống” (SoIC). Nó sử dụng liên kết Cu trực tiếp giữa khuôn với cường độ mạnh.

Có hai sản phẩm SoIC – “wafer-on-wafer” (WOW) và “chip-on-wafer” (COW). Cấu trúc liên kết WOW tích hợp một khuôn SoC phức tạp trên một tấm bán dẫn cung cấp cấu trúc tụ điện rãnh sâu (DTC) để tách rời tối ưu. Cấu trúc liên kết COW tổng quát hơn xếp chồng nhiều khuôn SoC.

Các công nghệ xử lý đủ tiêu chuẩn để lắp ráp SoIC được trình bày trong bảng bên dưới.

Hỗ trợ thiết kế cho 3DFabric, bao gồm 3dblox

Hỗ trợ thiết kế cho 3DFabric, bao gồm 3dblox

Như được minh họa ở góc trên bên phải của hình ảnh Vải 3D ở trên, TSMC đang hình dung các triển khai thiết kế trọn gói hệ thống phức tạp, kết hợp cả công nghệ 3D SoIC và 2.5D.

Độ phức tạp dẫn đến trong quy trình thiết kế là rất lớn, như đã nêu ở trên, với các quy trình phân tích nhiệt, thời gian và SI/PI nâng cao được yêu cầu (cũng có thể xử lý khối lượng dữ liệu mô hình).

Để cho phép phát triển các thiết kế cấp hệ thống này, TSMC đã hợp tác với các nhà cung cấp EDA về ba sáng kiến dòng thiết kế chính:

- phân tích nhiệt được cải thiện, sử dụng phương pháp tiếp cận hạt thô cộng với hạt mịn)

- phân tích thời gian tĩnh phân cấp

- khuôn riêng lẻ được thể hiện bằng một mô hình trừu tượng, để giảm độ phức tạp của việc phân tích dữ liệu tổng thể (đa góc)

- khuôn riêng lẻ được thể hiện bằng một mô hình trừu tượng, để giảm độ phức tạp của việc phân tích dữ liệu tổng thể (đa góc)

- phân vùng thiết kế mặt trước

Để giúp đẩy nhanh quá trình phân vùng thiết kế mặt trước của một hệ thống phức tạp, TSMC đã theo đuổi một sáng kiến có tên là “3Dblox”.

Mục tiêu là chia nhỏ hệ thống gói vật lý tổng thể thành các thành phần mô-đun, sau đó được tích hợp. Các loại mô-đun là:

- sự va chạm / trái phiếu

- cách

- mũ

- người chen vào

- chết

Các mô-đun này sẽ được tích hợp vào bất kỳ công nghệ gói SoIC, CoWoS hoặc InFO nào.

Lưu ý cụ thể là TSMC đang nỗ lực cho phép các thiết kế Vải 3D sử dụng nhiều công cụ EDA khác nhau - nghĩa là hoàn thành thiết kế vật lý bằng một công cụ của nhà cung cấp EDA và (có khả năng) sử dụng các sản phẩm của nhà cung cấp EDA khác nhau để hỗ trợ phân tích thời gian, tín hiệu. phân tích tính toàn vẹn / tính toàn vẹn của năng lượng, phân tích nhiệt.

3Dblox dường như đã đưa khái niệm “luồng tham chiếu” cho SoC lên một tầm cao mới, với việc TSMC thúc đẩy khả năng tương tác giữa các định dạng và mô hình dữ liệu của nhà cung cấp EDA. Khả năng lưu chuyển 3Dblox tổng thể sẽ có sẵn vào quý 3 năm 2022. (Bước sơ bộ – tức là tự động định tuyến các tín hiệu phân phối lại trên InFO – sẽ là tính năng đầu tiên được phát hành.)

Rõ ràng, TSMC đang đầu tư rộng rãi vào việc phát triển công nghệ đóng gói tiên tiến và (đặc biệt) các cơ sở chế tạo mới, do sự tăng trưởng được mong đợi ở cả cấu hình 2.5D và 3D. Việc chuyển đổi từ ngăn xếp bộ nhớ HBM2/2e sang HBM3 sẽ mang lại lợi ích đáng kể về hiệu suất cho các thiết kế hệ thống sử dụng công nghệ CoWoS 2.5. Khách hàng nền tảng di động sẽ mở rộng sự đa dạng của các thiết kế đa khuôn InFO. Việc áp dụng các thiết kế 3DFabric phức tạp kết hợp cả công nghệ 3D và 2.5D chắc chắn cũng sẽ tăng lên, thúc đẩy nỗ lực của TSMC trong việc “mô-đun hóa” các yếu tố thiết kế nhằm tăng tốc phân vùng hệ thống, cũng như nỗ lực của họ nhằm kích hoạt một bộ công cụ EDA rộng rãi/ dòng chảy được áp dụng.

-chipguy

Cũng đọc:

Đánh giá chuyên đề công nghệ TSMC 2022 - Phát triển công nghệ quy trình

Ba bài học quan trọng từ Hội nghị chuyên đề kỹ thuật TSMC năm 2022!

Công nghệ in thạch bản nghịch đảo - Cập nhật trạng thái từ TSMC

Chia sẻ bài đăng này qua: