TSMC höll nyligen sitt årliga teknologisymposium i Santa Clara, Kalifornien. Presentationerna gav en omfattande översikt över deras status och kommande färdplan, som täckte alla aspekter av processteknologi och avancerad förpackningsutveckling. Den här artikeln kommer att sammanfatta höjdpunkterna i processteknikuppdateringarna – en efterföljande artikel kommer att täcka det avancerade förpackningsområdet.

Först, här är en kort översikt över några av de allmänna observationerna och bredare branschtrender, som rapporterats av CC Wei, TSMC:s VD.

Allmänt

- "I år firar TSMC 35-årsjubileum. 1987 hade vi 258 anställda på en plats och släppte 28 produkter med tre teknologier. Tio år senare hade vi 3 5,600 anställda och släppte 915 produkter i 20 teknologier. I år 2022 har vi 63,000 12,000 anställda och kommer att släppa 300 XNUMX produkter över XNUMX teknologier."

- "Från 2018 till 2022 har volymen av 12" (motsvarande) wafers haft en årlig CAGR som överstiger 70%. I synnerhet ser vi en betydande ökning av antalet "big die"-produkter." (>500 mm**2)

- "2021 levererade TSMC:s affärssegment i Nordamerika mer än 7 miljoner wafers och över 5,500 700 produkter. Det fanns 65 nya produkter tapeouts (NTOs). Detta segment representerar XNUMX % av TSMC:s intäkter.”

- "Våra gigafab-expansionsplaner har vanligtvis inneburit att vi lägger till två nya "faser" varje år – det var fallet från 2017-2019. Under 2020 öppnade vi sex nya faser, inklusive vår avancerade förpackningsfabrik. 2021 fanns det sju nya faser, inklusive fabriker i Taiwan och utomlands – avancerad förpackningskapacitet lades också till. År 2022 kommer det att finnas fem nya faser, både i Taiwan och utomlands.”

- N2 tillverkning: Fab20 i Hsinchu

- N3: Fab 18 i Tainan

- N7 och N28: Fab22 i Kaohsiung

- N28: Fab26 i Nanjing Kina

- N16, N28 och specialteknologier: Fab23 i Kumanoto Japan (2024)

- N5 i Arizona (år 2024)

- "TSMC har 55 % av den globala installerade basen av EUV litografisystem."

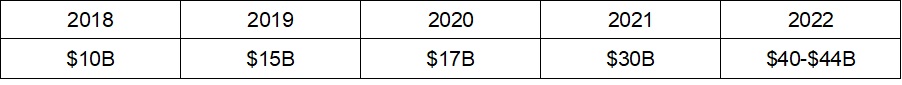

- "Vi utökar våra investeringar i kapitalutrustning avsevärt under 2022." (Tabellen nedan visar det avsevärda ökningen av planerade utgifter för caputrustning.)

- "Vi upplever stress i tillverkningskapaciteten hos mogna processnoder. På 35 år har vi aldrig ökat kapaciteten för en mogen nod efter att en efterföljande nod har rampat till högvolymtillverkning – det håller på att förändras. Vi investerar för att öka kapaciteten i vår 45nm-process.” (Senare, i en Q&A-session med en annan TSMC-chef, uppstod frågan om andra mogna noder också kommer att se en kapacitetsexpansion, såsom 90nm eller 65nm. "Nej, expansionsplaner är enbart för 45nm-noden, för närvarande.", var svaret.)

- "Vi fortsätter att investera kraftigt i "intelligent tillverkning", med fokus på precisionsprocesskontroll, verktygsproduktivitet och kvalitet. Varje gigafab hanterar 10 miljoner leveransbeställningar per dag och optimerar verktygsproduktiviteten. Varje gigafab genererar 70B datapunkter dagligen för att aktivt övervaka."

För första gången på symposiet tilldelades en speciell "Innovationszon" på utställningsvåningen. De senaste produkterbjudandena från ett antal nystartade företag lyftes fram. TSMC indikerade, "Vi har ökat vår stödinvestering för att hjälpa små företag att ta till sig vår teknik. Det finns ett dedikerat team som fokuserar på nystartade företag. Support för mindre kunder har alltid varit i fokus. Kanske kommer nästa Nvidia någonstans i det här området att finnas."

Process Technology Review

Med ett par undantag som diskuterades längre fram var presentationerna av processteknikens färdplan något rutinmässigt – det är inte en dålig sak, utan snarare en indikation på ett pågående framgångsrikt genomförande av tidigare färdplaner.

Uppdateringarna av färdplanen presenterades två gånger, en gång som en del av teknikagendan, och igen som en del av TSMC:s fokus på plattformslösningar. Kom ihåg att TSMC specifikt har identifierat fyra "plattformar" som individuellt tar emot utvecklingsinvesteringar för att optimera processteknikerbjudandena: mobil; högpresterande datoranvändning (HPC); bil; och IoT (ultra-låg effekt). Sammanfattningarna nedan slår samman de två presentationerna.

N7 / N6

- över 400 NTO:er i slutet av 2022, främst på smartphone- och CPU-marknaderna

- N6 erbjuder transparent migrering från N7, vilket möjliggör återanvändning av IP

- N6RF kommer att vara RF-lösningen för kommande WiFi7-produkter

- det finns en N7HPC-variant (visas inte i figuren ovan), som ger ~10 % prestandaförbättring vid överstyrda VDD-nivåer

För N6 kan logiska cellbaserade block implementeras på nytt i ett nytt bibliotek för ytterligare prestandaförbättringar, vilket uppnår en stor logikdensitetsförbättring (~18%).

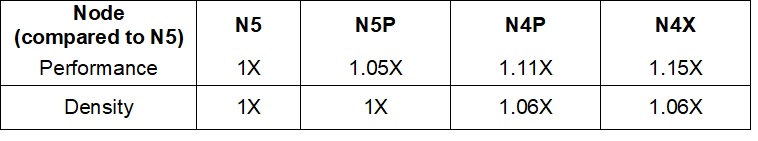

N5 / N4

- under det tredje produktionsåret, med över 3 miljoner wafers levererade, 2 NTO:er i slutet av 150

- mobilkunder var först, följt av HPC-produkter

- färdplanen inkluderar pågående N4-processförbättringar

- N4P foundation IP är klar, gränssnitts IP tillgänglig i 3Q2022 (till v1.0 PDK)

- det finns en N5HPC-variant (visas inte i figuren ovan, ~8% perf förbättring, HVM i 2H22)

Precis som med N7/N6 ger N4 "design återanvändning"-kompatibilitet med N5 hård IP, med ett cellbaserat blockåterimplementeringsalternativ.

Komplexiteten i SoC-designer för fordonssegmentet accelererar. Det kommer att finnas en N5A-processvariant för fordonsplattformen, kvalificerad för AEC-Q100 Grade 1 miljö- och tillförlitlighetsmål (måldatum: 2H22). Kvalificeringen för N5A-processer för fordon involverar både modellerings- och analysuppdateringar (t.ex. modeller för åldrande enheter, termisk medveten elektromigreringsanalys).

N3 och N3E

- N3 kommer att finnas i HVM med start under andra halvan av 2022

- N3E processvariant i HVM ett år senare; TSMC förväntar sig bred användning över mobila och HPC-plattformar

- N3E är redo för designstart (v0.9 PDK), med hög avkastning på standardkvalificeringstestplatsen för 256 Mb minnesuppsättning

- N3E lägger till metodalternativet "FinFLEX", med tre olika cellbibliotek optimerade för olika PPA-krav (mer i slutet av denna artikel)

Notera att N3 och N3E är något av en anomali i förhållande till den tidigare TSMC-processplanen. N3E kommer inte att erbjuda en transparent migrering av IP från N3. N3E-erbjudandet är lite av en "korrigering", eftersom betydande designregeländringar av N3 antogs för att förbättra avkastningen.

TSMC:s tidiga kunder kräver PPA-uppdateringar på en aggressiv tidslinje, oavsett om det är en inkrementell, kompatibel variant av en befintlig baslinje (t.ex. N7 till N6, N5 till N4), eller för en ny nod. Den ursprungliga N3-processdefinitionen har en bra pipeline av NTO:er, men N3E kommer att vara grunden för framtida varianter.

N2

- baserat på en nanosheetteknologi, målproduktionsdatum: 2025

- jämfört med N3E kommer N2 att erbjuda ~10-15% prestandaförbättring (@iso-power, 0.75V) eller ~25-30% effektminskning (@iso-perf, 0.75V); notera även det specificerade driftområdet i figuren ovan ner till 0.55V

- N2 kommer att erbjuda stöd för ett kraftdistributionsnätverk på baksidan

Parentetiskt står TSMC inför dilemmat att kraven på de olika plattformarna har ett så brett spektrum av mål för effekt, prestanda och yta/kostnad. Som nämnts ovan, adresserar N3E dessa mål med olika bibliotek, som innehåller ett annat antal fenor som definierar cellhöjden. För N2-biblioteksdesign ersätts detta designbeslut av ett processteknikbeslut om antalet vertikalt staplade nanoark (med viss tillåten variation i enhetens nanoarkbredd). Det ska bli intressant att se vad TSMC väljer att erbjuda för N2 för att täcka mobil- och HPC-marknaderna, vad gäller nanoarktopologin. (Bilden nedan från en tidigare teknisk presentation av TSMC vid VLSI 2022-konferensen visar 3 nanoark.)

OBS: Det finns två framväxande processteknologier som eftersträvas för att minska kraftleveransimpedansen och förbättra lokal routbarhet – dvs. "begravd" kraftskena (BPR) och "backside"-kraftdistribution (BSPDN). De inledande undersökningarna av att erbjuda BPR har snabbt utökats till att bearbeta färdplaner som integrerar fullständig BSPDN, som N2. Ändå är det lätt att blanda ihop de två akronymerna.

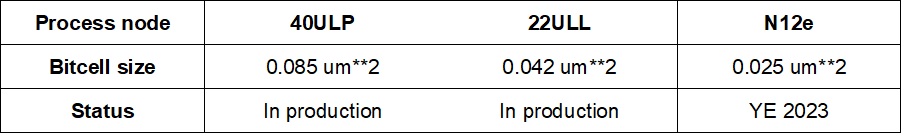

Specialitetstekniker

TSMC definierar följande erbjudanden i en klass som betecknas som "specialteknologier":

- ultralåg effekt/ultra-lågt läckage (med en ultrahög Vt-enhetsvariant)

- kräver särskilt fokus på SRAM-bitcellsdesign med ultralågt läckage

- N12e i produktion, N6e under utveckling (fokus på mycket låg VDD-modellstöd)

- (inbäddat) icke-flyktigt minne

- vanligtvis integrerad med en mikrokontroller (MCU), vanligtvis i en ULP/ULL-process

- Bagge

- kräver 2 extra masker, inbäddade i BEOL (mycket lägre kostnad än de 12 maskerna för eFlash)

- 10K skrivcykler (uthållighetsspecifikation), ~10 års retention @125C

-

- MRAM

- 22MRAM i produktion, fokus ligger på att förbättra uthålligheten

- 16MRAM för Automotive Grade 1-applikationer 2023

- MRAM

- power management IC (PMIC)

- baserat på bipolära CMOS-DMOS (BCD) enheter: 40BCD+, 22BCD+

- för komplexa 48V/12V effektdomäner

- kräver extremt låg enhet R_on

- högspänningstillämpningar (t.ex. bildskärmsdrivrutiner, med N80HV eller N55HV)

- analoga/blandade signalapplikationer som kräver unika aktiva och passiva strukturer (t.ex. precisions tunnfilmsmotstånd och enheter med lågt brus, med N22ULL och N16FFC)

- MEMS (används i rörelsesensorer, trycksensorer)

- CMOS-bildsensorer (CIS)

- pixelstorlek på 1.75um i N65, 0.5um i N28, övergång till N12FFC

- radiofrekvens (RF), som sträcker sig från mmWave till trådlös kommunikation med längre våglängd; den kommande WiFi7-standarden framhävdes

"Övergången från WiFi6 till WiFi7 kommer att kräva en betydande ökning av yta och effekt, för att stödja de ökade bandbreddskraven – t.ex. 2.2X area och 2.1X effekt. TSMC kvalificerar N6RF-erbjudandet, med ~30-40% effektminskning jämfört med N16RF. Detta kommer att göra det möjligt för kunder som för närvarande använder N16RF att i stort sett behålla befintliga effekt-/areamål när de utvecklar WiFi7-designer."

Diagrammen nedan illustrerar hur dessa specialteknologier är en grundläggande del av plattformsprodukter – t.ex. smartphones och fordonsprodukter. De karakteristiska processnoderna som används för dessa applikationer visas också.

Även om fokus för utveckling av smartphones tenderar att ligga på den huvudsakliga applikationsprocessorn, belyser diagrammet nedan de extremt olika kraven för specialteknologierbjudanden och deras relaterade funktioner. Inom fordonsområdet kommer övergången till en "zonstyrd" arkitektur att kräva en ny uppsättning IC:er för fordon.

N3E och FinFLEX

Tillkännagivandet om FinFLEX metodik betonades, med TSMC som indikerar "FinFLEX kommer att erbjuda full-nodskalning från N5."

I takt med att FinFET-teknologinoderna har skalats – dvs från N16 till N10 till N7 till N5 – har fenprofilen och drivström_per_mikron förbättrats avsevärt. Standardcellbiblioteksdesign har utvecklats till att inkludera färre pFET- och nFET-fenor som definierar cellhöjden (specificerad i termer av antalet horisontella metalldirigeringsspår). Som illustreras ovan använde N5-biblioteket en 2-2 fendefinition - det vill säga 2 pFET fenor och 2 nFET fenor för att definiera cellhöjden. (N16/N12 använde en 3-3-konfiguration.)

Bibliotekets definition för N3E ställdes inför ett par problem. Förbättringarna av pFET- och nFET-enhetens prestanda skalade inte lika. Och applikationerna för mobila och HPC-plattformar skiljer sig alltmer åt när det gäller deras PPA- (och kostnadsmål). Mobila produkter fokuserar på kretstäthet för att integrera mer funktionalitet och/eller minskad effekt, med mindre krävande prestandaförbättringar. HPC är mycket mer fokuserat på att maximera prestanda.

Som ett resultat kommer N3E att erbjuda tre bibliotek, som visas i figuren ovan:

- 2:1 ultralåg effekt bibliotek (en spårhöjd definierad av 2 pFET:1 nFET)

- 2:2 effektiv bibliotek

- 3:2 prestanda bibliotek

Bilden nedan är från TSMC:s FinFLEX-webbplats och illustrerar konceptet (länk).

Nu är det inte nytt att erbjuda flera bibliotek för integration på en enda SoC. I åratal har processorföretag utvecklat unika "datapath" och "control logic" bibliotekserbjudanden, med olika mål för: cellhöjder, kretsprestanda, routbarhet (dvs. maximal cellareaanvändning) och distinkta logikerbjudanden (t.ex. breda OCH- ELLER-grindar för datavägsmultiplexering). Ändå förlitade sig den fysiska implementeringen av SoC-designer med användning av flera bibliotek på ett konsekvent bibliotek per designblock.

Även om TSMC-bilden ovan också visar ett bibliotek per block, är FinFLEX-metodens unika natur att flera bibliotek och flera spårhöjder kommer att blandas i ett block. 2:1 plus 2:2 bibliotek och 2:2 plus 3:2 bibliotekskombinationer kommer att stödjas.

TSMC indikerade, ”Olika cellhöjder (i separata rader) är aktiverade i ett block för att optimera PPA. FinFLEX i N3E innehåller nya designregler, nya layouttekniker och betydande förändringar i EDA-implementeringsflöden."

Det kommer säkert att komma mer information om FinFLEX och förändringarna av det allmänna designflödet. Det kommer att behöva finnas nya metoder för att:

- golvplanering

- procentuell blandning av de två olika radhöjderna ska planeras för ett block

- mål% utnyttjande för celler i de olika biblioteksraderna för routbarhet (inklusive öppna celler för decap-fyllning)

- tillvägagångssätt mot PDN "avfolkning" för ett block med en betydande andel av celler med lägre effekt

- antal iterationer av planritning för blocket (genom fysisk syntes) för att nå stängning

- fysisk syntes

- hur kommer syntesen att förbättra timingen på en kritisk signal

För att förbättra timingen på en högbelastad signal skulle syntes vanligtvis uppdatera en celltilldelning i biblioteket till nästa högre enhetsstyrka – t.ex. NAND2_1X till NAND2_2X.

Med FinFLEX finns ytterligare alternativ tillgängliga med det andra biblioteket – t.ex. om en uppdatering till NAND2_1X_2:2 skulle använda NAND2_2X_2:2 eller NAND2_1X_3:2. Men om det senare väljs måste den nya cellen "ombalanseras" till en annan rad i blockplanen. De effektiva förändringarna i prestanda och in-/utgångsledningsbelastning för dessa val är komplicerade att uppskatta under fysisk syntes (för att inte tala om de specifika RDLY- och FDLY-fördröjningsövergångarna för utmatning som stiger mot fall för de olika bibliotekscellerna kan skalas olika).

Cellvalsalternativen blir ännu mer komplicerade när man överväger att använda specifika floppceller, inte bara med tanke på skillnaderna i klocka-till-Q-fördröjningar, utan också inställnings- och hålltidsegenskaperna och ingångsklockladdning. När skulle det vara bättre för enskilda floppbitar i ett register att använda olika drivstyrkor i samma bibliotek (och placeras lokalt) jämfört med att ha registerbitar ombalanserade till en rad som motsvarar ett annat biblioteksval?

- IP-integration på subblocknivå

Block innehåller ofta ett antal små hårda IP-makron, såsom registerfiler (som vanligtvis tillhandahålls av en registerfilgenerator). Med olikformiga cellradshöjder som spänner över ett enskilt block, hur kommer dessa hårda IP-makron att utformas och placeras?

- timing/effektoptimeringar under fysisk design

I likhet med de fysiska syntesblockskonstruktionsalternativen kommer det att finnas svåra beslut om cellval under timing- och effektoptimeringsstegen i det fysiska designflödet. Till exempel, om en cell kan minska sin tilldelade enhetsstyrka för att spara ström samtidigt som den uppfyller timing, skulle en förändring av biblioteksurvalet, och därmed radombalansering, övervägas? Skulle förändringarna i cellplaceringen motverka optimeringen?

och sist men absolut inte minst,

- Kommer det att finnas nya EDA-licenskostnader för att aktivera N3E FinFLEX?

(För flera år sedan gick CAD-avdelningschefen hos en tidigare arbetsgivare till mig viral i licenskostnadsadderaren för att möjliggöra placering och routing för flermönsterkrav. Med tanke på den betydande EDA-investering som krävs för att stödja FinFLEX, kommer historien sannolikt att upprepa sig med ytterligare kostnader för licensfunktioner .)

FinFLEX-metoden erbjuder definitivt några spännande alternativ. Det ska bli oerhört intressant att se hur detta tillvägagångssätt utvecklas.

Migrationsautomation för analog design

Slutligen belyste TSMC kortfattat arbete de bedriver inom området för att hjälpa designers att migrera analoga/blandade signalkretsar och layouter till nyare processnoder.

Specifikt har TSMC definierat en uppsättning "analoga celler", med förmågan att ta ett befintligt schema, mappa om till en ny nod, utvärdera kretsoptimeringar och migrera layouter, inklusive automatisk placering och (PG + signal) routing.

Definitionen av de analoga cellbiblioteken för N5/N4 och N3E är komplett, med N7/N6-stöd att följa. TSMC visade ett exempel på en operationell transkonduktansförstärkare (OTA) som hade gått igenom migreringsflödet.

Se efter mer information att följa. (Detta initiativ verkar överlappa med jämförbara funktioner tillgängliga från EDA-leverantörens anpassade fysiska designplattformar.)

En efterföljande artikel kommer att täcka TSMC:s avancerade förpackningsmeddelanden vid 2022 Technology Symposium.

-chipkille

Läs också:

Tre viktiga takeaways från 2022 TSMC Technical Symposium!

Invers litografiteknik – en statusuppdatering från TSMC

TSMC N3 kommer att vara en rekordinställningsnod!

Dela det här inlägget via: