Att definiera om en 2.5D-enhet är ett tryckt kretskort som krympts ner för att passa in i ett paket, eller ett chip som sträcker sig utanför gränserna för en enda stans, kan verka som hårklyvande semantik, men det kan få betydande konsekvenser för den övergripande framgången av en design.

Plana spån har alltid varit begränsad av storleken på hårkorset, som är cirka 858 mm2. Utöver det gör avkastningsproblem kiseln oekonomisk. I åratal har det begränsat antalet funktioner som kan träs in på ett plant underlag. Eventuella ytterligare funktioner skulle behöva utformas till ytterligare chips och kopplas till ett kretskort (PCB).

Tillkomsten av 2.5D förpackningsteknik har öppnat en helt ny axel för expansion, vilket tillåter flera chiplets att vara sammankopplade inuti en avancerat paket. Men utgångspunkten för denna paketerade design kan ha stor inverkan på hur de olika komponenterna sätts ihop, vem som är inblandad och vilka verktyg som används och när.

Det finns flera anledningar till att 2.5D vinner mark idag. En är kostnad. "Om du kan bygga mindre chips, eller chiplets, och dessa chiplets har designats och optimerats för att integreras i ett paket, kan det göra det hela mindre", säger Tony Mastroianni, chef för avancerade förpackningslösningar på Siemens Digital Industries-programvara. "Och eftersom avkastningen är mycket högre, har det en dramatisk inverkan på kostnaden. Istället för att ha en avkastning på 50 % eller lägre för spånstorlekar, kan du få det upp till 90 %."

Att sammankoppla chips med ett kretskort begränsar också prestandan. "Historiskt sett hade vi chips förpackade separat och sedan satt på PCB och kopplade ihop med lite routing", säger Ramin Farjadrad, VD och medgrundare av Eliyan. "Problemen som människor började möta var tvåfaldiga. En var att bandbredden mellan dessa chips begränsades genom att gå igenom PCB och sedan ett begränsat antal bollar på paketet, vilket begränsade anslutningen mellan dessa chips."

Den viktigaste skillnaden med 2.5D jämfört med ett PCB är att 2.5D använder chipdimensioner. Det finns mycket finare trådar och olika komponenter kan packas mycket närmare varandra på ett mellanlägg eller i en förpackning än på en bräda. Av dessa skäl kan ledningar vara kortare, det kan bli fler av dem och bandbredden ökas.

Det påverkar prestandan på flera nivåer. "Eftersom de är så nära har du inte de långa transport-RC- eller LC-förseningarna, så det går mycket snabbare", säger Siemens Mastroianni. "Du behöver inte stora drivrutiner på ett chip för att köra långa spår över brädan, så du har lägre effekt. Du får storleksordningar bättre prestanda — och lägre effekt. Ett vanligt mått är att prata om pico joule per bit. Mängden energi som krävs för att flytta bitar gör 2.5D övertygande."

Ändå påverkar tankesättet det ursprungliga designkonceptet, och det får återverkningar genom hela flödet. "Om du pratar med en formdesigner kommer de förmodligen att säga att det bara är ett stort chip", säger John Park, produktledningsgruppchef i Custom IC & PCB Group på Kadens. "Men om du pratar med en paketdesigner, eller en kortdesigner, kommer de att säga att det i grunden är en liten PCB."

Vem har rätt? "Den interna organisationsstrukturen inom företaget avgör ofta hur det här grips", säger Marc Swinnen, direktör för produktmarknadsföring på Ansys. "Långsiktigt vill du se till att ditt företag är strukturerat för att matcha fysiken och inte försöka matcha fysiken ditt företag."

Det som är tydligt är att ingenting är säkert. "Den digitala världen var väldigt regelbunden eftersom vi vartannat år fick en ny nod som var halvstor", säger Cadence's Park. ”Det skulle finnas några nya krav, men det var väldigt evolutionärt. Förpackningar är vilda västern. Vi kanske får 8 nya förpackningstekniker i år, 3 nästa år, 12 nästa år. Många av dessa kommer från gjuterierna, medan det brukade bara komma från de outsourcade halvledarmonterings- och testföretagen (OSAT) och substratleverantörerna. Medan gjuterierna är en ny deltagare, erbjuder OSAT:erna några riktigt intressanta förpackningstekniker till en lägre kostnad."

En del av anledningen till detta är att olika grupper av människor har olika kravuppsättningar. "Regeringen och militären ser de främsta fördelarna som heterogen integrationsförmåga", säger Ansys' Swinnen. "De pressar inte på kanten av processteknik. Istället designar de saker som monolitiska mikrovågsintegrerade kretsar (MMIC), där de behöver vågledare för mycket höghastighetssignaler. De närmar sig det från en förpackningsmonteringssynpunkt. Omvänt närmar sig högpresterande beräkningsföretag (HPC) det från en hög med 5nm och 3nm chips med högpresterande högbandbreddsminne (HBM). De ser det som ett kiselmonteringsproblem. Fördelen de ser är flexibiliteten i arkitekturen, där de kan lägga in kärnor och gränssnitt och skapa produkter för specifika marknader utan att behöva designa om varje chiplet. De ser flexibilitet som fördelen. Militären ser heterogen integration som fördelen.”

material

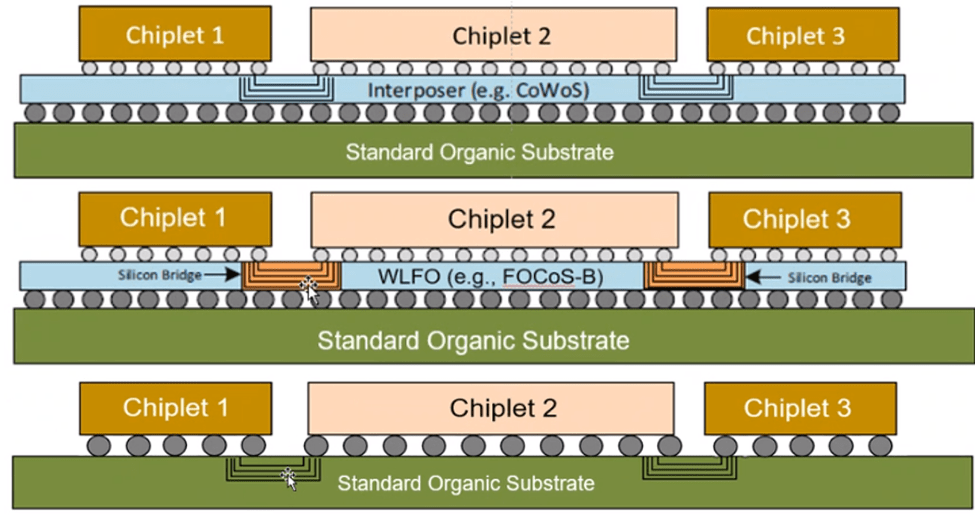

Det finns flera material som används som substrat i 2.5D-förpackningsteknik, som vart och ett har olika kompromisser vad gäller kostnad, densitet och bandbredd, tillsammans med var och en har ett urval av olika fysiska problem som måste övervinnas. En av de primära differentieringspunkterna är bump-pitch, som visas i figur 1.

Fig 1. Chiplets sammankoppling för olika substratkonfigurationer. Källa: Eliyan

När man talar om en interposem, anses det i allmänhet vara kisel. "Interposern kan vara en stor bit kisel (fig 1 överst), eller bara kiselbryggor mellan chipsen (fig 1 mitten) för att tillhandahålla anslutningen", säger Eliyans Farjadrad. ”Båda dessa lösningar använder mikrobulor, som har hög densitet. Mellanlägg och broar ger många högdensitetsbulor och spår, och det ger dig bandbredd. Om du använder 1,000 5 ledningar som var och en går på 5 Gb får du 10,000 Tb. Om du har 50 1 får du 5 Tb. Men de signalerna kan inte gå mer än två eller tre millimeter. Alternativt, om du undviker kiselmellanlägget och du stannar med ett organiskt paket (bild 10 längst ner), såsom flip chip-paket, är densiteten för spåren 5X till 10X mindre. Tjockleken på trådarna kan dock vara 5X till 25X mer. Det är en betydande fördel, eftersom trådarnas motstånd kommer att sjunka med kvadraten på tjockleken på trådarna. Tvärsnittet på den tråden går upp med kvadraten på den tråden, så motståndet minskar avsevärt. Om det är XNUMX gånger mindre densitet betyder det att du kan köra signaler nästan XNUMX gånger längre.”

För vissa människor handlar det om bandbredd per millimeter. "Om du har en parallell buss, eller ett parallellt gränssnitt som är höghastighets, och du vill ha bandbredd per millimeter, så skulle du förmodligen välja en kiselmellanläggare", säger Kent Stahn, senior manager för hårdvaruteknik på Synopsys' Solutions Group. "Ett organiskt substrat är lågförlust, låg kostnad, men det har inte densiteten. Däremellan finns det ett gäng lösningar som klarar en del av det, men inte för samma kostnad.”

Det finns andra skäl att välja ett substratmaterial också. "Silicon interposer kommer från ett gjuteri, så tillgänglighet är ett problem", säger Manuel Mota, senior personal produktchef i Synopsys Solutions Group. "Vissa företag står inför utmaningar när det gäller att köpa avancerade paket eftersom kapaciteten tas. Genom att gå till andra tekniker som har lite mindre bandbreddstäthet, men kanske tillräckligt för din applikation, kan du hitta dem någon annanstans. Det blir en kritisk aspekt."

Alla dessa tekniker går dock snabbt framåt. "Räketgränsen är cirka 858 mm i kvadrat", säger Park. ”Folk pratar om mellanlägg som kanske är fyra gånger så stora, men vi har laminat som blir mycket större. Vissa av laminatsubstraten som kommer från Japan närmar sig samma nivå av sammankopplingstäthet som vi kan få från kisel. Jag ser personligen mer tryck mot organiska substrat. Chip-on-Wafer-on-Substrate (CoWoS) från TSMC använder en kiselmellanläggare och har varit den teknik som valts ut i cirka 12 år. Mer nyligen introducerade de CoWoS-R, som använder filmpolyamid, närmare en organisk typ av substrat. Nu hör vi mycket om glassubstrat.”

Med tiden kan den totala fastigheten i paketet växa. "Det är inte vettigt för gjuterier att fortsätta bygga saker som är lika stora som ett 30-tums kretskort", tillägger Park. "Det finns material som kan möta de större designerna. Där vi verkligen behöver täthet är dö-till-dö. Vi vill ha de där chipletarna bredvid varandra, ett par millimeters sammankopplingslängd. Vi vill ha saker väldigt korta. Men resten av det är bara att fläkta ut I/O så att den ansluts till PCB.

Det är därför broar är populära. "Vi ser en utveckling till broar för höghastighetsdelen av gränssnittet", säger Synopsys' Stahn. "Baksidan av det skulle vara fanout, som RDL fanout. Vi ser RDL-paket som kommer att bli mer som traditionella paket framöver."

Interposers erbjuder ytterligare möjligheter. "I dag är 99% av interposers passiva", säger Park. "Det finns ingen front end of line, det finns inga enhetslager. Det är enbart back end of line-behandling. Du lägger till tre, fyra, fem metallskikt till det kislet. Det är vad vi kallar en passiv interposer. Det är bara att skapa den där kopplingen mellan dö och dö. Men det finns människor som tar den dien och gör den till en aktiv mellanläggare, och lägger i princip logik till det."

Det kan hända i olika syften. "Du ser redan några företag som gör aktiva interposers, där de lägger till energihantering eller någon av kontrolllogikerna", säger Mota. "När du börjar sätta aktiva kretsar på interposer, är det fortfarande en 2.5D-integration, eller blir det en 3D-integration? Vi ser ingen stor trend mot aktiva mellanläggare idag.”

Det finns dock några nya problem. "Du måste överväga oöverensstämmelse mellan termisk expansionskoefficient (CTE), säger Stahn. "Detta händer när två material med olika CTE binds samman. Låt oss börja med kiselmellanlägget. Du kan få system med högre watt, där SoCs kan prata med sina kamrater, och det kan förbruka mycket ström. En kiselmellanläggare måste fortfarande gå i ett paket. CTE-felmatchningarna är mellan kisel och förpackningsmaterial. Och med bryggan använder du den där du behöver den, men det är fortfarande kisel-till-dö. Du måste göra den termiska mekaniska analysen för att försäkra dig om att den kraft du levererar, och de CTE-fel som du har, resulterar i ett fungerande system."

Medan signallängder i teorin kan bli längre, ställer detta till vissa problem. "När du gör de där långa anslutningarna inuti ett chip, begränsar du vanligtvis dessa vägar till ett par millimeter, och sedan buffrar du det", säger Mastroianni. "Problemet med en passiv kiselmellanläggare är att det inte finns några buffertar. Det kan verkligen bli ett allvarligt problem. Om du behöver göra dessa kopplingar måste du planera dem mycket noggrant. Och du måste se till att du kör timinganalys. Vanligtvis kommer dina paketkillar inte att göra den analysen. Det är mer ett problem som har lösts med statisk timinganalys av kiselingenjörer. Vi behöver införa ett STA-flöde och ta itu med alla extraktioner som inkluderar spår av organiska och kiseltyp, och det blir ett nytt problem. När du börjar komma in i några av de mycket långa spåren, tar inte dina enkla RC-tidfördröjningar, som antas i normala STA-fördröjningsräknare, en del av induktansen och den ömsesidiga induktansen mellan dessa spår, så du kan få allvarliga noggrannhetsproblem för de långa spåren.”

Aktiva mellanlägg hjälper. "Med aktiva interposers kan du övervinna några av långdistansproblemen genom att sätta i buffertar eller signalrepeater", säger Swinnen. "Då börjar det se mer ut som ett chip igen, och du kan bara göra det på kisel. Du har EMIB-tekniken från Intel, där de bäddade in chiplet i interposern och det är en aktiv brygga. Chipet pratar med EMIB-chippet, och de pratar båda med dig genom detta lilla aktiva bryggchip, som inte precis är en aktiv mellanläggare, utan fungerar nästan som en aktiv mellanläggare.”

Men även passiva komponenter ger mervärde. "Det första som görs är att inkludera dikeskondensatorer i interposern", säger Mastroianni. "Det ger dig möjligheten att göra lite bra frikoppling, där det räknas, nära tärningen. Om du lägger ut dem på tavlan förlorar du många av fördelarna för höghastighetsgränssnitten. Om du kan få dem i mellanlägget, precis under där du har snabbväxlingshastighetssignalerna, kan du få en viss lokal frikoppling."

Förutom olika material är det frågan om vem som designar mellanlägget. "Branschen verkar se det som en liten PCB i sammanhanget av vem som gör designen", säger Matt Commens, senior manager för produktledning på Ansys. "Interposers designas vanligtvis av förpackningsingenjörer, även om de är kiselprocesser. Detta gäller särskilt för de högpresterande. Det verkar kontraintuitivt, men de har den signalintegritetsbakgrunden, de har designat transmissionslinjer och minimerat oöverensstämmelse vid sammankopplingar. En traditionell IC-designer arbetar utifrån en komponentsynpunkt. Så visst, branschen säger till oss att de personer de utser att göra det designarbetet är förpackningstyp av personas."

Effekt

Det finns några betydande skillnader i routing mellan PCB och interposers. "Interposer routing är mycket enklare, eftersom antalet komponenter är drastiskt minskat jämfört med PCB", säger Andy Heinig, avdelningschef för effektiv elektronik på Fraunhofer IIS/EAS. ”Å andra sidan är elnätet på mellanläggaren mycket mer komplext på grund av metallskiktens högre motstånd och det faktum att elnätet är utskuret av signalledningar. Routningen för die-to-die-gränssnittet är mer komplex på grund av routingdensiteten."

Kraftleveransen ser väldigt annorlunda ut. "Om du tittar på ett PCB, lägger de dessa stora metallgjutområden inbäddade i lagren, och de rensar ut områden där saker måste gå igenom", säger Park. "Du lägger ner en massa koppar och sedan tar du bort de andra. Vi kan inte bygga en interposer på det sättet. Vi måste deponera sammankopplingen, så kraft- och jordstrukturerna på en kiselmellanläggare kommer att se mer ut som ett digitalt chip. Men signalen kommer att se mer ut som ett PCB- eller laminatpaket."

Routing ser mer ut som ett PCB än ett chip. "Du kommer att se saker som tårar eller filéer där det gör en anslutning till en dyna eller via för att skapa bättre avkastning," tillägger Park. "Rotningsstilarna idag är mer anpassade till PCB än de är till en digital IC, där du bara har 90° ortogonala hörn och rena routingkanaler. För mellanläggare, oavsett om det är kisel eller organiskt, är via ofta större än tråden, vilket är ett klassiskt PCB-problem. Routrarna, om vi pratar om digitala, är återigen mer som ett litet PCB än ett mönster."

TSV kan också skapa problem. "Om du ska behandla dem som fyrkantiga, förlorar du mycket utrymme i hörnen", säger Swinnen. "Du vill verkligen ha 45° runt de där föremålen. Kiselroutrar är traditionellt Manhattan, även om det har funnits en lång tradition av RDL-routing, som är det översta lagret där gupparna är anslutna. Det har traditionellt använt åttakantiga eller runda stötar, och sedan 45° routing. Det är inte lika flexibelt som PCB-routningen, men de har routrar för omfördelningslager, och de har även några routrar som kommer från den fullständiga anpassade sidan som har full river-routing."

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoData.Network Vertical Generative Ai. Styrka dig själv. Tillgång här.

- PlatoAiStream. Web3 Intelligence. Kunskap förstärkt. Tillgång här.

- Platoesg. Kol, CleanTech, Energi, Miljö, Sol, Avfallshantering. Tillgång här.

- PlatoHealth. Biotech och kliniska prövningar Intelligence. Tillgång här.

- Källa: https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/