Durante a GOMACTech conferência realizada na Carolina do Sul na semana passada, tive uma ligação Zoom com Deepak Shankar, fundador e vice-presidente de tecnologia da Mirabilis Design Inc. Visual Sim – uma plataforma de modelagem, simulação, exploração e colaboração para desenvolver eletrônicos e SoCs. O que torna o VisualSim tão distinto é que ele vem com cerca de 500 blocos IP de alto nível prontos para uso, incluindo 35 processadores ARM, cerca de 100 processadores e mais de 30 interconexões diferentes. Os usuários do VisualSim conectam rapidamente esses blocos IP visualmente para criar seus sistemas, completos com redes. Um projetista automotivo pode modelar toda a rede, incluindo comunicações 5G, atualizações Ethernet, SDA e OTA com VisualSim.

Um modelo de alto nível permite a exploração arquitetônica mais rápida e a realização de compensações arquitetônicas, muito antes mesmo de a implementação começar com o código RTL. Você pode modelar atividades complexas como barramento, memórias e até cache, medindo coisas como atrasos e latência de ponta a ponta. Os engenheiros podem medir qual é a proporção de acertos/erros do cache e o que acontece com solicitações para caches L2. Todos os protocolos de rede populares são modelados: AXI, CHI, CMN600, Arteris NOC, UCIe, etc.

Com esta abordagem de modelagem, um arquiteto pode modelar um SoC, uma aeronave completa ou um sistema automotivo, e então começar a medir seu desempenho para ver se ele atende aos requisitos. VisualSim é um simulador multidomínio que pode integrar sistemas analógicos, de software, de energia, digitais e de rede em um único modelo.

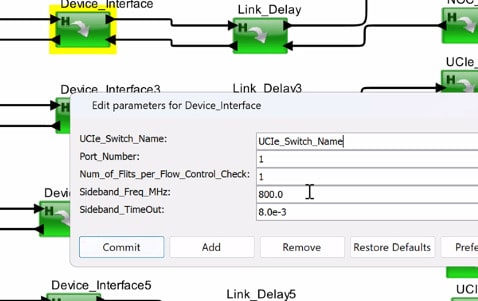

Para a demonstração ao vivo, Deepak me mostrou um design baseado em chiplet que tinha chips separados para DSP, GPU, processador AI e CPU, todos conectados entre si usando UCIe, e cada bloco IP foi parametrizado para permitir personalização e exploração.

Ao inserir o bloco UCIe, havia um IP chamado switch UCIe, e um usuário pode personalizar esse bloco com cinco parâmetros, todos de alto nível.

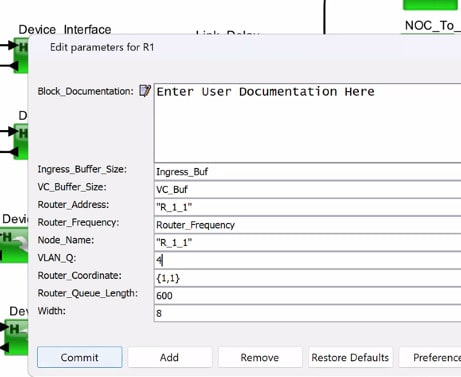

Um bloco IP do roteador possuía 10 parâmetros para customização.

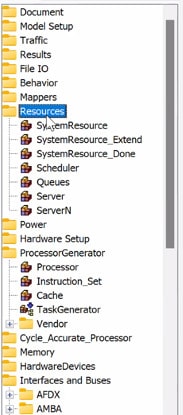

Para encontrar cada bloco IP havia uma lista rolável no lado esquerdo da GUI, com cada família de IP na biblioteca. Em questão de segundos você pode navegar, selecionar e começar a personalizar um IP.

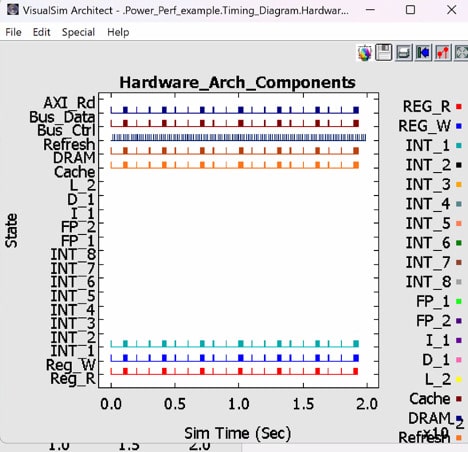

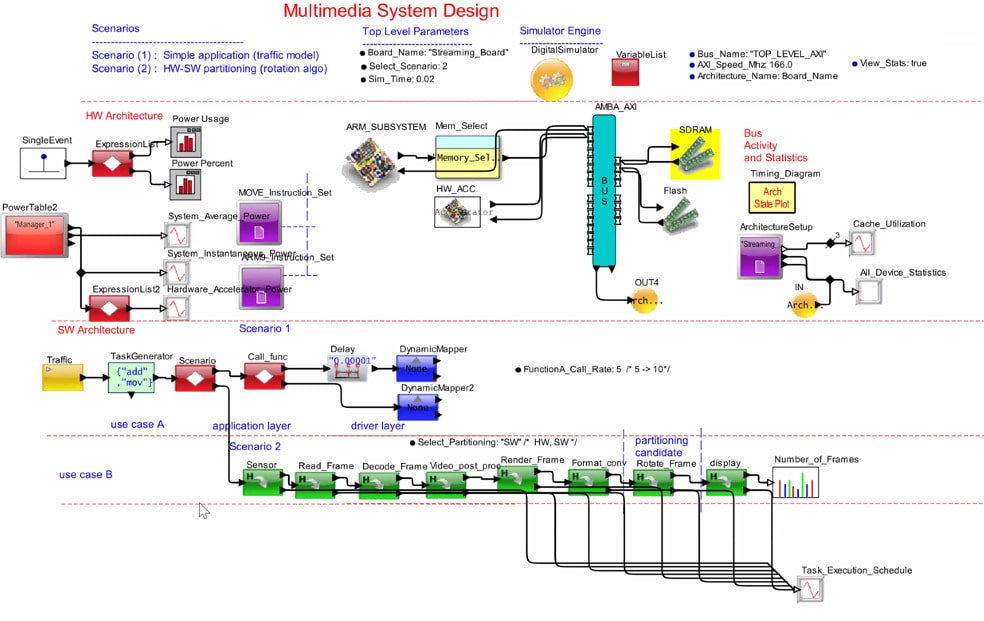

No VisualSim você conecta cada IP no fluxo de dados, permanecendo em um nível alto. A próxima demonstração ao vivo foi para um projeto de sistema multimídia e, para simular 20 ms, foram necessários cerca de 15 segundos de tempo de parede, rodando em um laptop. Enquanto a simulação está em execução, você pode visualizar o desempenho do sistema como potência instantânea, medir a utilização do pipeline, a utilização do cache, o uso da memória e até mesmo visualizar um diagrama de tempo. Esta simulação em tempo real desencadeou 7.5 milhões de eventos, e o cliente construiu este modelo em menos de 2 semanas, que incluiu todo o SoC.

Outro exemplo de cliente mencionado por Deepak inclui 45 masters e foi concluído em cerca de 4 semanas, totalmente testado.

Você pode examinar qualquer um dos blocos de IP e analisar métricas como aprovação/reprovação e, em seguida, entender por que ele falhou. Existe até um mecanismo de IA para ajudar a analisar dados com mais eficiência, como encontrar um buffer overflow que causou uma falha. Enquanto seu modelo está em execução, há análises capturadas para ajudar a medir o desempenho do sistema e identificar gargalos arquitetônicos.

O VisualSim é atualizado duas vezes por ano e há atualizações de patch para quando novos blocos de IP são adicionados. Um arquiteto define requisitos em um arquivo Excel, com métricas como limites de latência e ocupação de buffer.

Os usuários do VisualSim podem definir o intervalo de tamanho da carga útil em termos de bytes, faixas de velocidade e valores preferenciais. O modelo do seu sistema pode ser varrido pelas combinações para encontrar o melhor conjunto de parâmetros. O simulador ainda entende como explorar os valores mínimo, máximo e preferido. Você pode definir quais parâmetros do sistema serão explorados. A seguir foi mostrada uma demonstração do sistema multimídia e depois simulada ao vivo.

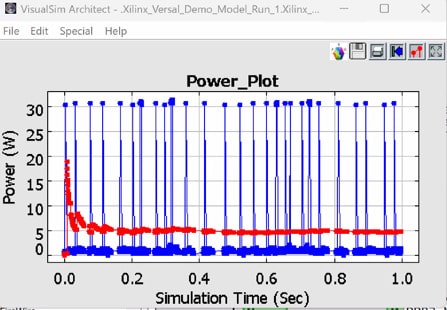

Para um bloco FPGA, você escolhe o fornecedor e o número da peça e, em seguida, pode ver a latência de cada tarefa e as estatísticas do canal do NOC após a execução de uma simulação. Um gráfico de potência foi mostrado para 1 segundo de operação ao usar peças Xilinx Versal.

Todas as demonstrações ao vivo foram executadas em um laptop Windows. Outros sistemas operacionais suportados são: Unix, Mac. A execução do VisualSim requer uma infraestrutura mínima de HW, pois os modelos são de alto nível.

Os usuários do VisualSim recebem mais de 500 exemplos pré-construídos para ajudá-lo a começar rapidamente, como um sistema de comunicação completo com antena, transceptor, FPGA com banda base e interface Ethernet. Os arquitetos de sistemas que usam VisualSim podem colaborar com todos os especialistas de baixo nível, como designers RTL.

As compensações no nível do sistema podem ser modeladas e avaliadas, como:

- Mudando da modulação 64-QAM para QPSK

- Processador mais rápido para mais lento

- Alterando as especificações Ethernet

Se você começar com o VisualSim para modelar, implementar e depois medir, espere ver 95% de precisão em comparação com os resultados da implementação RTL. A promessa de usar modelos de alto nível é eliminar problemas de desempenho antes da implementação ou integração. Na verdade, não há necessidade de codificação para um modelo de sistema inteiro.

A Mirabilis tem até agora 65 clientes em todo o mundo e cerca de 250 projetos concluídos. Alguns dos clientes conhecidos incluem: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Sumário

Antigamente, um designer de sistemas poderia ter desenhado suas ideias em um guardanapo enquanto comia em um restaurante e depois voltar ao trabalho e juntar algumas planilhas do Excel com equações misteriosas para criar um modelo. Hoje há uma nova escolha, e isso é dar Visual Sim de Mirabilis uma tentativa. Agora você pode modelar um sistema inteiro em apenas algumas semanas, além de fazer compensações arquitetônicas enquanto executa simulações reais, tudo antes de entrar em detalhes detalhados de implementação.

Blogs relacionados

Compartilhe esta postagem via:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/