Há vários anos, tenho me encontrado com AMIQ EDA o cofundador Cristian Amitroaie a cada poucos meses para discutir o estado da indústria, as principais tendências em design e verificação e as maneiras como elas ajudam a facilitar e acelerar o desenvolvimento de chips. Notei um novo recurso interessante mencionado em seu último comunicados à CMVM, então pedi mais informações ao Cristian. Isto levou a uma discussão animada e interessante.

A maioria dos designers e engenheiros de verificação escrevem seu código no SystemVerilog atualmente, mas há exceções. Alguns aproveitam as ferramentas de síntese de alto nível (HLS) para projetar em SystemC ou outras linguagens um pouco mais abstratas que SystemVerilog. Outros escrevem em suas próprias linguagens e usam ferramentas personalizadas para gerar os arquivos SystemVerilog usados para simulação, verificação formal, síntese e outras etapas do processo de desenvolvimento.

Cristian disse que eles ocasionalmente veem um meio-termo em que os engenheiros escrevem código que é principalmente SystemVerilog, mas também contém instruções de “pré-processador” em linguagens estabelecidas, como Perl e a biblioteca Jinja2 do Python, ou em linguagens proprietárias. Eles usam scripts para processar esses arquivos e gerar os arquivos SystemVerilog puros para o restante do fluxo. Perguntei a Cristian como o uso de pré-processadores muda a maneira como os engenheiros usam um ambiente de desenvolvimento integrado (IDE).

Aprendi que os usuários das ferramentas de design e verificação AMIQ EDA (TVP) A família IDE deseja ter acesso a todos os seus recursos favoritos, mesmo ao editar arquivos com código de pré-processador. A equipe AMIQ EDA desenvolveu heurísticas inteligentes para habilitar recursos IDE completos ao editar esses arquivos, assim como fazem com o SystemVerilog puro. Esses recursos incluem hiperlinks de navegação, preenchimento automático, detecção de erros em tempo real, correções rápidas, refatoração e todas as funcionalidades avançadas nas quais os usuários do DVT IDE são viciados.

Isso foi intrigante para mim. Estamos falando sobre “entender” arquivos de idiomas mistos, o que não é algo que qualquer compilador possa digerir facilmente. Para ter certeza de que acertei e que isso é real, Cristian convidou Zeljko Zurzic, líder da equipe que coordenou o desenvolvimento dessa capacidade, para explicar como ela funciona. Ele disse que tudo o que os usuários precisam fazer é informar o DVT IDE sobre o mapeamento entre os arquivos contendo instruções do pré-processador (“arquivo p”) e os arquivos gerados (“arquivo g”).

Isso é feito usando diretivas de compilador dedicadas que suportam vários casos de uso. Por exemplo, existe uma maneira de dizer ao compilador DVT IDE “vá descobrir o arquivo p correspondente a partir do comentário do cabeçalho do arquivo g”. Feito isso, os usuários apenas editam seus arquivos p como se não houvesse nada de especial neles. A compilação incremental dinâmica sinalizará quaisquer erros do SystemVerilog à medida que eles digitam, os hiperlinks os conduzem pelo código, o preenchimento automático e a refatoração funcionam perfeitamente, eles podem solicitar vários diagramas, etc.

As seções que contêm o código do pré-processador são marcadas de forma distinta para que os usuários saibam que serão transformadas em código SystemVerilog. Em TVP Eclipse IDE eles podem ver como o código é gerado usando a Visualização de Inspeção; em DVT IDE para Código VS eles podem “espiar” as transformações. O DVT IDE pode ser configurado para executar automaticamente o script de pré-processamento sempre que o código do pré-processador for alterado. Os usuários podem comparar facilmente o arquivo ap com o arquivo g correspondente, se desejarem.

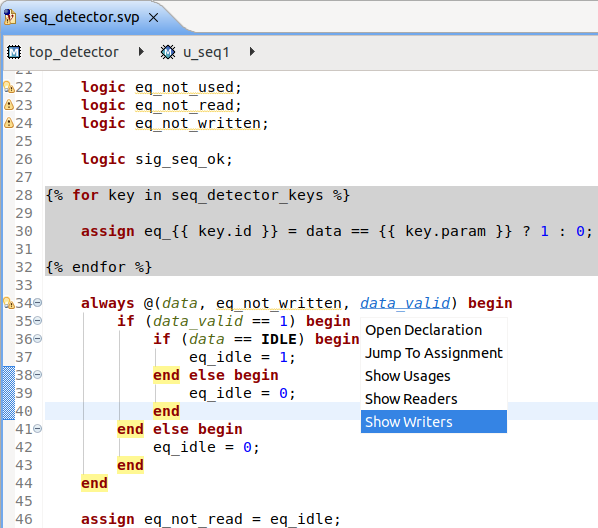

Zeljko forneceu três capturas de tela que mostram esse novo recurso em ação. O primeiro abaixo mostra um arquivo no DVT Eclipse IDE que inclui uma instrução do pré-processador Jinja2. Apesar da presença desse código não SystemVerilog, o usuário pode aproveitar as vantagens do poderoso recurso “Show Writers” para entender rapidamente como uma variável é controlada. Erros de compilação e avisos são indicados na coluna mais à esquerda da tela.

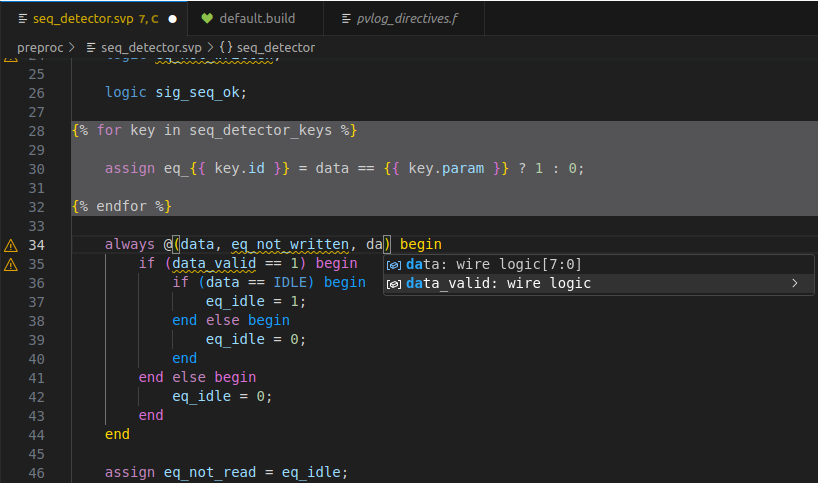

A captura de tela abaixo exibe o mesmo arquivo no DVT IDE para VS Code, mostrando os problemas do compilador na coluna da esquerda e habilitando o uso do preenchimento automático. Isso demonstra como até mesmo as funções DVT mais avançadas estão disponíveis em código com instruções de pré-processador.

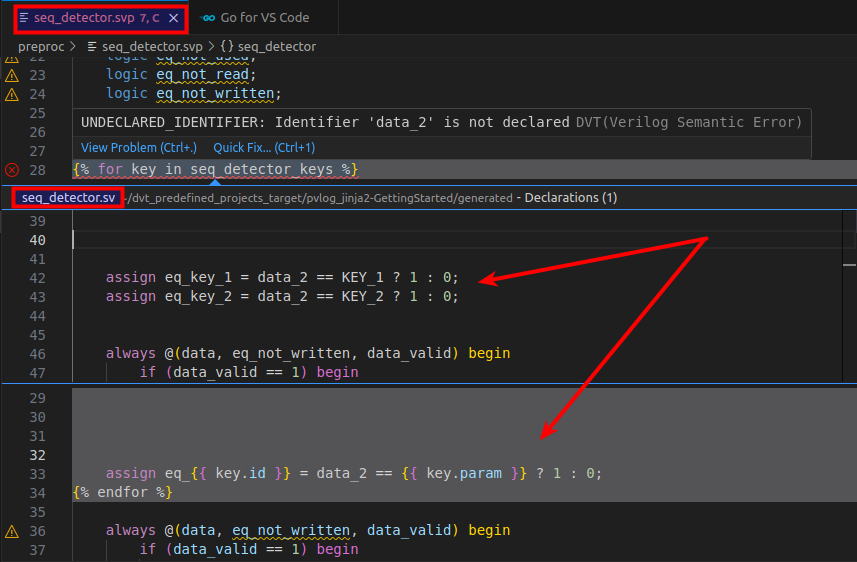

Zeljko enfatizou que o IDE verifica o código SystemVerilog gerado, importante porque pode haver um erro em uma instrução do pré-processador ou um bug no script de pré-processamento. A captura de tela abaixo mostra exatamente esse exemplo. O código SystemVerilog gerado contém uma variável que não foi definida no arquivo de origem. DVT IDE exibe o erro de compilação, o arquivo p e o código gerado no arquivo g.

A visualização dos arquivos g pode ser útil na depuração, mas o resultado final é que os usuários trabalham diretamente com os arquivos p, analisando-os e editando-os usando um IDE poderoso. Os arquivos g são marcados como “somente leitura” e os usuários serão avisados se forem modificados. Fiquei feliz em ouvir isso; todos nós sabemos que é realmente uma má ideia fazer alterações manuais em qualquer arquivo que será substituído por um processo de geração de código.

Por fim, Cristian enfatizou que o objetivo desse novo recurso é que os usuários possam editar o código com instruções do pré-processador como se fosse SystemVerilog puro. Tornar isso possível tem sido um esforço significativo conduzido por alguns clientes importantes que dependem de fluxos baseados em pré-processadores. Agradeci a Zeljko e Cristian pelas explicações e pelo tempo dispensado.

Se quiser saber mais sobre o uso de arquivos de pré-processador ou qualquer aspecto das soluções AMIQ EDA, você pode visitá-los no estande 107 da Conferência e Exposição de Design e Verificação (DVCon) Estados Unidos em San Jose, Califórnia, em 5 e 6 de março.

Leia também:

Perspectivas para 2024 com Cristian Amitroaie, Fundador e CEO da AMIQ EDA

Usando Linting para escrever código de teste livre de erros

AMIQ: Comemora 20 Anos em Consultoria e EDA

Compartilhe esta postagem via:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiwiki.com/eda/amiq-eda/342053-handling-preprocessed-files-in-a-hardware-ide/