A procura incessante por SoCs de menor potência é evidente em muitos mercados. Os exemplos incluem dispositivos móveis, IoT e vestíveis de última geração, juntamente com as altas demandas de computação para comunicações de IA e 5G/6G. Os drivers para baixo consumo de energia incluem a duração da bateria, o gerenciamento térmico e, para aplicações de alta computação, o custo geral de operação. Várias abordagens estão disponíveis para obter baixo consumo de energia. Um ponto comum para muitos é a necessidade de um Foundation IP ideal, ou seja, memórias incorporadas e bibliotecas lógicas. Esta é uma área de investimento significativo e liderança de mercado para a Synopsys. Duas publicações informativas estão agora disponíveis para ajudá-lo a compreender as opções e benefícios disponíveis. Acontece que alcançar um consumo extremamente baixo com os compiladores de memória IP e bibliotecas lógicas da Synopsys Foundation está ao seu alcance.

Vejamos as informações que estão disponíveis.

Boletim técnico

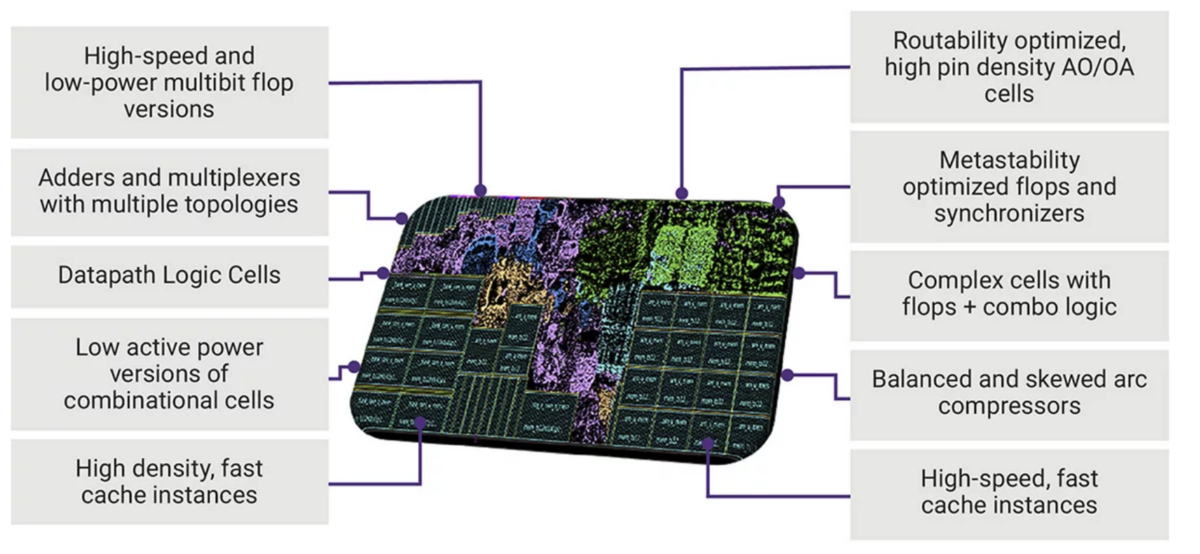

Vou começar com Otimizando PPA para aplicativos HPC e IA com Synopsys Foundation IP, um boletim técnico com foco em bibliotecas lógicas. O artigo fornece detalhes sobre a solução Foundation IP com reconhecimento de ferramentas da Synopsys. São discutidos tópicos como circuitos otimizados, suporte para ampla faixa de tensão operacional e flexibilidade para adicionar otimizações específicas do cliente. O artigo também oferece uma perspectiva sobre como alcançar o máximo desempenho possível ou a melhor relação entre potência e desempenho. A figura abaixo resume os circuitos da biblioteca lógica disponíveis no HPC Design Kit.

Detalhes de como as melhorias de potência são alcançadas são fornecidos em muitas aplicações e estratégias de projeto. Os tópicos abordados incluem escalonamento dinâmico de tensão em uma ampla faixa de tensão operacional, otimização de IA e bloco acelerador específico de aplicação PPA, soluções para rede no chip e como o Synopsys HPC Design Kit é co-otimizado com Synopsys EDA para implementação eficiente de SoC.

Este boletim técnico fornece um rico conjunto de informações e exemplos. Você pode acesse essas informações aqui.

White Paper

Também está disponível um white paper abrangente intitulado, Quão baixo você pode ir? Ultrapassando os Limites dos Transistores. Esta peça investiga memórias incorporadas e bibliotecas lógicas. Ele examina os detalhes por trás da obtenção de potência extremamente baixa. Diversas áreas de aplicação são discutidas, incluindo dispositivos móveis, Bluetooth e IoT, computação de alto desempenho, automotivo e criptografia.

Para memórias embarcadas, diversas abordagens são discutidas, incluindo técnicas de assistência e divisão de tensões de alimentação. Ressalta-se que é necessária uma co-otimização cuidadosa entre a tecnologia e o projeto de circuitos auxiliares de memória para fornecer operação de memória densa e de baixo consumo de energia em baixas tensões. Várias técnicas de assistência aprimorada são revisadas. Melhorias na faixa de potência de 10% a 37%.

A confiabilidade das memórias também é discutida. A peça explica que à medida que a tensão é reduzida, a célula SRAM começa a apresentar degradação. Essa degradação pode causar vários problemas: as leituras são perturbadas, a bitcell não gira, o SER é pronunciado, a detecção falha, os sinais de controle se desviam e o sinal BL enfraquece. Portanto, técnicas de assistência são necessárias para suportar as tensões extremamente baixas exigidas pelas aplicações de baixa potência de ponta.

As abordagens adotadas pela Synopsys aqui fazem uma diferença significativa. São discutidas estratégias para melhorar a confiabilidade e métodos para simular o envelhecimento. Você deve ler os detalhes por si mesmo – um link está chegando. Os dados mostram resultados convincentes, com cinco a dez anos de vida acrescentados.

Bibliotecas lógicas também são discutidas, com estratégias para permitir operação profunda em baixa tensão de 0.4 V e abaixo. A otimização arquitetônica também é revisada. Técnicas de arquitetura de células padrão podem ser empregadas para reduzir a potência dinâmica e de vazamento. Por exemplo, a Synopsys usa técnicas de arquitetura baseadas em pilha versus técnicas baseadas em estágio para a topologia ideal para operação profunda em baixa tensão. A estratégia por trás desta abordagem é apresentada.

A otimização da caracterização também é abordada. Uma parte importante da caracterização é modelar a variação do processo em um SoC, conhecida como variação no chip (OCV). Várias técnicas avançadas são empregadas aqui, incluindo aprendizado de máquina para aumentar a precisão e otimizar o desempenho e a potência.

O white paper conclui com uma visão geral de como reunir tudo no nível SoC para obter operação profunda em baixa tensão. A redução de tensão é discutida, juntamente com técnicas de escala dinâmica de tensão e frequência (DVFS) e várias estratégias de desligamento, como sono leve, sono profundo, desligamento total e modos POFF (Periphery OFF).

Este white paper aborda vários tópicos de otimização de energia com excelentes detalhes. Eu recomendo. Você pode pegue sua cópia aqui. E é assim que é possível alcançar um consumo extremamente baixo com os compiladores de memória IP e bibliotecas lógicas da Synopsys Foundation.

Compartilhe esta postagem via:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/