Nieustające zapotrzebowanie na układy SoC o niższej mocy jest widoczne na wielu rynkach. Przykłady obejmują najnowocześniejsze urządzenia mobilne, IoT i urządzenia do noszenia, a także wysokie wymagania obliczeniowe dla komunikacji AI i 5G/6G. Do czynników wpływających na niski pobór mocy zalicza się czas pracy baterii, zarządzanie temperaturą oraz, w przypadku zastosowań wymagających dużej mocy obliczeniowej, całkowity koszt eksploatacji. Dostępnych jest kilka podejść pozwalających uzyskać niską moc. Wspólnym wątkiem dla wielu jest potrzeba optymalnego Foundation IP, czyli wbudowanych pamięci i bibliotek logicznych. Jest to obszar znaczących inwestycji i wiodącej pozycji rynkowej dla Synopsys. Dostępne są obecnie dwie publikacje informacyjne, które pomogą Państwu zrozumieć dostępne opcje i korzyści. Okazuje się, że osiągnięcie ekstremalnie niskiego poboru mocy za pomocą kompilatorów pamięci IP Synopsys Foundation i bibliotek logicznych jest w zasięgu ręki.

Przyjrzyjmy się dostępnym informacjom.

Biuletyn techniczny

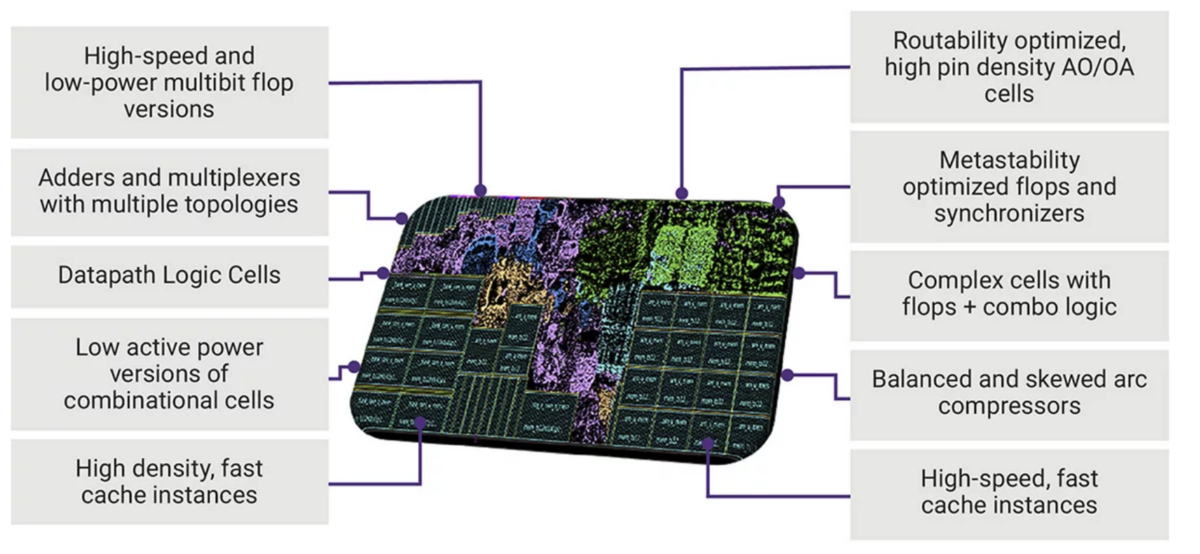

Zacznę od Optymalizacja PPA dla aplikacji HPC i AI za pomocą Synopsys Foundation IP, biuletyn techniczny skupiający się na bibliotekach logicznych. Artykuł zawiera szczegółowe informacje na temat świadomego narzędzi rozwiązania Foundation IP firmy Synopsys. Omawiane są takie tematy, jak zoptymalizowane obwody, obsługa szerokiego zakresu napięcia roboczego i elastyczność w dodawaniu optymalizacji dostosowanych do potrzeb klienta. Artykuł oferuje również perspektywę osiągnięcia maksymalnej możliwej wydajności lub najlepszego kompromisu w zakresie mocy. Poniższy rysunek podsumowuje obwody biblioteki logicznej dostępne w zestawie HPC Design Kit.

Szczegóły dotyczące sposobu osiągnięcia poprawy mocy są dostępne w wielu zastosowaniach i strategiach projektowych. Omawiane tematy obejmują dynamiczne skalowanie napięcia w szerokim zakresie napięcia roboczego, optymalizację sztucznej inteligencji i PPA bloku akceleratora specyficznego dla aplikacji, rozwiązania dla sieci na chipie oraz sposób, w jaki zestaw projektowy Synopsys HPC jest wspólnie optymalizowany z Synopsys EDA w celu wydajnej implementacji SoC.

Niniejszy biuletyn techniczny zawiera bogaty zestaw informacji i przykładów. Możesz uzyskaj dostęp do tych informacji tutaj.

Biała Księga

Dostępna jest także obszerna biała księga pt. Jak nisko możesz zejść? Przesuwanie granic tranzystorów. W tym artykule analizujemy zarówno wbudowane pamięci, jak i biblioteki logiczne. Bada szczegóły stojące za osiągnięciem ekstremalnie niskiej mocy. Omówiono kilka obszarów zastosowań, w tym urządzenia mobilne, Bluetooth i IoT, obliczenia o wysokiej wydajności, motoryzację i kryptowaluty.

W przypadku pamięci wbudowanych omawia się kilka podejść, w tym techniki wspomagania i dzielenie napięć zasilania. Zwraca się uwagę, że wymagana jest staranna optymalizacja technologii i konstrukcji obwodów wspomagających pamięć, aby zapewnić gęstą pracę pamięci o niskim poborze mocy przy niskich napięciach. Omówiono kilka ulepszonych technik wspomagania. Poprawa zakresu mocy od 10% do 37%.

Omówiono także niezawodność pamięci. W artykule wyjaśniono, że wraz ze spadkiem napięcia komórka SRAM zaczyna wykazywać degradację. Ta degradacja może powodować wiele problemów: odczyty są zakłócone, komórka bitowa nie odwraca się, SER jest wyraźny, wykrywanie kończy się niepowodzeniem, sygnały sterujące różnią się i sygnał BL słabnie. Dlatego potrzebne są techniki wspomagające, aby zapewnić obsługę niższych, ekstremalnie niskich napięć wymaganych w najnowocześniejszych zastosowaniach małej mocy.

Podejście zastosowane w tym przypadku przez Synopsys robi znaczącą różnicę. Omówiono strategie poprawy niezawodności i metody symulacji starzenia. Ze szczegółami warto zapoznać się samodzielnie – link już nadchodzi. Dane pokazują przekonujące wyniki, obejmujące wydłużenie życia o pięć do dziesięciu lat.

Omówiono także biblioteki logiczne wraz ze strategiami umożliwiającymi pracę przy głębokim niskim napięciu przy napięciu 0.4 V i niższym. Omówiono również optymalizację architektoniczną. Aby zmniejszyć zarówno moc dynamiczną, jak i moc rozproszenia, można zastosować standardowe techniki budowy ogniw. Na przykład Synopsys wykorzystuje techniki architektury oparte na stosie, a nie na stopniach, aby uzyskać optymalną topologię do pracy przy głębokim niskim napięciu. Przedstawiono strategię stojącą za tym podejściem.

Omówiono także optymalizację charakterystyki. Ważnym elementem charakterystyki jest modelowanie zmienności procesu w całym SoC, określane jako zmienność chipa (OCV). Zastosowano tu kilka zaawansowanych technik, w tym uczenie maszynowe, aby zwiększyć dokładność i zoptymalizować wydajność i moc.

Biała księga kończy się omówieniem, jak złożyć wszystko razem na poziomie SoC, aby uzyskać głęboką pracę przy niskim napięciu. Omówiono redukcję napięcia, techniki dynamicznego skalowania napięcia i częstotliwości (DVFS) oraz różne strategie wyłączania, takie jak lekki sen, głęboki sen, pełne wyłączenie i tryby POFF (wyłączenie urządzeń peryferyjnych).

W tym dokumencie szczegółowo omówiono szereg tematów związanych z optymalizacją zasilania. Gorąco polecam. Możesz zdobądź swoją kopię tutaj. I w ten sposób osiągnięcie ekstremalnie niskiego poboru mocy dzięki kompilatorom pamięci IP Synopsys Foundation i bibliotekom logicznym jest w zasięgu ręki.

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/