IC-ontwerpen hebben fysieke verificatietoepassingen zoals Layout Versus Schematic (LVS) op transistorniveau om ervoor te zorgen dat lay-out en schema's gelijkwaardig zijn. Daarnaast is er een Electrical Rules Check (ERC) voor verbindingen met brongebieden, een zogenaamde zachte controle. De verbindingen met alle apparaten moeten de meest consistente spanningssignalen hebben. Daarom moet het pad door de metaallagen lopen om de weerstand en factoren zoals IR Drop te verminderen. Het detecteren van verbindingen vond dat andere materialen, zoals Wells, verplicht waren. Soft-Checks zijn de meest gebruikte methode om deze situatie op te sporen. De kaliber productlijn van Siemens is het populairste hulpmiddel voor DRC- en LVS-controle, dus las ik een technisch artikel van Terry Meeks voor meer informatie over zachte controles.

Het verbinden van twee metaallagen in een IC-lay-out vereist een nauwkeurige uitlijning van beide metaallagen en de via-laag. Hier is een vergelijking waarbij zowel een zijaanzicht als een bovenaanzicht wordt gebruikt, waarbij het eerste voorbeeld niet met elkaar is verbonden, omdat Metaal1 en Metaal 2 elkaar niet overlappen, terwijl het tweede voorbeeld correct is verbonden.

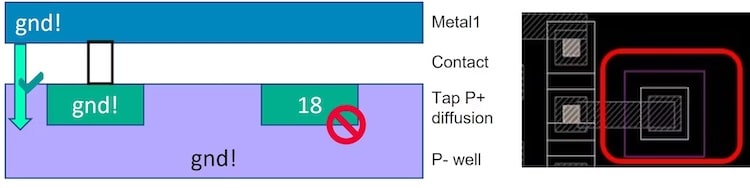

We willen dat onze ERC-tool tijdens zachte controles putconnectiviteitsfouten identificeert, zodat deze kunnen worden verholpen. De volgende IC-lay-out heeft een putconnectiviteitsfout en wordt getoond vanuit het zijaanzicht, waar het Metal1-signaal met de tekst Gnd is verbonden met een diffusiegebied dat tapdiffusie wordt genoemd. Aan de rechterkant bevindt zich nog een Metal1-laag met een tikdiffusie, maar deze connectiviteit creëert een pad met hoge weerstand in de Rwell naar Gnd, en wordt door de zachte controle als een fout gemarkeerd.

Een ander voorbeeld van een zachte connectiviteitsfout doet zich voor in de onderstaande IC-indeling, waar we slechts één naam per polygoon kunnen toepassen. Het digitale stroomnet VDD kan niet naast het analoge stroomnet AVDD bestaan, en we moeten deze in twee vormen verdelen. Zachte controles helpen deze problemen te signaleren.

Een IC-lay-out met zowel digitale als analoge voedingen kan nogal complex worden om goed te lay-outen, dus het is nog belangrijker om zachte controles te hebben.

Zachte controles zijn inbegrepen tijdens uw LVS-runs, en bij Kaliber nmLVS er is een rapport met de resultaten van de zachte controle, die u vervolgens kunt bekijken met behulp van de Kaliber RVE kijker.

Als u op RVE-resultaten klikt, ziet u welke cel de zachte controlefout heeft, de netnamen, de boven- en ondernamen en andere eigenschappen. Deze informatie helpt bij het bepalen van wat er moet worden opgelost in de IC-indeling. Als u op een lagere laag zoals een PWell klikt voor een zachte controlefout, wordt de geometrie in het geel weergegeven.

Voor dezelfde zachte controlefout wordt door op de bovenste laag te klikken het volgende weergegeven:

Tijdens het debuggen kunt u ook alle vormen van de bovenste laag weergeven. De groene vormen zijn de geselecteerde vormen van de netto bovenlaag, terwijl geel de afgewezen vorm van de netto bovenlaag is.

Bij het debuggen van soft-checkfouten met RVE moet u klikken op de connectiviteit van geselecteerde en afgewezen netten. Een Net Info-venster onthult details zoals om welke lagen het gaat en of vormen connectiviteit missen. Als je kijkt welke poorten op een net zijn aangesloten, kun je zien of er VDD- of GND-fouten ontbreken. Dit voorbeeld laat zien dat net 18 wordt afgewezen omdat er geen connectiviteit met Metal1 is.

Samengevat

LVS-controles zijn verplicht om ervoor te zorgen dat een IC een foutloze lay-out heeft, en zachte controles maken deel uit van uw LVS-controles. Er is een bewezen foutopsporingsstroom van Siemens in hun Caliber nmLVS-tool die RVE gebruikt om lay-outontwerpers te helpen snel fouten in de zachte controles te identificeren, zodat ontwerpers verbeteringen kunnen aanbrengen en opnieuw kunnen verifiëren totdat alle controles zijn geslaagd. Siemens heeft een technisch artikel geschreven om online te lezen, Detecteren en debuggen van softcheck-connectiviteitsfouten.

Gerelateerde blogs

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/eda/342526-soft-checks-are-needed-during-electrical-rule-checking-of-ic-layouts/