In het tijdperk van snelle technologische innovatie ontwikkelen hyperscale datacenters zich in een razend tempo. Met de voortdurende vooruitgang op het gebied van CPU's, GPU's, accelerators en switches is snellere gegevensoverdracht nu van het grootste belang. In de voorhoede van deze vooruitgang staat PCI Express (PCIe®), dat de de facto standaard is geworden voor interconnectie voor snelle gegevensoverdracht tussen verwerkings- en computerknooppunten.

Verdubbeling van de datasnelheden: de trend zet zich voort

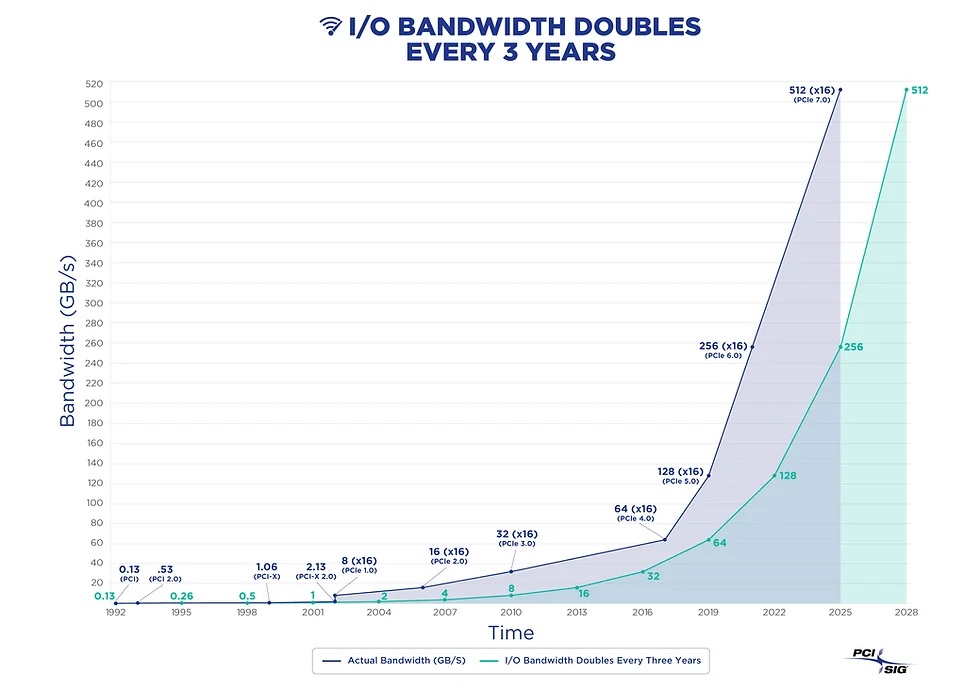

Het PCI-SIG®-consortium, verantwoordelijk voor de PCIe-interface, heeft een geschiedenis van het lanceren van ongeveer elke drie jaar een nieuwe PCIe-generatie. Hierdoor is de datasnelheid de afgelopen tien jaar steevast verdubbeld. PCI-SIG's nieuwste release, PCIe 6.0.1, luidt multi-level Pulse Amplitude Modulation (PAM4)-signalering in, met een duizelingwekkende overdrachtssnelheid van 64 GT/s in één richting op één rijstrook. Met name tijdens de PCI-SIG DevCon van 2022 werd de PCIe 7.0-specificatie aangekondigd, waarbij de datasnelheid werd verdubbeld tot 128 GT/s, waarbij zowel de energie-efficiëntie als de hogere bandbreedte werden benadrukt.

Figuur 1. PCI-SIG I/O-bandbreedte verdubbelt elke drie jaar. Van PCI-SIG

Strenge tests voor naleving en interoperabiliteit

Het is belangrijk om te begrijpen dat de inzet van PCIe-technologie, naast grootschalige datacenters, op gebieden als draagbare apparaten, servers, auto's, industriële toepassingen en meer, een hoge betrouwbaarheid en kosteneffectiviteit vereist. Dit vereist rigoureuze nalevingstests voor producten om ervoor te zorgen dat ze voldoen aan de PCIe 6.0.1-specificatie en met succes kunnen samenwerken met andere PCIe-apparaten.

Onthulling van PAM4-signalering en de implicaties ervan

De integratie van PAM4-signalering in PCIe 6.0.1 is cruciaal. In tegenstelling tot de Non-Return-to-Zero (NRZ)-signalering, die twee verschillende signaalniveaus gebruikte, gebruikt PAM4 er vier, waarbij twee bits aan informatie worden verzonden binnen een enkel eenheidsinterval (UI). Deze aanpassing introduceert nieuwe uitdagingen zoals overspraakinterferenties, signaalreflecties en voedingruis. De PCIe 6.0.1-specificatie heeft de Signal-to-Noise Distortion Ratio (SNDR) geïntroduceerd om deze uitdagingen aan te pakken, waarbij zowel de traditionele ruis als niet-compenseerbare beperkingen in het elektrische signaal worden ingekapseld. Het begrijpen van signaalintegriteitsproblemen in de hogesnelheidscommunicatiekanalen als gevolg van overspraak en reflectieverliezen met frequentie- en tijddomeinanalyse is de sleutel. Kanaalmeettechnieken en verschillende signaalverbeteringstechnieken met PCIe 6.0 zender- en ontvanger-equalisatie worden gebruikt om niet-ideale kanaalkarakteristieken te compenseren.

Samengevat

De vooruitgang in de PCIe-technologie heeft de weg vrijgemaakt voor een nieuw tijdperk van mogelijkheden voor gegevensoverdracht, waarbij PCIe 6.0.1 en de aanstaande PCIe 7.0 nieuwe maatstaven stellen. Met grotere capaciteiten komen echter grotere uitdagingen, vooral op het gebied van het garanderen van compliance en interoperabiliteit. Partnerschappen als Synopsys en Tektronix lopen voorop bij het aanpakken van deze uitdagingen en zorgen ervoor dat de technologie niet alleen voldoet aan de eisen van het huidige digitale tijdperk, maar deze zelfs overtreft.

Neem deel aan ons webinar!

Wilt u dieper ingaan op PCIe-simulaties en elektrische tests? Neem deel aan ons komende webinar op dinsdag 10 oktober van 9 uur tot 00 uur PDT, waar experts uit de industrie van Synopsys en Tektronix het nieuwste op het gebied van PCIe-technologie en het belang van robuuste testmethoden zullen bespreken. Klik hier om je nu in te schrijven!

Sprekers:

David Bouse is een Principal Technology Leader bij Tektronix en levert een actieve bijdrage aan PCI-SIG met expertise op het gebied van hogesnelheids-SERDES, waaronder testmethodologieën voor zenders en ontvangers, DSP-algoritmen voor NRZ/PAM4-signalering, klokkarakterisering en automatiseringssoftware-architectuur.

Madhumita Sanyal is Sr. Staff Technical Manager voor Synopsys snelle SerDes-portfolio. Ze heeft +17 jaar ervaring in het ontwerp en de toepassing van ASIC WLAN-producten, logische bibliotheken, ingebedde herinneringen en mixed-signal IP.

Over Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is de Silicon to Software™-partner voor innovatieve bedrijven die de elektronische producten en softwaretoepassingen ontwikkelen waar we elke dag op vertrouwen. Als een S&P 500-bedrijf heeft Synopsys een lange geschiedenis als wereldleider op het gebied van elektronische ontwerpautomatisering (EDA) en halfgeleider-IP en biedt het de breedste portfolio van testtools en -diensten voor applicatiebeveiliging. Of u nu een system-on-chip (SoC)-ontwerper bent die geavanceerde halfgeleiders maakt, of een softwareontwikkelaar die veiligere code van hoge kwaliteit schrijft, Synopsys heeft de oplossingen die nodig zijn om innovatieve producten te leveren. Meer informatie op www.synopsys.com.

Lees ook:

Volgende generatie AI-engine voor intelligente vision-toepassingen

VC formeel ingeschakelde QED-bewijzen op een RISC-V-kern

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. Automotive / EV's, carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- ChartPrime. Verhoog uw handelsspel met ChartPrime. Toegang hier.

- BlockOffsets. Eigendom voor milieucompensatie moderniseren. Toegang hier.

- Bron: https://semiwiki.com/events/333825-why-rigorous-testing-is-so-important-for-pci-express-6-0/