De auto-industrie stelt strenge eisen aan Functionele Veiligheid. Voor halfgeleiderbedrijven die betrokken zijn bij autochips en nog verder upstream bij Silicon Intellectual Property (SIP), is het verkrijgen van ISO 26262-certificering een fundamentele vereiste voor productpenetratie in autotoepassingen. Andes Technology ontwikkelt actief een portfolio van IP-producten van automobielkwaliteit om de efficiëntie van verificatieactiviteiten voor functionele productveiligheid te verbeteren. Eén van de processors uit de serie, de A(X)25MP-processors, beschikt over een ISO 26262-veiligheidscertificering. De A(X)25MP heeft een SIMD-ISA (Single Instruction Multiple Data) die de prestaties versnelt voor signaalverwerkingsbewerkingen die gebruikelijk zijn in een breed scala aan computervereisten in de automobielsector.

Naast uitbreidingen met drijvende komma zijn de processors uit de 25-serie uitgerust met een 5-traps pijplijn die is geoptimaliseerd voor hoge werkfrequentie en hoge prestaties. Ze beschikken ook over instructie- en datacaches, lokale geheugens voor toegang met lage latentie en ECC voor bescherming tegen zachte fouten in L1-geheugen. De processors bieden ook vertakkingsvoorspelling voor efficiënte vertakkingsuitvoering. Gebruikers kunnen het stroom- en energieverbruik regelen via meerdere instellingen voor energiebeheer.

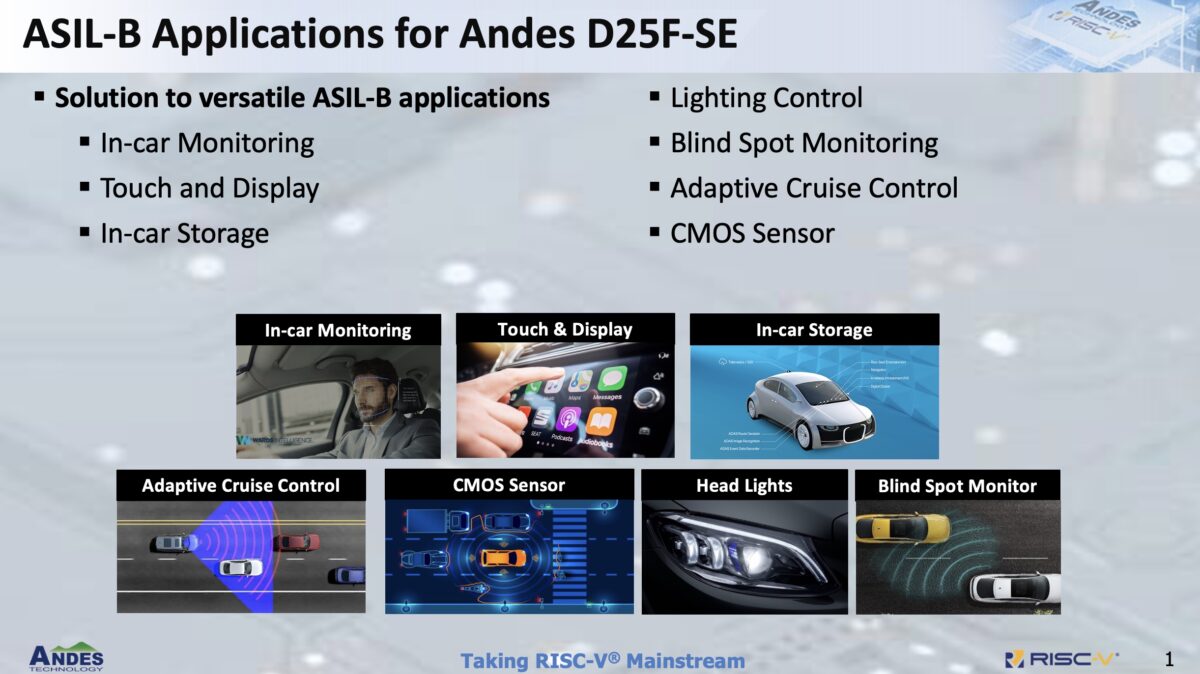

De roadmap van het bedrijf omvat een uitgebreid assortiment IP-producten voor de automobielsector, waaronder RISC-V IP-oplossingen met verschillende functionele veiligheidsniveaus van ASIL-B tot ASIL-D, samen met verschillende processorprestatieniveaus en functiesets. In 2023 zal Andes officieel een 8-traps pipeline dual-issue processor introduceren die voldoet aan de ASIL-D-standaard. Dit duidt op het vermogen van het bedrijf om op maat gemaakte oplossingen te bieden voor diverse automobieltoepassingen, wat hun toonaangevende expertise in de automotive RISC-V IP-markt benadrukt.

Maar een complete oplossing vereist dat een computerplatform een softwaretoolketen heeft die ook voldoet aan de strenge eisen van de automobielwereld. Aan deze eis wordt voldaan door Green Hills Software, een oude Andes-partner. De acceptatie van de RISC-V-instructiesetarchitectuur neemt snel toe in talloze markten, met name in automobieltoepassingen. Dankzij de Green Hills ASIL-gecertificeerde µ-velOSity RTOS, geavanceerde debugger en optimaliserende C/C++-compilers kunnen ontwerpers efficiënt veiligheids- en beveiligingskritische RISC-V-applicaties creëren en met vertrouwen implementeren.

De µ-velOSity RTOS biedt een duidelijke en beknopte application programming interface (API) die de ontwikkelingscyclus verkort. Kernelfuncties die in de RTOS worden ondersteund, omvatten de toewijzing van bronnen. TCP/IP, MS/DOS, USB-apparaat/massaopslagklasse en ingebouwde grafische kaart. µ-velOSity kan worden gebruikt in on-chip-geheugen, waardoor gebruikers een snellere uitvoeringssnelheid krijgen en de noodzaak voor off-chip-geheugen wordt geëlimineerd. Een hogere uitvoeringssnelheid in combinatie met een snelle opstarttijd maakt de software een nuttige oplossing in automobieltoepassingen.

De µ-velOSity RTOS is de kleinste real-time besturingssysteemfamilie van Green Hills Software. Het is bijgewerkt en geoptimaliseerd om de RISC-V-architectuur te ondersteunen en is gecertificeerd om te voldoen aan een groot aantal industrienormen voor functionele veiligheid en beveiliging. Het gestroomlijnde ontwerp, gekoppeld aan de naadloze integratie met de veiligheidsgecertificeerde Green Hills MULTI® geïntegreerde ontwikkelomgeving (IDE) en C/C++-compilers, maakt het gemakkelijk te leren en te gebruiken, waardoor ontwikkelaars geavanceerde oplossingen kunnen creëren met de hoogste prestaties en de kleinste footprint voor automobiel-, industriële en IoT-toepassingen.

Lees ook:

Interview met CEO: Frankwell Lin, voorzitter en CEO van Andes Technology

Door RISC-V-cores te koppelen aan NoC's worden SoC-protocollen met elkaar verbonden

Dieper gelegen RISC-V-pijpleiding ploegt door vector-scalaire lussen

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/events/337484-webinar-leverage-certified-risc-v-ip-to-craft-asil-iso-26262-grade-automotive-chips/