U kent waarschijnlijk de afkorting PPA, wat staat voor Power/Performance/Area. Soms is het PPAC, waarbij C voor kosten staat, omdat er meer aan de hand is dan alleen de oppervlakte. Wist u bijvoorbeeld dat het toevoegen van een extra metaallaag aan een chip de kosten dramatisch verhoogt, soms met miljoenen dollars. Er zijn minimaal twee maskers nodig (interconnect en via's) plus alle aanvullende bijbehorende processtappen. En verbindingslagen komen normaal gesproken in paren, verticaal en horizontaal, dus meestal zijn het vier maskers.

Er zijn veel inputs voor het optimaliseren van PPAC, en een belangrijke is het ontwerpen van de klokboom. De klok kan een groot deel van de stroom verbruiken, en een groot deel van de onderlinge verbinding, en heeft uiteraard invloed op de prestaties. Het proces van het ontwerpen van de klokboom wordt gewoonlijk Clock Tree Synthesis genoemd, meestal afgekort tot CTS. Siemens EDA heeft onlangs een whitepaper gepubliceerd Plaatsing en CTS-technieken voor high-performance computerontwerpen.

Eén uitdaging waarmee EDA-tools worden geconfronteerd, is dat u pas de echte kwaliteit van de resultaten krijgt als u klaar bent met het ontwerp. In de praktijk betekent dit dat tools ofwel pessimisme moeten gebruiken om de resultaten te bewaken, ofwel de nauwkeurigheid moeten vergroten door een veel betere correlatie te hebben tussen de gebruikte tool en de uiteindelijke resultaten.

Het witboek bespreekt hoe de uitdagingen op het gebied van plaatsing en klokboom in HPC-ontwerpen kunnen worden opgelost met behulp van de digitale implementatieoplossing van Aprisa, aangezien deze stappen van fundamenteel belang zijn voor het bereiken van de gewenste prestatiegegevens tijdens plaats en route. Terwijl bij de meeste andere plaats-en-route-tools moet worden gewacht op post-route-optimalisatie om de werkelijke kwaliteit van de resultaten te ontdekken, biedt Aprisa gebruikers een uitstekende correlatie tijdens de plaats-en-route-implementatie, waardoor ontwerpers veel eerder vertrouwen kunnen krijgen in de resultaten. in de stroom bij de fasen plaatsing en klokboomsynthese (CTS). Aprisa is bij uitstek geschikt om ontwerpers te helpen sneller HPC IC-innovaties te realiseren.

Voor het geval u de productnamen van Siemens EDA niet kent (na bijna tien jaar bij Cadence wist ik dat niet): Aprisa is de digitale implementatieoplossing van Siemens voor hiërarchische ontwerpen en ontwerpen op blokniveau. Onder de motorkap heeft het een routegerichte architectuur om de tijd die nodig is om het ontwerp af te ronden te verkorten, deels door de implicaties van beslissingen vroeg in het ontwerpproces naar die fase te trekken, in plaats van te wachten tot het ontwerp voltooid is om erachter te komen dat er problemen zijn die eerder waren gebeurd. eerder geïntroduceerd. Een sleutel tot een moderne implementatiestroom is het hebben van consistente timing, extractie, DRC en meer in de hele stroom.

Aprisa levert optimale prestaties, vermogen en oppervlakte (PPA) voor geavanceerde knooppunten, en biedt volledige ondersteuning voor ontwerpmethodologieën en optimalisatie om zowel het laagste vermogen als de hoogste prestaties te bereiken.

Het witboek gebruikt een voorbeeldontwerp, een Arm Cortex-A76 in 5 nm, draaiend op 2.75 GHz, en gebruikt 12 lagen metaal voor onderlinge verbinding. Ik heb hier geen ruimte om in detail op het ontwerp in te gaan, voor een diepere duik zul je het witboek moeten lezen.

De focus van de oefening was om te analyseren met behulp van 10 lagen metaal versus 12 lagen metaal (ik zei dat verbindingslagen meestal al in paren voorkomen). Uit de analyse kwam naar voren dat bij de 10-laags variant de frequentie met 9 procent verlaagd zou moeten worden om het gewenste vermogensdoel te bereiken. Het resulteerde echter in een aanzienlijke kostenbesparing voor het gehele project. Uiteraard kan Aprisa niet voor u beslissen of een prestatieverbetering van 9% de moeite waard is om de kosten te verlagen.

De focus van het witboek ligt op de klokboomsynthese (CTS), een van de grote uitdagingen bij elk HPC-ontwerp. Aprisa ondersteunt nuttige scheeftrekkingen, beginnend bij plaatsingsoptimalisatie en doorlopend tot aan route-optimalisatie, om ervoor te zorgen dat aan bepaalde uitdagende frequentiedoelen wordt voldaan. Een kracht van de Aprisa CTS-technologie is dat de push- en pull-offsets die tijdens de plaatsingsoptimalisatie worden gegenereerd, worden gerealiseerd tijdens de klokboomimplementatie.

Klokken gaan over het algemeen naar flip-flops, en een optimalisatie die moderne celbibliotheken bevatten zijn multi-bit flip-flops met een gemeenschappelijke klok. Aprisa heeft de mogelijkheid om multi-bit flip-flops samen te voegen of te splitsen en geïntegreerde klokpoorten te klonen/deklonen. Aprisa doet dit op basis van de timing, fysieke locatie van de cellen en kriticiteit van de paden.

Post-CTS-optimalisatie in Aprisa omvat congestieherstel dat congestie herstelt die is ontstaan tijdens de klokboomsynthese. Congestieherstel is een klokbewuste aanpak die de timing niet verslechtert en zo de iteraties terugbrengt naar plaatsingsoptimalisatie die anders nodig zou zijn.

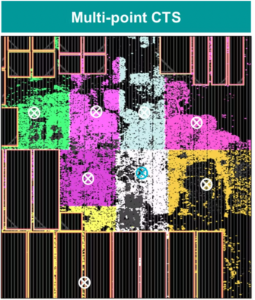

Aprisa ondersteunt verschillende soorten klokboomstructuren zoals H-tree, multi-point CTS en custom mesh. Multi-point is de meest populaire benadering voor HPC-ontwerpen en wordt beschreven in het witboek.

Er komt natuurlijk veel meer bij een implementatiestroom kijken dan het synthetiseren van de klokboom! Maar CTS is een kritische fase, vooral voor veeleisende HPC-ontwerpen, omdat er zo weinig ruimte is voor afwijkingen om de gewenste prestaties te bereiken en zo aan de PPA-eisen te voldoen.

Aprisa is door de beste gieterijen gecertificeerd voor de meest geavanceerde knooppunten. Het zorgt ervoor dat alle PPA-statistieken zorgvuldig uitgebalanceerd zijn voor de implementatie van HPC-ontwerp door middel van hoogwaardige klokbomen. Om nog maar te zwijgen van plaatsings- en routeringstechnologieën die de wrijving tussen het blok en het bovenste niveau tijdens de montage verminderen.

Opnieuw kan de whitepaper worden gedownload hier.

Lees ook:

AI voor het ontwerp van aangepaste, analoge gemengd-signaal-IC's

Optimalisatie van fysieke verificatiestromen van Shift-Left met Calibre

Het verminderen van de complexiteit van het ontwerpen van elektronische systemen met AI

Deel dit bericht via:

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiwiki.com/eda/siemens-eda/336466-placement-and-clocks-for-hpc/